����̎���g�ӵĴ�h(hu��n)���У��댧�w�OӋ��Ҫ������Ѹ�٣�����(ji��)���Լ�����(w��n)�������˝M���@һ���댧�w������I(y��)��Ҫ����ͻ�Ƽ��g��(chu��ng)�¡�ͨ�^��������������Ӱ푵ķ������͑����܌��F�^�F���OӋ��������(y��u)��� PPA Ŀ�ˡ����磬ȫ���~��ֵ��ȫ�ֵ�ԣ�ȕ�������ܺ��ĵ��@�����M��

���ˑ����������(zh��n)��Cadence ���m(x��)��(chu��ng)�²��_�l(f��)�� Cadence Tempus �OӋ��(w��n)���Է�����DRA�������ṩ��Q�������}����Ҫ�ķ���������ԓ���������M�Ľ�ģ�㷨���x�ܹ��̎��������R�e���m����׃���O�����е��P�I�OӋҪ�أ������m����ģ�K���� Tempus ECO Options ����ϵ�y(t��ng)/ȫоƬ���� Cadence Certus �Ք���Q���������߽Կ��� Innovus �OӋ���Fϵ�y(t��ng)���{�á�ͨ�^��ְl(f��)�]���ĸ��������ԣ��͑����ԏ����OӋ��(w��n)���ԣ���(y��u)�����ġ����ܺ���e��PPA��Ŀ�ˣ��^���y(t��ng)����ԣ�ȵķ������F����_ 10% �� PPA Ŀ��������

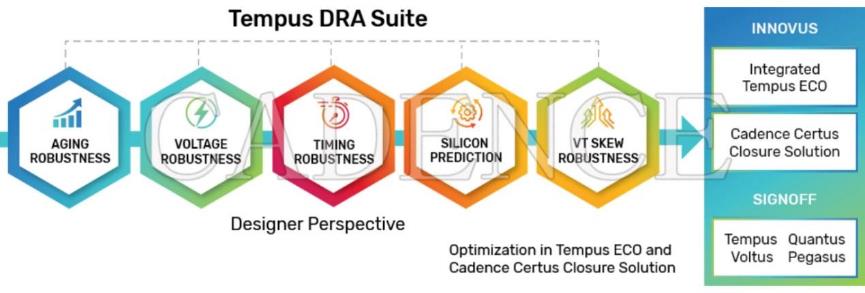

Tempus DRA ��

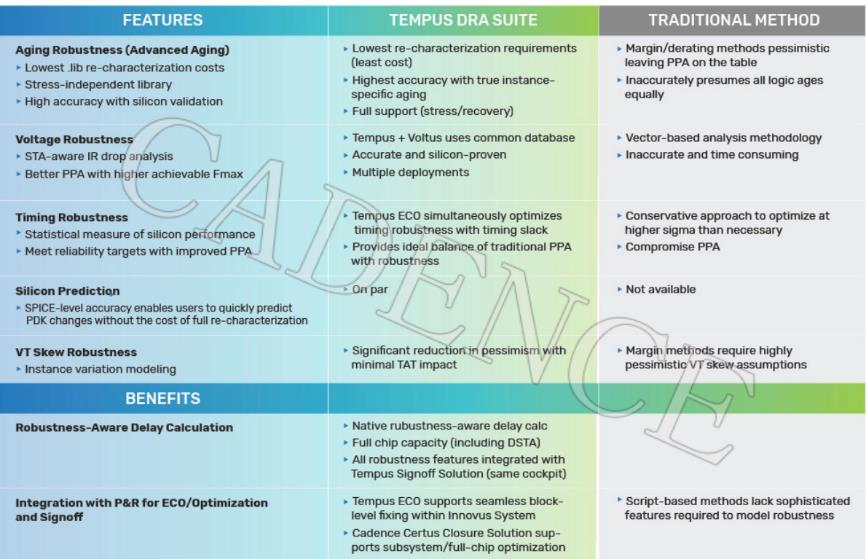

Tempus DRA ��������Խ�ķ���������ᘌ��ϻ�Ч����늉������ֵ늉�ƫб�Ȳ�ͬ��͵ĕr��ƫ���Q�OӋ�ӵķ�(w��n)���Ԇ��}��ԓ������ 5 �N�������������քe�m���ڷ�(w��n)���댧�w�OӋ���ض����̡�

1.�ϻ���(w��n)����

Tempus DRA ������Խ���ϻ���(w��n)���Է��������ژI(y��)�窚��һ�ã�PPA Ŀ����߿���� 10%���m������܇�����պ��졢���M����ӡ��Ƅ��O��ʹ�Ҏ(gu��)ģӋ����I��ԓ�����S���̎��� Cadence Liberate Library ���������̹��߃ȿ����ϻ������h(hu��n)�����������ṩ�ϻ��h(hu��n)�������������Y������ͨ�^�y(t��ng)Ӌ�W�D��ֱ�^�ʬF�����ͻ֏͠�B(t��i)��

�c�ϻ���֪�r������ƽY�ϣ��ϻ���(w��n)���Կ��Ԍ��F SPICE �����ȵ�Խ PPA �Y�������_�e� TMI ������ SPICE �ɿ���ģ�͵�֧���£����Ը�ۙ��������µ��o�B(t��i)�r�������STA���������ϻ����ǽy(t��ng)һ�ϻ����֏�ģ���x�������{��(ji��) STA ���(y��u)�O�á������ڴˣ��ϻ�Ч�����µķDZ�Ҫ���t��������Mһ�������OӋ�Ք���

2.늉���(w��n)����

늉���(w��n)���Է����c Tempus �Դ�����ԣ�PI���� Voltus IC�Դ�����Խ�Q�����o�p���ɣ���������ˬF�еĺ��˽�Q������ԓ���ɲ�������һ����IR�������������ޏͼ��g��늉���(w��n)���Է���ͨ�^ Tempus ECO Option ���F�ޏ����̵��Ԅӻ�����ͨ�^��(y��u)�� Victim �� Aggressor ��̖·����Q�������}��ֵ��ע����ǣ�ԓ���������R�e���y(t��ng) IR �������˷��������Եĕr���`������ֹ���܌��¸߰��ɱ���ƬʧЧ�İl(f��)������� IR �����OӋԣ�ȵĽ���Ҳ���Ԏ������F����(y��u)�� PPA Ŀ�ˡ�

3.�r��(w��n)����

�r��(w��n)���Է����� Tempus DRA ���ĵ���헷����������@헏������������ͨ�^����Ƭ���ܵĽy(t��ng)Ӌ�W�y�����_���r��Ĝʴ_�ԣ��ڷ��� Sigma �ɿ���Ҫ���ͬ�r�@������OӋ PPA�����Ñ��ѺõĽ�����Լ����OӋ�ֲ����ģ�ECO�����̣��ṩ���^�ڂ��y(t��ng) SPICE ���ؿ��������ֱ���ˮ��ķ�����

4.���A�y

���A�y�� Tempus DRA ���ĵ���헷�����������ע�ڹ�Ƭ���Եij��m(x��)�{��(y��u)�����Ԍ���Ƭ���O��ģ�͡����Ŀ���O��ģ���ṩ���ٷ����������OӋ���̎����OӋ�M�п����{�������A�y֧�ְ��� PBA�������OӋ�������ͷ�������GBA��ȫ�֘����c���������OӋ�ĸ����A�Σ����� Tempus �r���Q������Tempus ECO Option �� Innovus �OӋ���Fϵ�y(t��ng)�п��á�

�OӋ���̎������ù��A�y���ܽ���ģ���cӲ�������P�ԣ��@������Ĺ�Ƭ���ܣ����� Tempus �r��� Liberate �������������g���F���ʵĽy(t��ng)Ӌ�W��ģ���ڹ�ǰ�o�B(t��i)�r�������STA�����˕r�R�e�xɢ������ԓ�������������x���OӋ�Fꠣ������_�ɴ_菵��Ք��̓�(y��u)�������ù��A�y�A�����t������� PPA �����ʡ�

5.늉��ֵƫб��(w��n)����

늉��ֵ��VT��ƫб��(w��n)������ Tempus DRA ���ĵ���헷������������ڑ���Ŀǰ STA �������еĕr���^��Tempus DRA ���������̎����`���ķ��� TT���ضȺ�늉���corners����ÿ�� VT ��͈�(zh��)�п��ٽ��~�Ԍ����t��(y��u)������ corners �Ϳ� corners��SSG �� FFG�����OӋ�����Ԍ����c VT �����������ÿ�� VT ��Ͷ��x���Ϳ콵�~��Tempus DRA �����Ԉ�(zh��)�Ѓ�(y��u)�����У������� VT ��͵Ć��ӺͲ�·���ҳ������ɳ�׃����

Tempus DRA ����һ�����������������ϼ��������������OӋ�ӷ�(w��n)���ԣ����Ȃ��y(t��ng)�������F��Խ�� PPA �������������䌦�ϻ���(w��n)���ԣ�늉���(w��n)���ԣ��r��(w��n)���ԣ����A�y�� VT ƫб��(w��n)���ԵČ�ע��ԓ�����������OӋ�F��ڿ��ٵ����ļ��g�h(hu��n)����(chu��ng)������Ч���ɿ������и������İ댧�w��Q�������@�nj��F��һ���댧�w�OӋ���P�Iһ����

Tempus DRA ���ǏV�� Cadence �����c���˹������̵ĽM�ɲ��֣�֧�� Cadence ����ϵ�y(t��ng)�OӋ��(zh��n)�ԣ����팍�FԽ��Ƭ��ϵ�y(t��ng)��SoC���OӋ���˽���� Tempus �r���Q�����ĸ��������ԡ�

���ߣ�Reela�����ķ��g�D�d�� Cadence blog��