51單片機(jī)的結(jié)構(gòu)

一、MCS-51 的核心電路

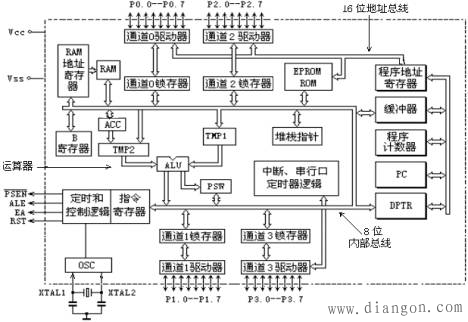

單片機(jī) 8051 內(nèi)部結(jié)構(gòu)框圖

一個(gè)8位CPU;

一個(gè)片內(nèi)振蕩器和時(shí)鐘電路;

4K字節(jié)片內(nèi)部程序存儲(chǔ)器ROM ;

128字節(jié)片內(nèi)部數(shù)據(jù)存儲(chǔ)器RAM ;

可尋址64K外部程序存儲(chǔ)器;

可尋址64K外部數(shù)據(jù)存儲(chǔ)器;

21個(gè)特殊功能寄存器 (專(zhuān)用寄存) ;

32條可編程的 I/O 線(4個(gè)8 位并行I/O端口);

兩個(gè)16位定時(shí)器/計(jì)數(shù)器;

一個(gè)可編程全雙工串行口;

具有5個(gè)中斷源,兩個(gè)優(yōu)先級(jí)嵌套中斷結(jié)構(gòu)。

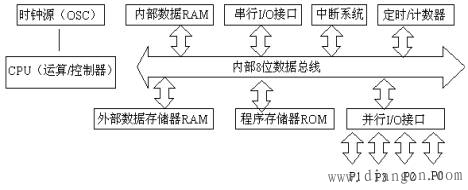

單片機(jī)各功能部件由內(nèi)部總線聯(lián)系在一起。簡(jiǎn)化結(jié)構(gòu)如下圖所示

MCS-51 單片機(jī)結(jié)構(gòu)框圖

二、中央處理單元CPU

CPU 是單片機(jī)的核心部件,如上圖所示,各方框表示功能部件,可以看出本單片機(jī)是 8 位數(shù)據(jù)寬度的處理器,能處理 8 位二進(jìn)制數(shù)據(jù)或代碼, CPU 負(fù)責(zé)控制、指揮和調(diào)度整個(gè)單元系統(tǒng)協(xié)調(diào)的工作,完成各種運(yùn)算,實(shí)現(xiàn)對(duì)單片機(jī)各功能部件的指揮和控制任務(wù),它是由運(yùn)算器和控制器等部件組成的。各功能部件實(shí)際上是 CPU 的有機(jī)組成部分,各功能部件通過(guò)運(yùn)行程序相聯(lián)系

(1)運(yùn)算器

運(yùn)算器的功能是進(jìn)行算術(shù)運(yùn)算和邏輯運(yùn)算,它還包含一個(gè)布爾處理器,用來(lái)處理位的操作。運(yùn)算器模塊包括算術(shù)和邏輯運(yùn)算部件 ALU、布爾處理器,累加器 ACC、 B 寄存器、暫存器 TMP1 和 TMP2、程序狀態(tài)字寄存器 PSW 和十進(jìn)制數(shù)調(diào)整電路等。

1、累加器 ACC 是一個(gè)最常用的專(zhuān)用寄存器。大部分單操作數(shù)據(jù)指令的操作數(shù)取自累加器。很多雙操作數(shù)指令中的一個(gè)操作數(shù)也取自累加器。加、減、乘、除算術(shù)運(yùn)算指令的運(yùn)算結(jié)果都存放在累加器 A 或 AB 寄存器對(duì)中。指令系統(tǒng)中用 A 作為累加器的助記符。

2、B 寄存器

3、程序狀態(tài)字 PSW

程序狀態(tài)字記錄程序狀態(tài)信息,反映程序運(yùn)算結(jié)果的特征,它是一個(gè) 8 位寄存器。其中 PSW 的 1 位未用,格式如下:(按 D7 ~ D0 順序排列)

Cy | Ac | F0 | RS | RS | OV | - | P |

① Cy (PSW.7) — 進(jìn)位標(biāo)志。在執(zhí)行某些算術(shù)和邏輯指令時(shí),當(dāng)運(yùn)算結(jié)果的最高位有進(jìn)位或借位時(shí), Cy 將被硬件置位,否則就被清零。不同的是在布爾處理機(jī)中,它被認(rèn)為是位累加器,可由軟件置位或清零。

② AC (PSW.6) — 輔助進(jìn)位標(biāo)志。在進(jìn)行加法或減法操作中,當(dāng)?shù)?4 位數(shù)向高 4 位數(shù)有進(jìn)位或借位時(shí), AC 將被硬件置位,否則就被清零。 AC 被用于十進(jìn)制調(diào)整。

③ FO (PSW.5) — 用戶(hù)定義標(biāo)志。可由用戶(hù)讓其記錄程序狀態(tài),用作標(biāo)記,即用軟件使其置位或復(fù)位。

④ RS1、RS0(PSW.4,PSW.3) — 工作寄存器組選擇控制位。可以用軟件置位或清零,以確定當(dāng)前工作寄存器組。

⑤ OV(PSW.2 —溢出標(biāo)志位。在對(duì)有符號(hào)數(shù)作加減運(yùn)算時(shí),用 C6 表示 D6 位向 D7 位的進(jìn)位或借位,用C7表示D7位向更高位的進(jìn)位或借位,則 OV 標(biāo)志可由下式求得: OV=C6 ⊕ C7。 OV=1 表示加減運(yùn)算的結(jié)果超出了目的寄存器 A 所能表示的帶符號(hào)數(shù)的范圍(-128 ~ +127)。

無(wú)符號(hào)數(shù)乘法指令 MUL 的執(zhí)行結(jié)果也會(huì)影響溢出標(biāo)志。若置于累加器 A 和寄存器 B 的兩個(gè)數(shù)的乘積超過(guò) 255 時(shí)(8位數(shù)), OV=1 ,否則 OV=0 。此積的高 8 位放在 B 內(nèi),低 8 位放在 A 內(nèi)。因此, OV=0 時(shí),只要從 A 中取得乘積即可,否則還要從 B 中取得乘積的高 8 位。

除法指令 DIV 也會(huì)影響溢出標(biāo)志,當(dāng)除數(shù)為 0 時(shí), OV=1 ,否則 OV=0 。

⑥ (PSW.0) — 奇偶標(biāo)志。每個(gè)指令周期都由硬件來(lái)置位或清零,以表示累加器 A 中有 1 的位數(shù)的奇偶數(shù)。若 1 的位數(shù)為奇數(shù),則 P 置位,否則清零。該標(biāo)志位對(duì)串行通信中的數(shù)據(jù)傳輸有重要意義。和數(shù)學(xué)中的數(shù)據(jù)本身的奇偶性有區(qū)別。當(dāng) A=10101000B 時(shí),因數(shù)中是三個(gè) 1 使 P 置位。在數(shù)據(jù)傳輸時(shí),當(dāng)把一批數(shù)的 P 位和原 8 位放在一起構(gòu)成 9 位數(shù),這批 9 位數(shù)中 1 的個(gè)數(shù)應(yīng)全為偶數(shù)。接收端如收到的數(shù)沒(méi)有偶數(shù)個(gè) 1 則認(rèn)為出錯(cuò)。

(2)控制器

控制器部件是由指令寄存器、程序計(jì)數(shù)器 PC ,定時(shí)與控制電路等組成的。

① 指令寄存器和譯碼

指令寄存器中存放指令代碼。

② 程序計(jì)數(shù)器 PC

程序計(jì)數(shù)器 PC 用來(lái)存放即將要執(zhí)行的指令地址,共 16 位,可對(duì) 64K 程序存儲(chǔ)器直接尋址。

③ 定時(shí)與控制電路

定時(shí)與控制電路是產(chǎn)生 CPU 操作時(shí)序的,它是單片機(jī)的心臟。控制各種操作的時(shí)間。

8051 芯片內(nèi)部有一個(gè)反向放大器所構(gòu)成的振蕩電路, XTAL1 和 XTAL2 分別為振蕩電路的輸入端和輸出端。放大器可以產(chǎn)生自激振蕩,此時(shí)時(shí)鐘由內(nèi)部方式產(chǎn)生。當(dāng) XTAL1 接地, XTAL2 接外部振蕩器時(shí),時(shí)鐘由外部方式產(chǎn)生。

三、8051 內(nèi)部 ROM 存儲(chǔ)器

ROM: Read Only Memory

一般用于存放程序和表格等不常改變的數(shù)據(jù)

8051單片機(jī)的 ROM 是掩摸 ROM

容 量:4096byte(212)

地址范圍:0000H ~ 1FFFH

四、8051 內(nèi)部的 RAM 存儲(chǔ)器

RAM : Random Access Memory

一般用于存放程序執(zhí)行過(guò)程中產(chǎn)生的大量的臨時(shí)數(shù)據(jù),相當(dāng)于 PC 的內(nèi)存。

8051 單片機(jī)的內(nèi)部 RAM :

容 量: 128 字節(jié)

地址范圍: 00H~7FH

編輯:admin 最后修改時(shí)間:2018-05-08