��Ƭ�C(j��)��ַ�g�a�·

��̎����ϵ�y(t��ng)�У����еĴ惦������I/O�ӿڣ����Ե�ַ����^(q��)�֣�����(j��)�L���惦�������L��I/O�ӿڣ�ָ���еĵ�ַ��Ϣ�����ַ�g�a�·�a(ch��n)������(y��ng)�ĵ�ַ�x����̖�����x������Ĵ惦������I/O�ӿڣ����Դ惦���Ľӿڞ���������һ���8λ̎��������惦���ĵ�ַ����16�l��A0~A15������ַ������64K������һ�����Hϵ�y(t��ng)�в�һ���U(ku��)չ64K���A�����������U(ku��)չ�Ĵ��A��Ҳ����һƬ������64K�Ĵ惦�����������ϵ�y(t��ng)ͨ��Ҫ��U(ku��)չ��Ƭ���A���·��ÿ�N�惦��оƬ������(j��)��������Ҫһ���ĵ�ַ��̖����2K�惦������ĵ�ַ��̖��A0~A10��8K�惦������ĵ�ַ��̖��A0~A12�����ϵ�y(t��ng)���B�Ӵ惦���r��������A��оƬ�ṩ��횵ĵ�ַ��̖�⣬߀��(y��ng)�ṩƬ�x��̖��ʹ���е�һ��оƬ��Ƭ�x��̖��Ч�r��������ַ�g�a�·�����ṩƬ�x��̖���·������һ��ϵ�y(t��ng)��Ҫ�B��2Ƭ2K���A�������ϵ�y(t��ng)�����惦���ṩA10~A0�ĵ�ַ��̖�����x�� 2K���A���е�ijһ����Ԫ�����˅^(q��)�e�@�ɂ��惦��оƬ����һ�����x�У���(y��ng)����Ƭ�x��̖������̖���g�a�·�a(ch��n)����

I/O�ӿ�����ĵ�ַ�g�a�·��ԭ���c�惦�����ƣ���ͬ���ǣ�ͨ��I/O�ӿ�ֻ��һ����ַ����ׂ���ַ��������惦��һ��оƬ��ռ���^��ĵ�ַ����ˌ���I/O�ӿڵ��g�a�·����횸���(j��)ԓ�O(sh��)��ռ�õĵ�ַ�Ĕ�(sh��)�������w���]��

��ַ�g�aͨ������ȫ�g�a�·�������g�a�·�����x�·�Ȳ�ͬ�ķ�ʽ��

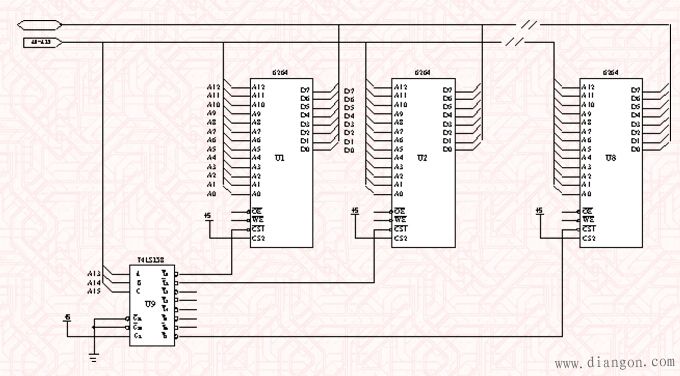

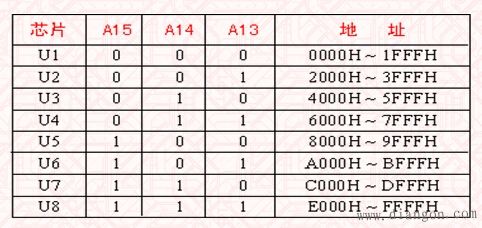

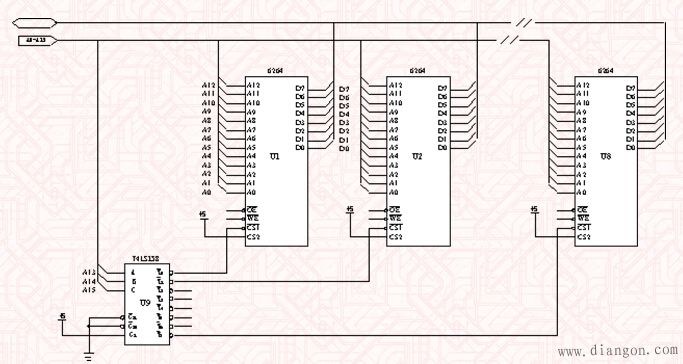

��ϵ�y(t��ng)�У��惦����I/O�ӿ���ʹ�ò��ֵ�ַ��̖���@Щ��̖ͨ�����ַ��̖�еĵ�λ��ַ��̖��ȫ�g�a�·���������еĸ�λ��ַ��̖��(j��ng)�g�a����Ƭ�x��̖����ȫ�g�a�·��ϵ�y(t��ng)�У����е�ַ��̖��������惦����I/O�ӿ�оƬ�������������g�a�·���g�a�·��ݔ�������x����̖���cΨһ�Ĵ惦����I/O�ӿڵĵ�ַ����(y��ng)����ij����λ̎����������I/O�ӿچΪ���ַ�ķ�ʽ�����x��惦���ĵ�ַ����16�l��A0~A15�����x��I/O�ӿڵĵ�ַ����8�l��A0~A7�����t����ȫ�g�a�·�r���x��惦���ĵ�ַ�g�a�·��횰���A0~A15�ĵ�ַ��̖�б��惦��оƬ���õĵ�ַ֮������е�ַ��̖�����x��I/O�ӿڵĵ�ַ�g�a�·��횰���A0~A7�ĵ�ַ��̖�б�I/O�ӿ����õĵ�ַ֮������е�ַ��̖���D1�鳣�õ��g�a�·74LS138��74LS13������(j��)�惦�����������惦������ĵ�ַ��̖��ͬ������ڲ��ò�ͬ�惦���rȫ�g�a�·��ݔ���ַ��̖��ͬ���D2�����8K�惦����ȫ�g�a�·�������g�a�·�ĵ�ַ��̖��A13~A15�����ַ��������1��ʾ���ĵ�ַ������п��Կ���������ȫ�g�a�����r�����A��оƬ֮�g�ĵ�ַ���B�m(x��)�ģ�����������Ч������ 64K���A���g��

��

��

��a�� 74LS138 ������b�� 74LS139

�D1 �g�a����߉��̖

�D2 ȫ�g�a�·�U(ku��)չ8K�Ĵ惦��

��1 �U(ku��)չ8K�惦���ĵ�ַ����

������(d��ng)ϵ�y(t��ng)��U(ku��)չ�Ĵ惦����I/O�ӿڵĔ�(sh��)���^�ٕr���ɲ��ò����g�a�·���cȫ�g�a�·��ͬ���Dz����g�a�·���惦����I/O�ӿ����õĵ�λ��ַ����ĸ�λ��ַ���еIJ��ֵ�ַ��̖�����g�a�·��ݔ����̖�������@�N�����ă�(y��u)�c�ǜp�����g�a�·��ݔ����̖�����g�a��ݔ���c��ַ����һһ����(y��ng)���P(gu��n)ϵ������δ�����g�a�ĵ�ַ��̖�����в�ͬ�ľ��a������g�a��ݔ�����x�в�ͬ�ĵ�ַ���D3�����2K�惦���IJ����g�a�·���惦�����õĵ�ַ��A0~A10������ȫ�g�a�·��ݔ�뵽�g�a������̖��A11~A15�����ڈD3�ЃH����A11~A13��A14��A15δ�����g�a���@��A15��A14���H�Ͽ��Դ���4�N��r����00��01��10��11���Ե�һ��оƬ��������(d��ng)�҂���A15��A14�����00�r������ָ�����Ե�ַ0000H~07FFH�x��ԓоƬ���������ָ���зքe���˵�ַ4000H~47FFH��8000H~87FFH��C000H~C7FFH�x�е�����ԓоƬ����һ����Ԫ���Îׂ���ַ���L����

�D3 �����g�a�·

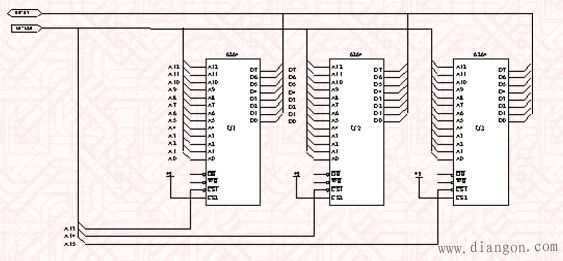

������(d��ng)ϵ�y(t��ng)��U(ku��)չ�Ĵ惦����I/O�ӿڵĔ�(sh��)���^�ٕr��߀�ɲ��þ��x�·���Դ惦���ĔU(ku��)չ��������ϵ�y(t��ng)�U(ku��)չ�Ğ�8K�Ĵ惦��оƬ���t��ַ��̖A0~A12��惦����ʹ�ã���ȫ�g�a�·�У��õ�ַ��̖A12~A15�����ַ�g�a��������D4��ʾ�ľ��x�·�У��@Щ��̖��ֱ������Ƭ�x��̖ʹ�á������@����ʹ�õĵ�ַ��ֻ��3�l��������ֻ���S�B��3Ƭ8K�Ĵ��A������24K�Ĵ惦��������ʹ���@�N�������ܳ������64K�Ĵ��A���g���������^С��ϵ�y(t��ng)��

�D4 ���x���g�a�·

������2�����þ��x�ķ����U(ku��)չ3Ƭ�惦���r��ַ�ķ�����r���ı��п��Կ������M���@�N�������^���Σ�����ʹ�õĵ�ַ�Dz��B�m(x��)�ģ�������ʹ�Õr��횷�ֹ�ɗl��ַ��ͬ�r����ƽ����t��ʹϵ�y(t��ng)ͬ�r�x�Ѓɂ��惦��оƬ���o������������

�� 2 ���x�·�惦���ĵ�ַ����

| оƬ | A15 | A14 | A13 | �� ַ |

| U3 | 1 | 1 | 0 | C000H ~ DFFFH |

| U4 | 1 | 0 | 1 | A000H ~ BFFFH |

| U5 | 0 | 1 | 1 | 6000H ~ 7FFFH |

����admin ����ĕr�g��2023-03-03