單片機(jī)微處理器的總線驅(qū)動

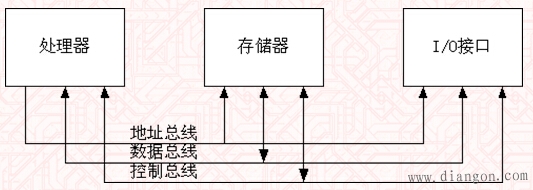

微處理器系統(tǒng)的基本結(jié)構(gòu)如圖1所示。

圖1 微處理器系統(tǒng)的基本結(jié)構(gòu)

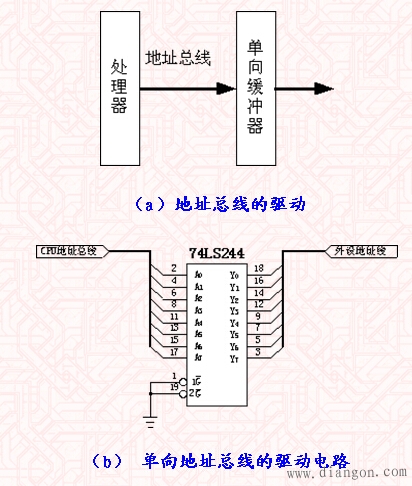

對于微處理器,地址信號是輸出信號,它的作用是選擇存儲器或I/O接口的地址。當(dāng)一個系統(tǒng)有較多的存儲器單元或I/O接口需要選擇時,需要地址信號提供較大的驅(qū)動能力,如所需的驅(qū)動能力大于微處理器的輸出能力時,應(yīng)對地址信號加驅(qū)動電路。地址總線的驅(qū)動如圖2(a)所示,常用的器件有圖2(b)所示的74LS244,它是一個單方向的緩沖器,能提供12 mA的電流驅(qū)動能力。其使能控制端為-G,當(dāng)-G= 0時,電路的輸出有效,當(dāng)-G=1時電路的輸出為高阻態(tài)。

圖2 地址總線的驅(qū)動與驅(qū)動電路

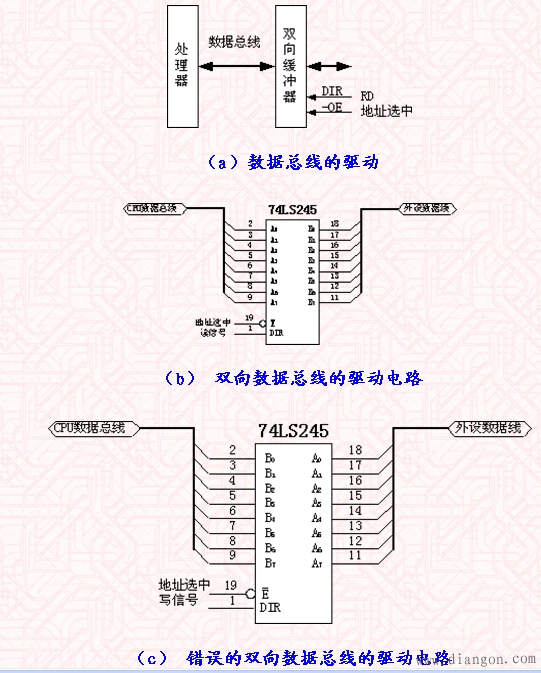

數(shù)據(jù)總線上傳送的是指令和數(shù)據(jù)。在微處理器讀取指令時,在數(shù)據(jù)總線上傳送的是指令信息,指令從存儲指令的存儲器讀出,送入微處理器進(jìn)行處理。對于微處理器,此時的數(shù)據(jù)總線是輸入信號。在讀取或輸出數(shù)據(jù)時,在數(shù)據(jù)總線上傳送的是數(shù)據(jù),這些數(shù)據(jù)將根據(jù)需要與存儲器或I/O接口交換。在讀取數(shù)據(jù)時,對于微處理器,此時的數(shù)據(jù)總線是輸入信號。在輸出數(shù)據(jù)時,對于微處理器,此時的數(shù)據(jù)總線是輸出信號。因此數(shù)據(jù)總線是雙向信號,根據(jù)讀寫控制信號,或讀指令控制信號能判斷其傳輸?shù)姆较颉?

很容易理解,當(dāng)微處理器連接較多的存儲器或I/O接口電路時,需要它提供較大的負(fù)載電流,因此需要提供總線驅(qū)動電路。但當(dāng)微處理器連接較少的存儲器或輸出接口電路,而這些電路與微處理器的距離較遠(yuǎn)時,將有較大的電容負(fù)載,此時同樣需要總線驅(qū)動電路。與地址總線的驅(qū)動電路不同的是,數(shù)據(jù)總線必須采用圖3(a)所示的雙向驅(qū)動電路,常用的器件有圖3(b)所示的74LS245,與74LS244不同的是,它不但具有使能控制信號,還需方向控制信號。其使能控制端為-E,當(dāng)-E= 0時,電路的輸出有效,當(dāng)-E=1時電路的輸出為高阻態(tài)。DIR端決定傳送方向,當(dāng) DIR=0時信號從B端流向A端,而當(dāng)DIR=1時信號從A端流向B端。方向控制信號必須在讀有效時起作用,當(dāng)此信號有效時將存儲器或I/O接口的數(shù)據(jù)送往微處理器。在寫信號有效時微處理器的數(shù)據(jù)送往存貯器或I/O接口。

圖3 數(shù)據(jù)總線的驅(qū)動與驅(qū)動電路

在使用雙向緩沖器74LS245時必須考慮使能端和方向端的連接方法,通常使能端應(yīng)在存儲器或I/O接口被選中時起作用,而方向端則由讀信號控制。在未選中存儲器或I/O接口時雙向緩沖器輸出為高阻態(tài),在選中存儲器或I/O接口時,如為讀信號有效,雙向緩沖器的輸出連接到數(shù)據(jù)總線上,將數(shù)據(jù)送往微處理器,而非讀信號時數(shù)據(jù)從微處理器送出。非讀信號有效包括了寫信號有效或時序的其他狀態(tài),采用讀信號作為方向控制端避免了時序在其他狀態(tài)時雙向緩沖器的輸出連接到數(shù)據(jù)總線上而造成數(shù)據(jù)總線的沖突。

如采用圖33(c)的方法,用寫信號作為控制端,在寫信號有效時數(shù)據(jù)從微處理器輸出,在讀有效及時序的其他狀態(tài)時雙向緩沖器的輸出連接到數(shù)據(jù)總線上,而后者將造成數(shù)據(jù)總線沖突。

使能端的另一個連接方法是直接接低電平,此時無論地址是否有效,在發(fā)出讀信號時都會將雙向緩沖器的輸出連接到數(shù)據(jù)總線上。這種方式適用于微處理器只連接一個總線驅(qū)動器的場合;如系統(tǒng)總線連接了多個總線驅(qū)動器,或連接一個總線驅(qū)動器,又直接連接了部分存儲器或I/O接口時,則會造成數(shù)據(jù)總線沖突。

微處理器的控制信號提供了微處理器正常工作所需的系統(tǒng)時鐘信號和復(fù)位信號。還提供了控制存儲器或I/O接口的信號,包括了讀寫控制,存儲器與I/O接口的區(qū)分,中斷信號的處理,直接數(shù)據(jù)通道的處理。在這些信號的作用下微處理器能將數(shù)據(jù)送入存儲器或輸出接口,或者從存儲器或輸入接口讀入數(shù)據(jù)。

編輯:admin 最后修改時間:2018-05-08