AT89S52ÎÆŹC(jš©)ČąĐĐI/O¶ËżÚ

ÎÆŹC(jš©)I/O¶ËżÚÊÇ”(shšŽ)ț(jšŽ)ĘÈëŸ_Ąą”(shšŽ)ț(jšŽ)Ęłöò(qš±)Ó(dš°ng)Œ°æiŽæ¶àí(xiš€ng)čŠÄÜI/Oë·ŁŹÊÇÎÆŹC(jš©)Š(dušŹ)ÍâČż(shšȘ)ŹF(xiš€n)żŰÖÆșÍĐĆÏąœ»Q”Ä±Űœ(jš©ng)֟·ĄŁAT89S52ÎÆŹC(jš©)I/O¶ËżÚÓĐŽźĐĐșÍČąĐĐÖź·ÖŁŹÓĐP0ĄąP1ĄąP2șÍP3ËÄ(gšš)8λȹĐĐI/O¶ËżÚŁŹčČŐŒ32žùÒęÄ_ŁŹĂżÒ»(gšš)I/O¶ËżÚ¶ŒÄÜȘ(dšČ)Áą”ŰÓĂŚśĘÈë»òĘłöŁ»ÓĐ1(gšš)ŽźĐĐI/O¶ËżÚŁŹÒ»ŽÎÖ»ÄÜśËÍһλ¶țßM(jšŹn)ÖÆĐĆÏąĄŁ

1ŁźČąĐĐI/O¶ËżÚ

P0żÚéÈęB(tš€i)ëpÏòżÚŁŹP1ĄąP2ĄąP3żÚéÊ(zhšłn)ëpÏòżÚĄŁ

Łš1Ł©P0¶ËżÚ

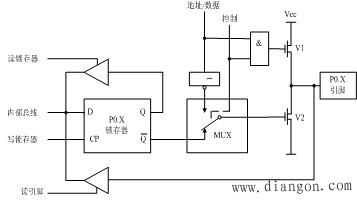

P0żÚŚÖč(jišŠ)”ŰÖ·80HŁŹÎ»”ŰÖ·80HĄ«87HĄŁP0żÚłęŚśéÊ(zhšłn)ëpÏòÍšÓĂIŁŻOœÓżÚÊčÓĂÍ⣏ßÓĐžüÖŰÒȘ”ÄÉ·NčŠÄÜŁș·Ör(shšȘ)Í(fšŽ)ÓĂé”ŰÖ·żŸ(xiš€n)șÍ”(shšŽ)ț(jšŽ)żŸ(xiš€n)ĄŁP0żÚĘłör(shšȘ)ÄÜò(qš±)Ó(dš°ng)8(gšš)LSTTLŰ(fšŽ)ĘdŁŹŒŽĘłöëÁśČ»ĐĄÓÚ800ŠÌAĄŁP0żÚλœY(jišŠ)(gš°u)ÈçD1ËùÊŸĄŁ

D1 P0żÚλœY(jišŠ)(gš°u) ź(dšĄng)P0żÚÓĂŚśĘłöżÚÊčÓĂr(shšȘ)ŁŹÔÚò(qš±)Ó(dš°ng)NMOSë·r(shšȘ)Ș(yš©ng)ÍâœÓÉÏÀëŚèŁ»ĘÈëČÙŚśÓĐŚxÒęÄ_șÍŚxæiŽæÆśÖź·ÖĄŁ

Łš2Ł©P1¶ËżÚ

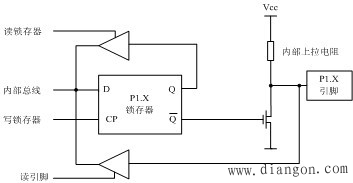

P1żÚŚÖč(jišŠ)”ŰÖ·90HŁŹÎ»”ŰÖ·90HĄ«97HĄŁP1żÚÖ»ÓĐŚśéÍšÓĂĘÈ룯ʳöœÓżÚ”ÄčŠÄÜĄŁP0żÚλœY(jišŠ)(gš°u)ÈçD2ËùÊŸĄŁ

D2 P1żÚλœY(jišŠ)(gš°u) AT89S52”ÄP1.0șÍP1.1ÊǶàčŠÄÜÒęÄ_ŁŹP1.0żÉŚś¶šr(shšȘ)Æś/Ó(jšŹ)”(shšŽ)Æś2”ÄÍâČżÓ(jšŹ)”(shšŽ)Ó|°l(fšĄ)ĘÈë¶ËT2ŁŹP1.1żÉŚś¶šr(shšȘ)Æś/Ó(jšŹ)”(shšŽ)Æś2”ÄÍâČżżŰÖÆĘÈë¶ËT2EXĄŁ

Łš3Ł©P2¶ËżÚ

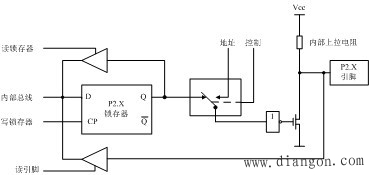

P2żÚŚÖč(jišŠ)”ŰÖ·A0HŁŹÎ»”ŰÖ·A0HĄ«A7HĄŁP2żÚÊÇÒ»(gšš)8λÊ(zhšłn)ëpÏòI/OżÚŁŹŸßÓĐÉ·NčŠÄÜĄŁÒ»ÊÇŚśÍšÓĂI/OżÚÓĂŁŹĆcP1żÚÏàÍŹĄŁ¶țÊÇŚśÏ”œy(tšŻng)U(kuš°)ŐčÍâČżŽæŠ(chšł)Æś”Äžß8λ”ŰÖ·żŸ(xiš€n)ŁŹĘłöžß8λ”ŰÖ·ŁŹĆcP0żÚÒ»ÆđœMłÉ16λ”ŰÖ·żŸ(xiš€n)ĄŁP2żÚλœY(jišŠ)(gš°u)ÈçD3ËùÊŸŁŹ

D3 P2żÚλœY(jišŠ)(gš°u) Łš4Ł©P3¶ËżÚ

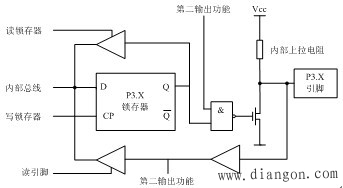

P3żÚŚÖč(jišŠ)”ŰÖ·B0HŁŹÎ»”ŰÖ·B0HĄ«B7HĄŁP3żÚÒČÊÇÒ»(gšš)8λÊ(zhšłn)ëpÏòI/OżÚŁŹŒÈżÉÒÔŚÖč(jišŠ)ČÙŚśŁŹÒČżÉÒÔλČÙŚśŁ»ŒÈżÉÒÔ8λżÚČÙŚśŁŹÒČżÉÒÔÖđλ¶šÁxżÚŸ(xiš€n)éĘÈëŸ(xiš€n)»òĘłöŸ(xiš€n)Ł»ŒÈżÉÒÔŚxÒęÄ_ŁŹÒČżÉÒÔŚxæiŽæÆśŁŹ(shšȘ)ŹF(xiš€n)Ą°ŚxÒ»ĐȚžÄÒ»ĘłöĄ±ČÙŚśĄŁP3żÚ”ÄλœY(jišŠ)(gš°u)ÈçD4ĄŁ

D4 P3żÚλœY(jišŠ)(gš°u)

P3żÚłęŸßÓĐĆcP1żÚÍŹÓ”ÄčŠÄÜÍâŁŹßŸßÓДڶțčŠÄÜŁŹÈç±í1ËùÊŸ

±í1 P3żÚ”ĔڶțčŠÄÜ 2ŁźŽźĐĐI/O¶ËżÚ

AT89S52ÓĐÒ»(gšš)È«ëpč€”ÄżÉŸłÌŽźĐĐI/O¶ËżÚĄŁß@(gšš)ŽźĐĐI/O¶ËżÚŒÈżÉÒÔÔÚłÌĐòżŰÖÆÏÂąCPU”Ä8λȹĐĐ”(shšŽ)ț(jšŽ)ŚłÉŽźĐĐ”(shšŽ)ț(jšŽ)һλһλ”ŰÄ°l(fšĄ)ËÍ”(shšŽ)ț(jšŽ)Ÿ(xiš€n)TXD°l(fšĄ)ËÍłöÈ„ŁŹÒČżÉÒÔ°ŃŽźĐĐœÓÊŐ”œ”Ä”(shšŽ)ț(jšŽ)ŚłÉ°ËλȹĐĐ”(shšŽ)ț(jšŽ)ËÍœoCPUŁŹ¶űÇÒß@·NŽźĐĐ°l(fšĄ)ËÍșÍŽźĐĐœÓÊŐżÉÒÔÎȘ(dšČ)ßM(jšŹn)ĐĐŁŹÒČżÉÒÔÍŹr(shšȘ)ßM(jšŹn)ĐĐĄŁ

AT89S52ŽźĐĐ°l(fšĄ)ËÍșÍŽźĐĐœÓÊŐÀûÓĂÁËP3żÚ”ĔڶțčŠÄÜŁŹŒŽÀûÓĂP3.1 ÒęÄ_ŚśéŽźĐĐ”(shšŽ)ț(jšŽ)”Ä°l(fšĄ)ËÍŸ(xiš€n)TXDșÍP3.0ÒęÄ_ŚśéŽźĐĐ”(shšŽ)ț(jšŽ)”ÄœÓÊŐŸ(xiš€n)RXDĄŁ

ŸĘŁșadmin ŚîșóĐȚžÄr(shšȘ)égŁș2018-05-08