��Ƭ�C(j��)SPI�����r��Ԕ��

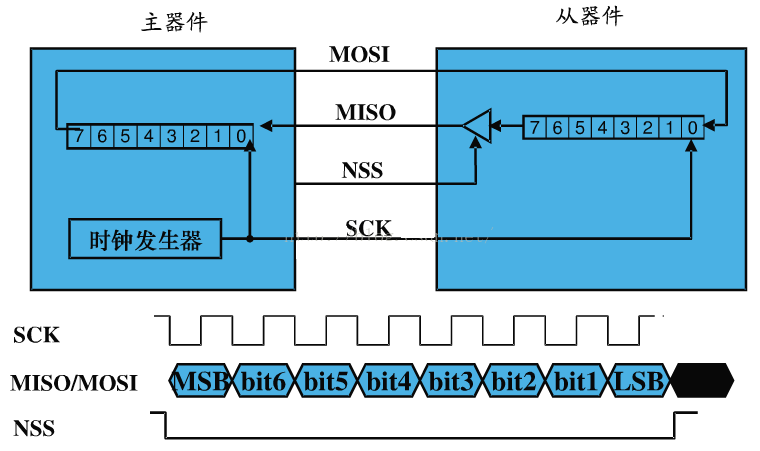

SPI������Motorola��˾�Ƴ�������ͬ���ӿڣ�ͬ������3����ʽ�M(j��n)��ͨ��:һ�l�r犾�SCK��һ�l��(sh��)��(j��)ݔ�뾀MOSI��һ�l��(sh��)��(j��)ݔ����MISO;���� CPU�c���N��������M(j��n)��ȫ�p����ͬ������ͨӍ��SPI��Ҫ���c(di��n)��:����ͬ�r�l(f��)���ͽ��մ��Д�(sh��)��(j��);���Ԯ�(d��ng)�����C(j��)��ęC(j��)����;�ṩ�l�ʿɾ��̕r�;�l(f��)�ͽY(ji��)���Д���(bi��o)־;���_ͻ���o(h��);�����������o(h��)�ȡ�

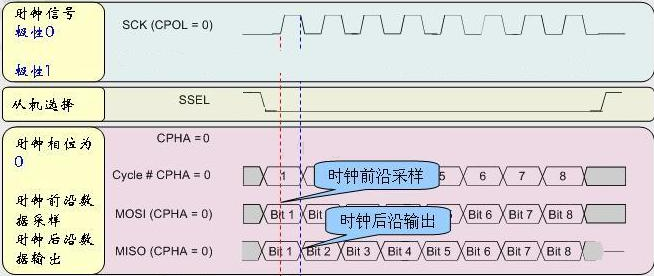

SPI�������ķN������ʽ(SP0, SP1, SP2, SP3)������ʹ�õ����V������SPI0��SPI3��ʽ��SPIģ�K���˺����O(sh��)�M(j��n)�Д�(sh��)��(j��)���Q������(j��)���O(sh��)����Ҫ����ݔ������ͬ���r犘O�Ժ���λ�����M(j��n)�����ã��r犘O��(CPOL)����ݔ�f(xi��)�h�]���ش��Ӱ푡����CPOL=0������ͬ���r犵Ŀ��e��B(t��i)����ƽ;���CPOL=1������ͬ���r犵Ŀ��e��B(t��i)����ƽ���r���λ(CPHA)�܉����������x��ɷN��ͬ�Ă�ݔ�f(xi��)�h֮һ�M(j��n)�Д�(sh��)��(j��)��ݔ����� CPHA=0���ڴ���ͬ���r犵ĵ�һ����׃��(�������½�)��(sh��)��(j��)���ɘ�;���CPHA=1���ڴ���ͬ���r犵ĵڶ�����׃��(�������½�)��(sh��)��(j��)���ɘӡ�

SPI��ģ�K���c֮ͨ�ŵ����O(sh��)���r���λ�͘O�ԑ�(y��ng)ԓһ�¡�

SPI�r��Ԕ��---SPI�ӿ���ģʽ0��ݔ����һλ��(sh��)��(j��)�ĕr��SPI�ӿ����ķN��ͬ�Ĕ�(sh��)��(j��)��ݔ�r��ȡ�Q��CPOL��CPHL�@��λ�ĽM�ϡ��D1�б��F(xi��n)���@�ķN�r�r���cCPOL��CPHL���P(gu��n)ϵҲ���ԏĈD�п�����

�D1

CPOL���Á�Q��SCK�r���̖���e�r���ƽ��CPOL=0�����e�ƽ����ƽ��CPOL=1�r�����e�ƽ����ƽ��CPHA���Á�Q���ɘӕr�̵ģ�CPHA=0����ÿ�����ڵĵ�һ���r��زɘӣ�CPHA=1����ÿ�����ڵĵڶ����r��زɘӡ�������ʹ�õ�����������ģʽ0�@�N�r��(CPOL=0��CPHA=0)�����Ԍ��D1������D2��ֻ�P(gu��n)עģʽ0�ĕr��

�D2

�҂����P(gu��n)עSCK�ĵ�һ���r����ڣ��ڕr犵�ǰ�زɘӔ�(sh��)��(j��)(�����أ���һ���r���)���ڕr犵ĺ���ݔ����(sh��)��(j��)(�½��أ��ڶ����r���)�����ȁ�������������������ݔ����(MOSI)ݔ���Ĕ�(sh��)��(j��)bit1���ڕr犵�ǰ�ر��������ɘӣ������������ںΕr��ݔ��bit1����?bit1��ݔ���r�̌�(sh��)�H����SCK��̖��Ч��ǰ����SCK��������߀Ҫ��낀�r����ڡ�bit1��ݔ���r���cSSEL��̖�]���P(gu��n)ϵ���ف�������������������ݔ���MISOͬ�����ڕr犵�ǰ�زɘӏ�����ݔ����bit1�ģ��Ǐ����������ںΕr��ݔ��bit1���ء�����������SSEL��̖��Ч������ݔ��bit1���M�ܴ˕rSCK��̖߀�]����Ч��

���@���D�Ϳ��Ժ�����Ŀ�������������bit1������ݔ����

����admin ����ĕr�g��2018-05-25