圖文教你理解單片機(jī)STM32時(shí)鐘

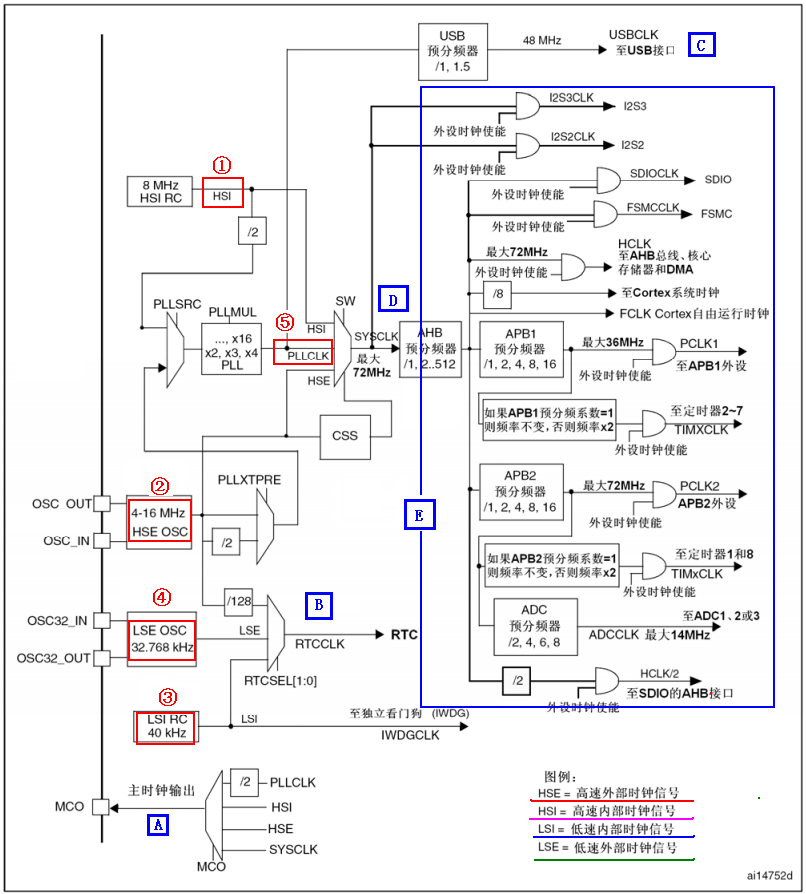

眾所周知STM32有5個(gè)時(shí)鐘源HSI、HSE、LSI、LSE、PLL,其實(shí)他只有四個(gè),因?yàn)閺纳蠄D中可以看到PLL都是由HSI或HSE提供的。

其中,高速時(shí)鐘(HSE和HSI)提供給芯片主體的主時(shí)鐘.低速時(shí)鐘(LSE和LSI)只是提供給芯片中的RTC(實(shí)時(shí)時(shí)鐘)及獨(dú)立看門狗使用,圖中可以看出高速時(shí)鐘也可以提供給RTC。內(nèi)部時(shí)鐘是在芯片內(nèi)部RC振蕩器產(chǎn)生的,起振較快,所以時(shí)鐘在芯片剛上電的時(shí)候,默認(rèn)使用內(nèi)部高速時(shí)鐘。而外部時(shí)鐘信號是由外部的晶振輸入的,在精度和穩(wěn)定性上都有很大優(yōu)勢,所以上電之后我們再通過軟件配置,轉(zhuǎn)而采用外部時(shí)鐘信號.

高速外部時(shí)鐘(HSE):以外部晶振作時(shí)鐘源,晶振頻率可取范圍為4~16MHz,我們一般采用8MHz的晶振。

高速內(nèi)部時(shí)鐘(HSI): 由內(nèi)部RC振蕩器產(chǎn)生,頻率為8MHz,但不穩(wěn)定。

低速外部時(shí)鐘(LSE):以外部晶振作時(shí)鐘源,主要提供給實(shí)時(shí)時(shí)鐘模塊,所以一般采用32.768KHz。

低速內(nèi)部時(shí)鐘(LSI):由內(nèi)部RC振蕩器產(chǎn)生,也主要提供給實(shí)時(shí)時(shí)鐘模塊,頻率大約為40KHz。

OSC_OUT和OSC_IN開始,這兩個(gè)引腳分別接到外部晶振8MHz,第一個(gè)分頻器PLLXTPRE,遇到開關(guān)PLLSRC(PLL entry clock source),我們可以選擇其輸出,輸出為外部高速時(shí)鐘(HSE)或是內(nèi)部高速時(shí)鐘(HSI)。這里選擇輸出為HSE,接著遇到鎖相環(huán)PLL,具有倍頻作用,在這里我們可以輸入倍頻因子PLLMUL,要是想超頻,就得在這個(gè)寄存器上做手腳啦。經(jīng)過PLL的時(shí)鐘稱為PLLCLK。倍頻因子我們設(shè)定為9倍頻,也就是說,經(jīng)過PLL之后,我們的時(shí)鐘從原來8MHz的 HSE變?yōu)?2MHz的PLLCLK。緊接著又遇到了一個(gè)開關(guān)SW,經(jīng)過這個(gè)開關(guān)之后就是STM32的系統(tǒng)時(shí)鐘(SYSCLK)了。通過這個(gè)開關(guān),可以切換SYSCLK的時(shí)鐘源,可以

選擇為HSI、PLLCLK、HSE。我們選擇為PLLCLK時(shí)鐘,所以SYSCLK就為72MHz了。PLLCLK在輸入到SW前,還流向了USB預(yù)分頻器,這個(gè)分頻器輸出為USB外設(shè)的時(shí)鐘(USBCLK)。回到SYSCLK,SYSCLK經(jīng)過AHB預(yù)分頻器,分頻后再輸入到其它外設(shè)。如輸出到稱為HCLK、FCLK的時(shí)鐘,還直接輸出到SDIO外設(shè)的

SDIOCLK時(shí)鐘、存儲器控制器FSMC的FSMCCLK時(shí)鐘,和作為APB1、APB2的預(yù)分頻器的輸入端。GPIO外設(shè)是掛載在APB2總線上的, APB2的時(shí)鐘是APB2預(yù)分頻器的輸出,而APB2預(yù)分頻器的時(shí)鐘來源是AHB預(yù)分頻器。因此,把APB2預(yù)分頻器設(shè)置為不分頻,那么我們就可以得到GPIO外設(shè)的時(shí)鐘也等于HCLK,為72MHz了。

SYSCLK:系統(tǒng)時(shí)鐘,STM32大部分器件的時(shí)鐘來源。主要由AHB預(yù)分頻器分配到各個(gè)部件。

HCLK:由AHB預(yù)分頻器直接輸出得到,它是高速總線AHB的時(shí)鐘信號,提供給存儲器,DMA及cortex內(nèi)核,是cortex內(nèi)核運(yùn)行的時(shí)鐘,cpu主頻就是這個(gè)信號,它的大小與STM32運(yùn)算速度,數(shù)據(jù)存取速度密切相關(guān)。

FCLK:同樣由AHB預(yù)分頻器輸出得到,是內(nèi)核的“自由運(yùn)行時(shí)鐘”。“自由”表現(xiàn)在它不來自時(shí)鐘 HCLK,因此在HCLK時(shí)鐘停止時(shí) FCLK 也繼續(xù)運(yùn)行。它的存在,可以保證在處理器休眠時(shí),也能夠采樣和到中斷和跟蹤休眠事件 ,它與HCLK互相同步。

PCLK1:外設(shè)時(shí)鐘,由APB1預(yù)分頻器輸出得到,最大頻率為36MHz,提供給掛載在APB1總線上的外設(shè),APB1總線上的外設(shè)如下:

RCC_APB1Periph_TIM2 TIM2時(shí)鐘

RCC_APB1Periph_TIM3 TIM3時(shí)鐘

RCC_APB1Periph_TIM4 TIM4時(shí)鐘

RCC_APB1Periph_WWDG WWDG時(shí)鐘

RCC_APB1Periph_SPI2 SPI2時(shí)鐘

RCC_APB1Periph_USART2 USART2時(shí)鐘

RCC_APB1Periph_USART3 USART3時(shí)鐘

RCC_APB1Periph_I2C1 I2C1時(shí)鐘

RCC_APB1Periph_I2C2 I2C2時(shí)鐘

RCC_APB1Periph_USB USB時(shí)鐘

RCC_APB1Periph_CAN CAN時(shí)鐘

RCC_APB1Periph_BKP BKP時(shí)鐘

RCC_APB1Periph_PWR PWR時(shí)鐘

RCC_APB1Periph_ALL 全部APB1外設(shè)時(shí)鐘

PCLK2:外設(shè)時(shí)鐘,由APB2預(yù)分頻器輸出得到,最大頻率可為72MHz,提供給掛載在APB2總線上的外設(shè),APB2總線上的外設(shè)如下:

RCC_APB2Periph_AFIO 功能復(fù)用IO時(shí)鐘

RCC_APB2Periph_GPIOA GPIOA時(shí)鐘

RCC_APB2Periph_GPIOB GPIOB時(shí)鐘

RCC_APB2Periph_GPIOC GPIOC時(shí)鐘

RCC_APB2Periph_GPIOD GPIOD時(shí)鐘

RCC_APB2Periph_GPIOE GPIOE時(shí)鐘

RCC_APB2Periph_ADC1 ADC1時(shí)鐘

RCC_APB2Periph_ADC2 ADC2時(shí)鐘

RCC_APB2Periph_TIM1 TIM1時(shí)鐘

RCC_APB2Periph_SPI1 SPI1時(shí)鐘

RCC_APB2Periph_USART1 USART1時(shí)鐘

RCC_APB2Periph_ALL 全部APB2外設(shè)時(shí)鐘

編輯:admin 最后修改時(shí)間:2018-05-23