���оƬHK32MCU�V�iЧ�����}�о����A����ʩ

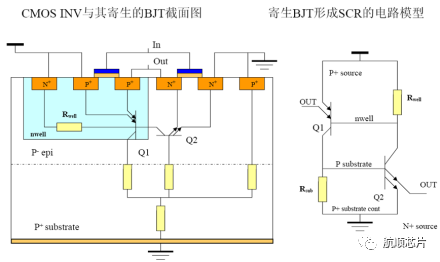

�V�iЧ�������ɿع�(SCR)��һ�NPNPN�Y������CMOS��ˇ�Ĺ��нY��֮һ������NMOS����Դ�^(q��)��P�r�ס�N�塢PMOS����Դ�^(q��)����SCR�Y��(PNPN�Y��)��������һ�����O����ƫ�r���͕������������γ��V�i���V�iЧ����CMOS��ˇ�����еļ���Ч�������ؕ������·��ʧЧ����������оƬ�������V�i�ķ�������Ҫ�pС�r��N��ļ�����裬ʹ���������O�ܲ���̎����ƫ��B(t��i)��

�o���һ�N����Ҋ���Ɖ������������Ԫ�����a��Ӱ푡��o늷��(ESD)�����P��늉�˲׃���������V�iЧ����latch-up�����ǰ댧�w����ʧЧ����Ҫԭ��֮һ����ԓ�����������һ����늈�ʩ���������Y���е������ﱡĤ�ϣ��tԓ�����ﱡĤ�͕�����|�������p�ġ��ܼ��Ľ��ٻ��E�������ڴ�������p�ģ�����������ӿ�����ɵ��^����γ��_·���@�������^�ġ��V�iЧ���������V�i��r�£��������Դ�c��֮�g�γɶ�·����ɴ������EOS����^�d���������p�ġ�

����MOS��ˇ�����S�����ڵ��p�O�;��w�ܣ���CMOS��ˇ�£����c�r�Y�ϕ����¼�����n-p-n-p�Y�����@Щ�Y��������VDD��VSS���Ķ�·���Ķ�ͨ�����Ɖ�оƬ����������ϵ�y(t��ng)�e�`���V�iЧ��ԭ��

���D��ʾ��Q1��һ��ֱʽPNP BJT(�p�O�Y�;��w��), ���O(base)��nwell, ���O����늘O(collector)��������_���ٱ���Q2��һ����ʽ��NPN BJT�����O��P substrate������늘O��������_��ʮ�������У�Rwell��nwell�ļ�����裻Rsub��substrate��衣

ԭ��ʾ��D

�V�iЧ���Įa���C��

��������Ԫ�����ɿɿع裨SCR���·�����o���ɔ_δ�����|�l(f��)�r���ɂ�BJT̎�ڽ�ֹ��B(t��i)����늘O�����C-B�ķ���©������ɣ��������dz�С���˕rLatch up�����a����

�ڮ�����һ��BJT�ļ�늘O������ⲿ�ɔ_ͻȻ���ӵ�һ��ֵ�r������������һ��BJT���Ķ�ʹ�ɂ�BJT���|�l(f��)����ͨ��ͨ����r����PNP���^�����|�l(f��)��������VDD��GND��VSS���g�γɵͿ�ͨ·��֮��������ɔ_��ʧ�����ڃ����O��֮�g�γ���������߀�Ǖ����Դ�͵�֮�g��©늣����i����B(t��i)���V�iЧ����latch-up���ɴ˶��a����

�V�iЧ���|�l(f��)����ģ�M

���HK32MCU��HK32F0ϵ�к�HK32F1ϵ��֮ܛӲ�������݇���Ʒ��MCU���Ѵ����������ڸ��N��ӮaƷ�С��乤��늉�֧��2.0V~5.5V�����˷���ģ�M�|�l(f��)�V�iЧ����latch-up��������ׂ����È����yԇ�l������VCC=5.5V�Ĺ���늉���

����һ

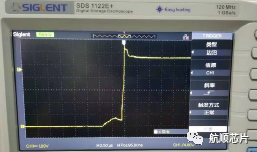

�yԇ�l����VCC=5.5V��VCC�_�]��ȥ����ݣ�����GPIO�ҿա�

�yԇ�������oVCC�������

�yԇ�Y�����|�l(f��)�V�iЧ����latch-up��

���������D��ʾ��VCC����ٶȷ���Ҫ����Փ�����|�l(f��)Latch up��������늲����Ͽ�����늺�VCC���^�_��6V~7V���������ߣ��Ɯy�^�_�|�l(f��)�V�iЧ����latch-up����

����һ��VCC���ΈD

������

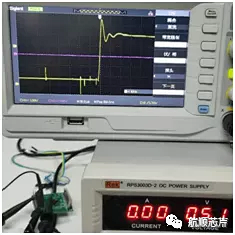

�yԇ�l����VCC=5.5V��VCC�_��0.1uFȥ����ݣ�����GPIO�ҿա�

�yԇ�������oVCC�������

�yԇ�Y�����|�l(f��)�V�iЧ����latch-up��

������VCC����ٶȷ���Ҫ������늲����Ͽ�����늺�VCC���^�_�F(xi��n)�������Ȉ���һ�����أ��Ɯy�^�_�|�l(f��)�V�iЧ����latch-up����

��������VCC���ΈD

������

�yԇ�l����VCC=5.5V��VCC�_��0.1uF+1uFȥ����ݣ�����GPIO�ҿա��yԇ�������oVCC�������

�yԇ�Y�����|�l(f��)�V�iЧ����latch-up��

������VCC����ٶȷ���Ҫ������늲����Ͽ�����늺�VCC�����^�_��6V~7V�F(xi��n)�ͽ�0.1uFȥ����ݲ�e�����Ɯy�^�_�|�l(f��)�V�iЧ����latch-up����

��������VCC���ΈD

������

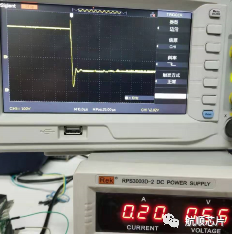

�yԇ�l����VCC=5.5V��VCC�_��0.1uF+1uFȥ����ݣ�����GPIO�ҿա�

�yԇ�������oVCC������늣�ģ�M�ⲿ��ؓ�d���Σ�

�yԇ�Y�����|�l(f��)�V�iЧ����latch-up��

������VCC늉����ٵ��䣬�γ�VCC�_���^�ͬF(xi��n)���Ɯy�_�|�l(f��)�V�iЧ����latch-up���������|�l(f��)���V�iЧ����latch-up���Լ��O����200mA����, VCC�o�����»֏͵�5.5V��

�����ģ�VCC���ΈD

������

�yԇ�l����VCC=5.5V��VCC�_��0.1uF+1uFȥ����ݣ�������1�Wķ��裬��ijIO��ֱ�ӽӵ��Դ��

�yԇ�������oVCC�������

�yԇ�Y�����|�l(f��)�V�iЧ����latch-up��

���������˲�g��IO��늉�����VCC�������|�l(f��)Latch up��

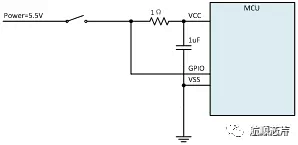

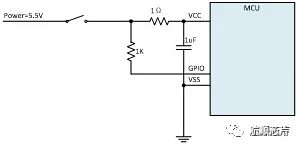

�����壺�·�D

������N�������ǿ����|�l(f��)�V�iЧ��(latch-up)���}�Ĉ��������ƴ�ʩ������ԭ��D���£�

1. ����MCU��VCC����늻����˲�g�a���^�_���_�F(xi��n)�����Դ��оƬVCC֮�g����1�Wķ��裬����оƬVCC�ϼ�0.1uF��1uFȥ����ݡ�

2.����Ĭ�J��Ҫ���ƽ��IO��ֱ�ӽӵ��Դ�F(xi��n)����Ҫͨ�^1K�����ϵ���������������Դ��

����ԭ��D

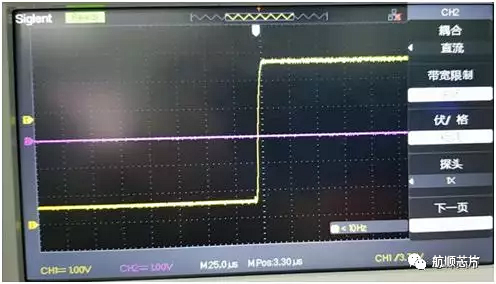

ͨ�^���ϸ��ƴ�ʩ���y��VCC�Դ�������£�������������ݵ����ƣ�VCC�ϛ]�г��F(xi��n)�^�_�F(xi��n)�yԇ�Y����ȫ�����|�l(f��)�|�l(f��)�V�iЧ����latch-up����

���ƺ��VCC����

�V�iЧ���A����ʩ���Y

�������V�iЧ���Įa���C�����|�l(f��)����ģ�M���ƴ�ʩ�Ĝyԇ�Y�����Կ������|�l(f��)�V�iЧ����latch-up�����}���кܶ�����أ�Ҫ��ֹ�V�iЧ����latch-up���������Ѓɷ����ʩ��һ�Ǐ�оƬ�ĽǶ��v������ͨ�^оƬ��ˇ�ĸ��M���OӋ�ă�(y��u)���������V�i��Σ�U�����Ǐđ��õĽǶ��v������ͨ�^һЩ�A����ʩ�������|�l(f��)�V�iЧ����latch-up���Ď��ʣ����w�磺

1����ݔ��˺�ݔ���˼��Qλ�·��ʹݔ���ݔ�������^Ҏ(gu��)��늉���

2��оƬ���Դݔ��˼�ȥ����ݣ���ֹVCC�˳��F(xi��n)˲�g�ĸ߉���

3����VCC�����Դ֮�g��������裬��ʹ�д�����Ҳ�����Mȥ��

4����ϵ�y(t��ng)�Ɏׂ��Դ�քe��늕r���_�PҪ����������_���r�����_��CMOS�·���Դ�����_��ݔ����̖��ؓ�d���Դ���P�]�r�����P�]ݔ����̖��ؓ�d���Դ�����P�]CMOS�·���Դ��

����Ҫ�˽���ຽ�MCU�aƷ��Ո(li��n)ϵ��혺��Ĵ����̣��f���¿Ƽ������ߒߴa(li��n)ϵ�҂���

��֮ǰ�Ľ�B�У��҂�Ҳ���ҽ�B�������оƬHK32MCU�{ԇ�ĵ�����Ҳ��Ŀǰ�҂����Ƶķdz�����Ľ�Q������

����zzy ����ĕr�g��2022-05-19