MOS╣▄ķōųĄļŖē║┼c£ŽķL║═£ŽīÆĄ─ĻPŽĄ╝░ė░ĒæķōųĄļŖē║Ą─ę“╦žĘų╬÷

ķōųĄļŖē║ Ż©Threshold voltageŻ®Ż║═©│Żīóé„▌ö╠žąįŪ·ŠĆųą▌ö│÷ļŖ┴„ļS▌ö╚ļļŖē║Ė─ūāČ°╝▒äĪūā╗»▐D(zhu©Żn)š█ģ^(q©▒)Ą─ųą³cī”æ¬Ą─▌ö╚ļļŖē║ĘQ×ķķōųĄļŖē║ĪŻį┌├Ķ╩÷▓╗═¼Ą─Ų„╝■ĢrŠ▀ėą▓╗═¼Ą─ģóöĄ(sh©┤)ĪŻ╚ń├Ķ╩÷ł÷░l(f©Ī)╔õĄ─╠žąįĢrŻ¼ļŖ┴„▀_ĄĮ10mAĢrĄ─ļŖē║▒╗ĘQ×ķķōųĄļŖē║ĪŻ

MOS╣▄ķōųĄļŖē║┼c£ŽķL║═£ŽīÆĄ─ĻPŽĄ

ĻPė┌ MOSFET Ą─ W ║═ L ī”ŲõķōųĄļŖē║ Vth Ą─ė░ĒæŻ¼īŹļHį┌┐╝æ]╣ż╦ćŽÓĻPę“╦ž║¾Č╝╩Ū▒╚▌^Å═ļsŻ¼Ą½╩Ūę▓┐╔ęįėąę╗ą®║å╗»Ą─Ęų╬÷Ż¼▀@└’ų„ę¬▀Ć╩ŪĘų╬÷«öŠ¦¾w╣▄╠Äį┌šŁ£ŽĄ└║═Č╠£ŽĄ└ŪķørŽ┬Ż¼MOSFET ║─▒Mģ^(q©▒)Ą─ļŖ║╔Ą─ūā╗»Ż¼Å─Č°Ęų╬÷Ųõī”Š¦¾w╣▄Ą─ķōųĄļŖē║Ą─ū„ė├ĪŻ

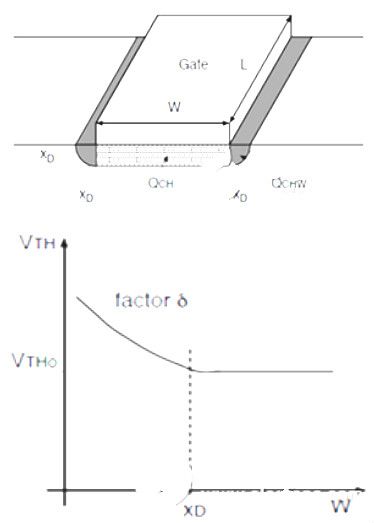

Narrow channel šŁ£ŽĄ─Ęų╬÷

Å─╔ŽłD┐╔ęį┐┤ĄĮŻ¼øQČ©MOSFETķōųĄļŖē║Ą─║─▒MīėļŖ║╔Ż¼▓ó▓╗āH╩Ūį┌¢┼Ž┬ģ^(q©▒)ė“Ą─ļŖ║╔ QchŻ╗īŹļH╔Žį┌łDųą║─▒Mģ^(q©▒)ū¾ėę┼c▒Ē├µŽÓĮė╠ÄŻ¼▀ĆąĶę¬ėąŅ~═ŌĄ─ļŖ║╔ QchwĪŻ

į┌Š¦¾w╣▄Ą─£ŽīÆ W ▌^┤¾ĢrŻ¼Qchw ▀@ę╗Ņ~═ŌĄ─ļŖ║╔┐╔ęį║÷┬įŻ╗Č°«ö£ŽīÆ W ▌^ąĪĢrŻ¼Qchw ▓╗─▄į┘║÷┬įŻ¼╩╣Ą├Ą╚ą¦Ą─║─▒MīėļŖ║╔├▄Č╚į÷╝ėŻ¼MOS ╣▄Ą─ķōųĄļŖē║╔²Ė▀Ż¼╝┤╚ń╔Ž├µłD╦∙╩ŠĪŻ

īŹļH╔ŽŻ¼šŁ£Žī¦ų┬Ą─ķōųĄļŖē║Ą─ūā╗»ę▓┐╔ęį└ĒĮŌ×ķį┌£ŽīÆ W ĘĮŽ“Ą─▀ģŠēļŖł÷Ą─ļŖ┴”ŠĆ│÷¼F(xi©żn)į┌£ŽĄ└ęį═ŌŻ¼ę“┤╦ąĶę¬Ė³ČÓĄ─¢┼ļŖē║üĒŠS│ų£ŽĄ└ķ_åóĪŻę“┤╦šŁ£ŽĄ─ą¦æ¬īŹļH╔Ž┼cŠ▀¾wĄ─╝»│╔ļŖ┬Ę╣ż╦ćŻ¼└²╚ńŲ„╝■▓╔ė├Ą─Ė¶ļxĘĮ╩Į║═Ė¶ļxģ^(q©▒)ė“Ą─ōĮļsØŌČ╚Ą╚ĻPŽĄ║▄┤¾ĪŻ

ī”ė┌ STI Ż©shallow trench isolaTIonŻ® Ė¶ļxĘĮ╩ĮĄ─ MOSFETŻ¼ ė╔ė┌ STI wall Ą─ū„ė├Ż¼£ŽīÆ W ĘĮŽ“Ą─▀ģŠēļŖł÷Ą─ļŖ┴”ŠĆīŹļH╔Ž╩Ūį┌£ŽĄ└ĘĮŽ“╝»ųąŻ¼ę“┤╦Ģ■│÷¼F(xi©żn)╦∙ų^Ą─ inverse narrow-width effectŻ¼ę▓╝┤╩ŪļSų°£ŽīÆ W Ą─£pąĪŻ¼ķōųĄļŖē║ļSų«£pąĪĪŻ

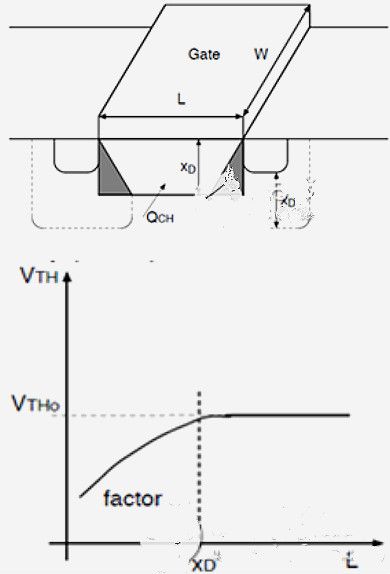

Short channel Č╠£ŽĄ─Ęų╬÷

╚ń╔Ž├µū¾łD╦∙╩ŠŻ¼ Š¦¾w╣▄ųą║─▒MīėļŖ║╔░³└©Å─į┤ĄĮ┬®Ą─╦∙ėąļŖ║╔ĪŻ Ą½╩ŪŻ¼ īŹļH╔Žį┌┐┐Į³į┤║═┬®Č╦Ą─▓┐ĘųļŖ║╔ Qchl Ż¼ ▓╗į┘ų▒Įė╩▄┐žė┌¢┼Ż¼ Č°╩Ūė╔į┤║═┬®üĒ┐žųŲĪŻ ę“┤╦ Qchl ╩Ū▓╗æ¬įō░³║¼į┌ķōųĄļŖē║Ą─ėŗ╦ŃųąĄ─ĪŻ

ŅÉ╦Ųų«Ū░Ą─Ęų╬÷Ż¼ «ö£ŽķL L ▌^ąĪĢrŻ¼ ąĶę¬┐╝æ] Qchl ė░ĒæŻ¼ ╩╣Ą╚ą¦Ą─║─▒MīėļŖ║╔├▄Č╚£pąĪŻ¼ MOS ╣▄Ą─ķōųĄļŖē║£pąĪŻ¼╝┤╚ń╔Ž├µėęłD╦∙╩ŠĪŻ

į┌Š▀¾w╣ż╦ćųąŻ¼ ė╔ė┌┤µį┌£ŽĄ└Ą─ĘŪŠ∙ä“ōĮļsĄ╚¼F(xi©żn)Ž¾Ż¼īŹļH╔ŽĢ■╩╣Ą├ėą reverse short-channel effect Ą─│÷¼F(xi©żn)Ż¼╝┤ļSų° MOSFET Ą─£ŽķL L Ą─£pąĪŻ¼ķōųĄļŖē║Ģ■Ž╚ąĪĘ∙╔²Ė▀Ż¼ų«║¾ L ▀Mę╗▓Į£pąĪĢrŻ¼ķōųĄļŖē║Ž┬ĮĄŻ¼▓óŪę┤╦ĢrĄ─ķōųĄļŖē║ī”£ŽķLĄ─ūā╗»Ė³×ķ├¶ĖąĪŻ

ė░ĒæķōųĄļŖē║Ą─ę“╦ž

ę╗éĆ╠žČ©Ą─Š¦¾w╣▄Ą─ķōųĄļŖē║║═║▄ČÓę“╦žėąĻPŻ¼░³└©backgateĄ─ōĮļsŻ¼ļŖĮķ┘|(zh©¼)Ą─║±Č╚Ż¼¢┼śO▓─┘|(zh©¼)║═ļŖĮķ┘|(zh©¼)ųąĄ─▀^╩ŻļŖ║╔ĪŻ

1Īó▒│¢┼Ą─ōĮļs

▒│¢┼Ż©backgateŻ®Ą─ōĮļs╩ŪøQČ©ķōųĄļŖē║Ą─ų„ę¬ę“╦žĪŻ╚ń╣¹▒│¢┼ōĮļs

įĮųžŻ¼╦³Š═įĮļyĘ┤▐D(zhu©Żn)ĪŻę¬Ę┤▐D(zhu©Żn)Š═ę¬Ė³ÅŖĄ─ļŖł÷Ż¼ķōųĄļŖē║Š═╔Ž╔²┴╦ĪŻMOS╣▄Ą─▒│¢┼ōĮļs─▄═©▀^į┌ĮķļŖīė▒Ē├µŽ┬Ą─╔į╬óĄ─implantüĒš{(di©żo)š¹ĪŻ

2ĪóļŖĮķ┘|(zh©¼)

ļŖĮķ┘|(zh©¼)į┌øQČ©ķōųĄļŖē║ĘĮ├µę▓Ų┴╦ųžę¬ū„ė├ĪŻ║±ļŖĮķ┘|(zh©¼)ė╔ė┌▒╚▌^║±Č°Ž„╚§┴╦ļŖł÷ĪŻ╦∙ęį║±ļŖĮķ┘|(zh©¼)╩╣ķōųĄļŖē║╔Ž╔²Ż¼Č°▒ĪļŖĮķ┘|(zh©¼)╩╣ķōųĄļŖē║Ž┬ĮĄĪŻ

3Īó¢┼śOĄ─╬’┘|(zh©¼)│╔Ęų

¢┼śOŻ©gateŻ®Ą─╬’┘|(zh©¼)│╔Ęųī”ķōųĄļŖē║ę▓ėą╦∙ė░ĒæĪŻ╚ń╔Ž╦∙╩÷Ż¼«öGATE║═BACKGATEČ╠ĮėĢrŻ¼ļŖł÷Š═╩®╝ėį┌gate oxide╔ŽĪŻ

4ĪóĮķļŖīė┼c¢┼śOĮń├µ╔Ž▀^╩ŻĄ─ļŖ║╔

GATE OXIDE╗“č§╗»╬’║═╣Ķ▒Ē├µų«ķgĮń├µ╔Ž▀^╩ŻĄ─ļŖ║╔ę▓┐╔─▄ė░ĒæķōųĄļŖē║ĪŻ▀@ą®ļŖ║╔ųą┐╔─▄ėąļxūė╗»Ą─ļs┘|(zh©¼)įŁūėŻ¼▓Č½@Ą─▌d┴„ūėŻ¼╗“ĮY(ji©”)śŗ(g©░u)╚▒Ž▌ĪŻļŖĮķ┘|(zh©¼)╗“╦³▒Ē├µ▓Č½@Ą─ļŖ║╔Ģ■ė░ĒæļŖł÷▓ó▀Mę╗▓Įė░ĒæķōųĄļŖē║ĪŻ╚ń╣¹▒╗▓Č½@Ą─ļŖūėļSų°ĢrķgŻ¼£žČ╚╗“Ų½ų├ļŖē║Č°ūā╗»Ż¼─Ū├┤ķōųĄļŖē║ę▓Ģ■Ė·ų°ūā╗»ĪŻ