MOS晶體管的閾值電壓及輸出解析

MOS晶體管MOS管

MOS管全稱金屬—氧化物—半導(dǎo)體場效應(yīng)晶體管或稱金屬—絕緣體—半導(dǎo)體場效應(yīng)晶體管,英文名metal oxide semiconductor,屬于場效應(yīng)管中的絕緣柵型,因此,MOS管有時(shí)候又稱為絕緣柵場效應(yīng)管。

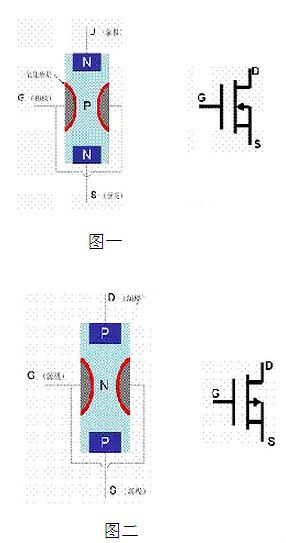

MOS管這個(gè)器件有兩個(gè)電極,分別是漏極D和源極S,無論是圖一的N型還是圖二的P型都是一塊摻雜濃度較低的P型半導(dǎo)體硅襯底上,用半導(dǎo)體光刻、擴(kuò)散工藝制作兩個(gè)高摻雜濃度的N+/P+區(qū),并用金屬鋁引出漏極D和源極S。然后在漏極和源極之間的N/P型半導(dǎo)體表面復(fù)蓋一層很薄的二氧化硅(Si02)絕緣層膜,在再這個(gè)絕緣層膜上裝上一個(gè)鋁電極,作為柵極G。這就構(gòu)成了一個(gè)N/P溝道(NPN型)增強(qiáng)型MOS管。

MOS管工作原理與MOS晶體管的閾值電壓解析

雙極結(jié)晶體管是放大輸入電流的微小變化以產(chǎn)生輸出電流的大變化的晶體管。另一種類型的晶體管,稱為場效應(yīng)晶體管(MOSFET),將輸入電壓的變化轉(zhuǎn)換為輸出電流的變化,因此FET的增益通過其跨導(dǎo)來測量,跨導(dǎo)定義為輸出電流變化與變化的比率在輸入電壓。電壓施加到稱為其柵極的輸入端子,流過晶體管的電流取決于柵極電壓產(chǎn)生的電場。在柵電極下面放置了絕緣板,因此MOSFET的柵極電流近似為零。

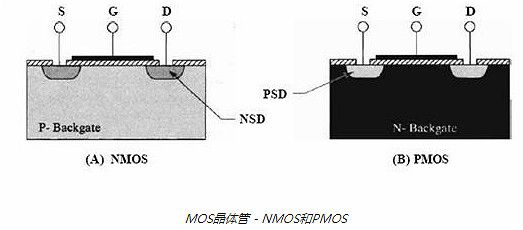

基于在絕緣層下面形成的溝道,MOS管被分類為N溝道晶體管(NMOS)和P溝道晶體管(PMOS)。兩個(gè)晶體管的橫截面圖如圖1所示。每個(gè)晶體管應(yīng)具有源極,漏極,柵極和通常稱為體端子的背柵。在NMOS的情況下,通過將N型摻雜劑擴(kuò)散到P襯底來產(chǎn)生源極和柵極,反之亦然,用于PMOS。MOS晶體管的源極和漏極是可互換的,載流子流出源極并進(jìn)入漏極。

NMOS晶體管 - 工作原理

下面解釋NMOS管工作原理。MOS晶體管有三個(gè)操作區(qū)域。

1. 截止區(qū)域(V GS TH )

2. 三極管區(qū)域(V GS > V TH和V DS DSsat )

3. 飽和區(qū)(V GS > V TH和V DS > V DSsat )

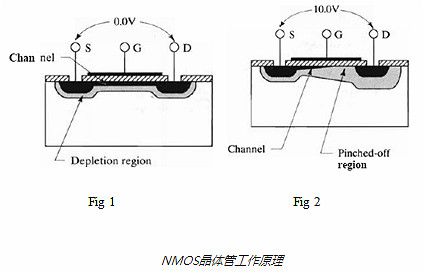

最初考慮具有V GS = 0 的Tr ,即沒有施加?xùn)艠O到源極電壓。它類似于在源極和漏極之間背靠背連接的2個(gè)二極管。所以沒有電流從源流到漏極。在源極 - 襯底,漏極 - 襯底連接處也會(huì)形成耗盡區(qū)。當(dāng) V GS 電壓逐漸增加到低于閾值電壓(V TH)時(shí),柵極下方的空穴被排斥以產(chǎn)生耗盡區(qū),并且在源極到漏極的柵極下它變得連續(xù)。然后V GS 增加到閾值電壓即V GS > V TH 。此時(shí),P sub中的少數(shù)載流子(電子)穿過耗盡區(qū)并到達(dá)柵極下方。此過程稱為反轉(zhuǎn)。柵極下方的電子數(shù)量取決于電壓V GS - V TH 。

因此,由于該橫向電場而產(chǎn)生導(dǎo)電通道(圖1)。在源極和漏極之間建立通道后,V DS(漏極到源極電壓)從0逐漸增加。當(dāng)V DS 當(dāng)漏極相對于源極變得更正時(shí)(圖2),漏極將變?yōu)檎龢O,子極點(diǎn)會(huì)反向偏置,耗盡區(qū)變寬,由于這種橫向電場,電流從源極開始流動(dòng)。漏極和電流隨著V DS的增加而增加。因此,源極處的電位小于源極處的電位,耗盡區(qū)域在漏極附近變寬,并且溝道在此逐漸變細(xì)。

在V DS = V DSsat 時(shí),溝道剛剛接觸漏極,相應(yīng)的漏極 - 源極電壓稱為夾斷電壓。高于飽和電壓,電流變得恒定。載體沿著由沿著相對弱的電場推動(dòng)的通道向下移動(dòng)。當(dāng)它們到達(dá)夾斷區(qū)域的邊緣時(shí),它們被強(qiáng)電場吸過耗盡區(qū)域。隨著漏極電壓的增加,溝道兩端的電壓降不會(huì)增加; 相反,夾斷區(qū)域變寬。因此,漏極電流達(dá)到極限并且不再增加。

MOS晶體管的閾值電壓

MOS晶體管的閾值電壓是剛好形成導(dǎo)電溝道所需的柵極 - 源極偏置電壓,其中晶體管的背柵(體)連接到源極。如果柵極 - 源極偏置(V GS)小于閾值電壓,則不形成溝道。給定晶體管呈現(xiàn)的閾值電壓取決于許多因素,包括背柵極摻雜,電介質(zhì)厚度,柵極材料和電介質(zhì)中的過量電荷。將簡要檢查這些影響中的每一個(gè)。

背柵摻雜對閾值電壓有重要影響。如果背柵更重?fù)诫s,那么反轉(zhuǎn)以形成通道變得更加困難。因此需要更強(qiáng)的電場來實(shí)現(xiàn)反轉(zhuǎn),并且閾值電壓增加。可以通過在柵極電介質(zhì)下方進(jìn)行淺注入來摻雜溝道區(qū)域來調(diào)整MOS晶體管的背柵摻雜。這種類型的植入物稱為閾值調(diào)節(jié)植入物(或V TH 調(diào)節(jié)植入物)。

考慮V TH 調(diào)節(jié)注入對NMOS晶體管的影響。如果植入物由受體組成,則硅表面變得更難以反轉(zhuǎn)并且閾值電壓增加。如果植入物由供體組成,則表面變得更容易反轉(zhuǎn)并且閾值降低。如果注入足夠的施主,則硅的表面實(shí)際上可以成為反摻雜的。在這種情況下,薄的N型硅層在零柵極偏壓下形成永久溝道。隨著柵極偏壓的增加,溝道變得更強(qiáng)烈地反轉(zhuǎn)。隨著柵極偏壓的減小,溝道的反轉(zhuǎn)變得不那么強(qiáng)烈,并且在某些時(shí)候它會(huì)消失。

閾值電壓也由在柵電極下方使用的電介質(zhì)確定。較厚的電介質(zhì)通過將電荷分開更大的距離來削弱電場。因此,較厚的電介質(zhì)增加閾值電壓,而較薄的電介質(zhì)減小閾值電壓。理論上,電介質(zhì)的材料也會(huì)影響電場。實(shí)際上,幾乎所有MOS晶體管都使用純二氧化硅作為柵極電介質(zhì)。可以制造極薄的SiO 2 層,具有純度和均勻性。因此,替代的介電材料在使用中非常罕見。

柵電極材料也影響晶體管的閾值電壓。在施加電壓時(shí),電場由柵極和背柵材料之間的功函數(shù)的差異產(chǎn)生。最常見的重?fù)诫s多晶硅用作柵電極。通過改變摻雜,多晶硅的功函數(shù)可以改變到某種程度。在柵極氧化物中或沿著氧化物和多晶硅表面之間的界面存在過量電荷也是影響閾值電壓的主要因素。這些電荷可以是電離的雜質(zhì)原子,捕獲的載流子或結(jié)構(gòu)缺陷。這些電荷的存在將改變電場,從而改變閾值電壓。如果捕獲的電荷量隨時(shí)間,溫度或施加的偏壓而變化,則閾值電壓也將變化。

該NMOS晶體管的閾值電壓實(shí)際上是負(fù)的。這種晶體管稱為耗盡型NMOS,或簡稱為耗盡型NMOS。相反,具有正閾值電壓的NMOS被稱為增強(qiáng)型NMOS或增強(qiáng)型NMOS。大多數(shù)商業(yè)制造的MOS晶體管是增強(qiáng)型器件,但是有一些應(yīng)用需要耗盡型器件。還可以構(gòu)建耗盡型PMOS。這種器件將具有正閾值電壓。

MOS晶體管的閾值電壓輸出特點(diǎn)

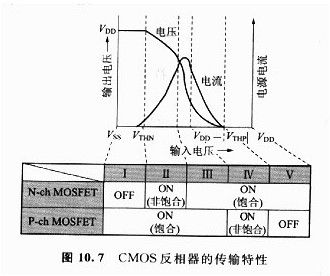

邏輯閾值電壓

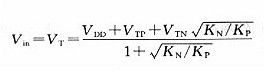

由于邏輯閾值電壓是式(10.1)中的-IDS與式(10.2)中的IDS相等時(shí)的電壓,所以應(yīng)用這個(gè)關(guān)系能夠求得Vin:

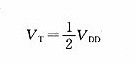

假如KN=Kp,即KN/KP=1,經(jīng)過選擇恰當(dāng)?shù)膒溝MOS晶體管與n溝MOS晶體管的參數(shù),可以完成|VTP|=|VTN|,那么作為反相器,當(dāng)然就能夠得到如下理想的關(guān)系:

實(shí)踐上,這樣的理想狀態(tài)是不存在的。在版圖設(shè)計(jì)中,經(jīng)過設(shè)計(jì)恰當(dāng)?shù)膒溝MOS晶體管與n溝MOS晶體管的W/L比,盡可能使VTP與VTN相等,能夠得到接近1/2VDD的邏輯閾值電壓。