─·║├Ż¼ÜgėŁ▀M(j©¼n)╚ļ╔Ņ█┌╩ąĘf╠žą┬┐Ų╝╝ėąŽ▐╣½╦Š╣┘ĘĮŠW(w©Żng)šŠŻĪ

─·║├Ż¼ÜgėŁ▀M(j©¼n)╚ļ╔Ņ█┌╩ąĘf╠žą┬┐Ų╝╝ėąŽ▐╣½╦Š╣┘ĘĮŠW(w©Żng)šŠŻĪ

Constraints MethodologyŻ©╝s╩°ĘĮĘ©šōŻ®

ĻP(gu©Īn)ė┌╝s╩°ĘĮĘ©šō

įO(sh©©)ėŗ(j©¼)╝s╩°Č©┴x┴╦ŠÄūg┴„│╠▒žĒÜØMūŃĄ─ę¬Ū¾Ż¼ęį╩╣įO(sh©©)ėŗ(j©¼)į┌░Õ╔ŽŲū„ė├ĪŻ ▓óĘŪ╦∙ėą▓Į¾EČ╝╩╣ė├╦∙ėą╝s╩°

į┌ŠÄūg┴„│╠ųąĪŻ └²╚ńŻ¼╬’└Ē╝s╩°āHį┌īŹ(sh©¬)¼F(xi©żn)▓Į¾EŲ┌ķg╩╣ė├Ż©╝┤Ż¼ė╔▓╝ŠųŲ„║═┬Ęė╔Ų„Ż®ĪŻ

ė╔ė┌Xilinx®Vivado®╝»│╔įO(sh©©)ėŗ(j©¼)Łh(hu©ón)Š│Ż©IDEŻ®ŠC║Ž║═īŹ(sh©¬)¼F(xi©żn)╦ŃĘ©╩ŪĢr(sh©¬)ą““ī(q©▒)äė(d©░ng)Ą─Ż¼ę“┤╦▒žĒÜäō(chu©żng)Į©▀m«ö(d©Īng)?sh©┤)─Ģr(sh©¬)ą“╝s╩°ĪŻ

▀^(gu©░)Č╚╝s╩°╗“įO(sh©©)ėŗ(j©¼)▓╗ūŃĢ■(hu©¼)╩╣Ģr(sh©¬)ą“╩šö┐ūāĄ├└¦ļyĪŻ ─·▒žĒÜ╩╣ė├Ę¹║Ž─·Ą─æ¬(y©®ng)ė├│╠ą“ę¬Ū¾Ą─║Ž└Ē╝s╩°ĪŻ

ę▓Š═╩Ūšf(shu©Ł)▀@ę╗š┬ų„ꬊ═╩ŪųvĮŌ╝s╩°Ą─ąą×ķęÄ(gu©®)ĘČŻ¼╔Žę╗š┬ųv╩÷Ą─╩Ū╚ń║╬▌ö╚ļ╝s╩°╬─╝■Ż¼▀@Č╝╩Ūėąę╗Č©Ēśą“Ą─

ĮM┐Ś─ŃĄ─╝s╩°Ż©éĆ(g©©)╚╦šJ(r©©n)×ķ▒╚▌^ųžę¬Ż¼æ¬(y©®ng)įō╩Ū╬ę╦∙ąĶꬥ─▓┐ĘųŻ®

The Vivado IDE allows you to use one or many constraint files. While using a single

constraint file for the entire compilation flow might seem more convenient, it can be a

challenge to maintain all the constraints as the design becomes more complex. This is

usually the case for designs that use several IP cores or large blocks developed by different

teams.

After the timing and physical constraints have been imported, independent of the number

of source files or whether the design is in Project/Non-Project mode, all the constraints can

be exported as a single file with the write_xdc command. The constraints are written to

the specified output file in the same order that they were read into the project or design.

The command line option write_xdc -type can be used to select a sub-set of

constraints (timing, physical, or waiver) to export.

ėų╩Ūę╗┤¾Č╬ėó╬─Ż¼▓╗Üwšf(shu©Ł)šµĄ─Ż¼╝╝ąg(sh©┤)ķ_░l(f©Ī)╚╦åTę╗ą®╝╝ąg(sh©┤)┘Y┴Žę╗Č©ę¬┐┤Č«Ż¼Ą½╩Ū▒╚▌^ÖÓ(qu©ón)═■Ą─┤¾▓┐ĘųČ╝į┤ūįėó╬─░µŻ¼╦∙ęįīW(xu©”)║├ėóšZ(y©│)║▄ųžę¬ŻĪŻĪŻĪ ▓╗▀^(gu©░)ø]ėą─Ū├┤ČÓĢr(sh©¬)ķgūī╬ę¼F(xi©żn)īW(xu©”)ėó╬─

ų╗─▄═╦Č°Ū¾Ųõ┤╬Ż¼ŽļŽļ▐kĘ©Ż¼

Vivado IDEį╩įS─·╩╣ė├ę╗éĆ(g©©)╗“ČÓéĆ(g©©)╝s╩°╬─╝■ĪŻ ļm╚╗ī”(du©¼)š¹éĆ(g©©)ŠÄūg┴„╩╣ė├å╬éĆ(g©©)╝s╩°╬─╝■╦Ų║§Ė³ĘĮ▒ŃŻ¼Ą½ļSų°įO(sh©©)ėŗ(j©¼)ūāĄ├Ė³╝ėÅ═(f©┤)ļsŻ¼ŠSūo(h©┤)╦∙ėą╝s╩°┐╔─▄╩Ūę╗éĆ(g©©)╠¶æ(zh©żn)ĪŻ ī”(du©¼)ė┌╩╣ė├ė╔▓╗═¼łF(tu©ón)ĻĀ(du©¼)ķ_░l(f©Ī)Ą─ČÓéĆ(g©©)IP║╦╗“┤¾ēKĄ─įO(sh©©)ėŗ(j©¼)Ż¼═©│ŻŠ═╩Ū▀@ĘNŪķørĪŻ

ī¦(d©Żo)╚ļČ©Ģr(sh©¬)║═╬’└Ē╝s╩°║¾Ż¼¬Ü(d©▓)┴óė┌į┤╬─╝■Ą─öĄ(sh©┤)┴┐╗“įO(sh©©)ėŗ(j©¼)╩Ūʱ╠Äė┌ĒŚ(xi©żng)─┐/ĘŪĒŚ(xi©żng)─┐─Ż╩ĮŻ¼┐╔ęį╩╣ė├write_xdc├³┴Ņīó╦∙ėą╝s╩°ī¦(d©Żo)│÷×ķå╬éĆ(g©©)╬─╝■ĪŻ

╝s╩°ęį┼cūx╚ļĒŚ(xi©żng)─┐╗“įO(sh©©)ėŗ(j©¼)ŽÓ═¼Ą─Ēśą“?q©▒)æ╚ļųĖČ©Ą─▌ö│÷╬─╝■Ī?br />├³┴Ņąą▀xĒŚ(xi©żng)write_xdc -type┐╔ė├ė┌▀xō±ę¬ī¦(d©Żo)│÷Ą─╝s╩°Ż©Ģr(sh©¬)ķgŻ¼╬’└Ē╗“╗Ē├ŌŻ®ūė╝»ĪŻ

▓╗▀^(gu©░)▀@└’ėąę╗éĆ(g©©)Į©ūhŻ║

RECOMMENDED: Xilinx recommends that you separate timing constraints and physical constraints by

saving them into two distinct files. You can also keep the constraints specific to a certain module in a

separate file.

Į©ūhŻ║XilinxĮ©ūh─·īóĢr(sh©¬)ą“╝s╩°║═╬’└Ē╝s╩°Ęųķ_Ż¼īó╦³éā▒Ż┤µ×ķā╔éĆ(g©©)▓╗═¼Ą─╬─╝■ĪŻ ─·▀Ć┐╔ęįīó╠žČ©ė┌─│éĆ(g©©)─ŻēKĄ─╝s╩°▒Ż┤µį┌å╬¬Ü(d©▓)Ą─╬─╝■ųąĪŻ

ĒŚ(xi©żng)─┐─Ż╩ĮŻ©╣ż│╠─Ż╩ĮŻ®/ĘŪĒŚ(xi©żng)─┐─Ż╩ĮŻ©ĘŪ╣ż│╠─Ż╩ĮŻ®Ą─Ė┼─ŅŻ║

▀@╩Ūā╔ĘNVIVADOĄ─ā╔ĘNįO(sh©©)ėŗ(j©¼)┴„│╠─Ż╩Į

Ż©ę╗Ż® įO(sh©©)ėŗ(j©¼)š▀┐╔ęį╩╣ė├╗∙ė┌╣ż│╠Ą─ĘĮĘ©ūįäė(d©░ng)╣▄└ĒįO(sh©©)ėŗ(j©¼)▀^(gu©░)│╠║═įO(sh©©)ėŗ(j©¼)öĄ(sh©┤)ō■(j©┤)Ż¼▀@éĆ(g©©)Š═╩Ūšf(shu©Ł)┐╔ęįė├VIVADO▄ø╝■üĒ(l©ói)▀M(j©¼n)ąą

Ż©Č■Ż®┐╔ęįĖ∙ō■(j©┤)TCL─_▒ŠĄ─ĘĮĘ©Ż¼┐╔ęįūį╝║įO(sh©©)ėŗ(j©¼)╣▄└Ēį┤╬─╝■║═įO(sh©©)ėŗ(j©¼)┴„│╠Ż¼▀@ĘNĘĮĘ©ĘQ×ķĘŪ╣ż│╠─Ż╩ĮŻ¼▀@Š═ĘŪ│ŻĖ▀┤¾╔Ž┴╦Ż¼Š═Ž±╩ŪLinux└’shell Windows└’Ą─docŻ¼▓╗▀^(gu©░)╬ęū„×ķ│§īW(xu©”)š▀Ż¼▀Ć╩Ū▀xė├Ą┌ę╗ĘNĘĮĘ©░╔ĪŻ

Project Flows

You can add your Xilinx Design Constraints (XDC) files to a constraints set during the

creation of a new project, or later, from the Vivado IDE menus.

Figure 2-1 shows two constraint sets in a project, which are Single or Multi XDC. The first

constraint set includes two XDC files. The second constraint set uses only one XDC file

containing all the constraints.

You can also add Tcl scripts to your constraints set as unmanaged constraints or

unmanaged Tcl scripts. The Vivado Design Suite does not write modified constraints back

into an unmanaged Tcl script. Tcl scripts and XDC files are loaded in the same sequence as

displayed in the Vivado IDE (if they belong to the same PROCESSING_ORDER group) or as

reported by the command report_compile_order -constraints.

An XDC file or a Tcl script can be used in several constraints sets if needed. For more

information on how to create and add constraint files and constraints sets to your project,

see Working with Constraints in the Vivado Design Suite User Guide: System-Level Design

Entry (UG895) [Ref 2].

ĒŚ(xi©żng)─┐┴„│╠

─·┐╔ęįį┌äō(chu©żng)Į©ą┬ĒŚ(xi©żng)─┐Ų┌ķg╗“╔į║¾Å─Vivado IDE▓╦å╬ųąīóXilinxįO(sh©©)ėŗ(j©¼)╝s╩°Ż©XDCŻ®╬─╝■╠Ē╝ėĄĮ╝s╩°╝»ųąĪŻ

łD2-1’@╩Š┴╦ĒŚ(xi©żng)─┐ųąĄ─ā╔éĆ(g©©)╝s╩°╝»Ż¼╝┤å╬XDC╗“ČÓXDCĪŻ Ą┌ę╗éĆ(g©©)╝s╩°╝»░³└©ā╔éĆ(g©©)XDC╬─╝■ĪŻ Ą┌Č■éĆ(g©©)╝s╩°╝»āH╩╣ė├ę╗éĆ(g©©)░³║¼╦∙ėą╝s╩°Ą─XDC╬─╝■ĪŻ

╚ń╣¹ĒŚ(xi©żng)─┐░³║¼╩╣ė├Ųõūį╔Ē╝s╩°Ą─IPŻ¼ätŽÓæ¬(y©®ng)Ą─╝s╩°╬─╝■▓╗Ģ■(hu©¼)│÷¼F(xi©żn)į┌╝s╩°╝»ųąĪŻ ŽÓĘ┤Ż¼╦³┼cIPį┤╬─╝■ę╗Ų┴ą│÷ĪŻ

─·▀Ć┐╔ęįīóTcl─_▒Š╠Ē╝ėĄĮ╝s╩°╝»ųąū„×ķĘŪ═ą╣▄╝s╩°╗“ĘŪ═ą╣▄Tcl─_▒ŠĪŻ VivadoįO(sh©©)ėŗ(j©¼)╠ū╝■▓╗Ģ■(hu©¼)ųžą┬ŠÄīæą▐Ė─Ą─╝s╩°

▀M(j©¼n)╚ļę╗éĆ(g©©)ĘŪ═ą╣▄Ą─Tcl─_▒ŠĪŻ Tcl─_▒Š║═XDC╬─╝■Ą─╝ė▌dĒśą“┼cVivado IDEųą’@╩ŠĄ─Ēśą“ŽÓ═¼Ż©╚ń╣¹╦³éāī┘ė┌═¼ę╗éĆ(g©©)PROCESSING_ORDERĮMŻ®╗“├³┴Ņreport_compile_order -constraintsł¾(b©żo)ĖµĄ─Ēśą“ĪŻ

╚ń╣¹ąĶ꬯¼┐╔ęįį┌ČÓéĆ(g©©)╝s╩°╝»ųą╩╣ė├XDC╬─╝■╗“Tcl─_▒ŠĪŻ ėąĻP(gu©Īn)╚ń║╬×ķĒŚ(xi©żng)─┐äō(chu©żng)Į©║═╠Ē╝ė╝s╩°╬─╝■║═╝s╩°╝»Ą─Ė³ČÓą┼ŽóŻ¼šł(q©½ng)ģóķåĪ░Vivado Design Suiteė├æ¶ųĖ─ŽĪ▒ųąĄ─╩╣ė├╝s╩°Ż║ŽĄĮy(t©»ng)╝ē(j©¬)įO(sh©©)ėŗ(j©¼)

ģó┘Éū„ŲĘŻ©UG895Ż®[ģó┐╝╬─½I(xi©żn)2]ĪŻ

ĘŪĒŚ(xi©żng)─┐┴„│╠

į┌ĘŪĒŚ(xi©żng)─┐─Ż╩ĮŽ┬Ż¼▒žĒÜį┌ł╠(zh©¬)ąąŠÄūg├³┴Ņų«Ū░å╬¬Ü(d©▓)ūx╚Ī├┐éĆ(g©©)╬─╝■ĪŻ

Ž┬├µĄ─╩Š└²─_▒Š’@╩Š┴╦╚ń║╬╩╣ė├ę╗éĆ(g©©)╗“ČÓéĆ(g©©)XDC╬─╝■▀M(j©¼n)ąąŠC║Ž║═īŹ(sh©¬)¼F(xi©żn)ĪŻ

╩Š└²─_▒ŠŻ║

read_verilog [glob src / * .v]

read_xdc wave_gen_timing.xdc

read_xdc wave_gen_pins.xdc

synth_design -top wave_gen -part xc7k325tffg900-2

opt_design

place_design

route_design

šZ(y©│)Š│═Ō╝s╩°

į┌HD╗“PR┴„ųąŻ¼═©│Żęį╔ŽŽ┬╬─Ż©OOCŻ®ĘĮĘ©║Ž│╔įO(sh©©)ėŗ(j©¼)Ą─Ė„▓┐ĘųĪŻ «ö(d©Īng)╩╣ė├▀@śėĄ─┴„Ģr(sh©¬)Ż¼┐╔ęįāH×ķOOC║Ž│╔ųĖČ©ę╗ą®╝s╩°ĪŻ └²╚ńŻ¼«ö(d©Īng)ēK║Ž│╔OOCĢr(sh©¬)Ż¼▒žĒÜČ©┴xį┌ēKĄ─▌ö╚ļ▀ģĮń╠Äé„▓źĄ─Ģr(sh©¬)ńŖĪŻ ▀@ą®Ģr(sh©¬)ńŖį┌OOC XDC╬─╝■ųąČ©┴xĪŻ

In Project Mode:

add_file constraints_ooc.xdc

set_property USED_IN {synthesis out_of_context} [get_files constraints_ooc.xdc]

The Out-of-Context can also be set on the XDC file through the GUI (property on file

constraints_ooc.xdc).

ę▓┐╔ęį═©▀^(gu©░)GUIŻ©╬─╝■constraints_ooc.xdc╔ŽĄ─ī┘ąįŻ®į┌XDC╬─╝■╔ŽįO(sh©©)ų├Out-of-ContextĪŻ

In Non-Project Mode:

read_xdc -mode out_of_context constraints_ooc.xdc

Synthesis and Implementation Constraint Files

By default, all XDC files and Tcl scripts added to a constraint set are used for both synthesis

and implementation. Set the USED_IN_SYNTHESIS and USED_IN_IMPLEMENTATION

properties on the XDC file or the Tcl script to change this behavior. This property can take

the value of either TRUE or FALSE.

║Ž│╔║═īŹ(sh©¬)¼F(xi©żn)╝s╩°╬─╝■

─¼šJ(r©©n)ŪķørŽ┬Ż¼╠Ē╝ėĄĮ╝s╩°╝»Ą─╦∙ėąXDC╬─╝■║═Tcl─_▒ŠČ╝ė├ė┌║Ž│╔║═īŹ(sh©¬)¼F(xi©żn)ĪŻ į┌XDC╬─╝■╗“Tcl─_▒Š╔ŽįO(sh©©)ų├USED_IN_SYNTHESIS║═USED_IN_IMPLEMENTATIONī┘ąįęįĖ³Ė─┤╦ąą×ķĪŻ ┤╦ī┘ąį┐╔ęį▓╔ė├TRUE╗“FALSEĄ─ųĄĪŻ

ųžę¬ą┼ŽóŻ║DONT_TOUCHī┘ąį▓╗ū±čŁUSED_IN_SYNTHESIS║═USED_IN_IMPLEMENTATIONĄ─ī┘ąįĪŻ ╚ń╣¹į┌║Ž│╔XDCųą╩╣ė├DONT_TOUCHī┘ąįŻ¼ät×ķ

¤o(w©▓)šōUSED_IN_IMPLEMENTATIONĄ─ųĄ╚ń║╬Ż¼Č╝Ģ■(hu©¼)é„▓źĄĮīŹ(sh©¬)¼F(xi©żn)ųąĪŻ ėąĻP(gu©Īn)DONT_TOUCHī┘ąįĄ─Ė³ČÓą┼ŽóŻ¼šł(q©½ng)ģóķåRTLī┘ąįŻ¼Ą┌58Ēō(y©©)Ż¼▀@┐╔─▄╩ŪūŅąĶę¬ūóęŌĄ─ĄžĘĮ

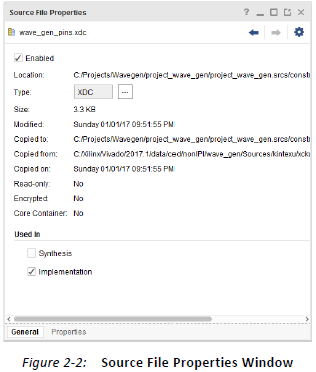

For example, to use a constraint file for implementation only:

1. Select the constraint file in the Sources window.

2. In the Source File Properties window:

a. Uncheck Synthesis.

b. Check Implementation.

The equivalent Tcl commands are:

set_property USED_IN_SYNTHESIS false [get_files wave_gen_pins.xdc]

set_property USED_IN_IMPLEMENTATION true [get_files wave_gen_pins.xdc]

When running the Vivado IDE in Non-Project Mode, you can read in the constraints directly

between any steps of the flow. The properties USED_IN_SYNTHESIS and

USED_IN_IMPLEMENTATION do not matter in this mode.

į┌ĘŪĒŚ(xi©żng)─┐─Ż╩ĮŽ┬▀\(y©┤n)ąąVivado IDEĢr(sh©¬)Ż¼─·┐╔ęįų▒Įėį┌┴„Ą─╚╬║╬▓Į¾Eų«ķgūx╚Ī╝s╩°ĪŻ į┌┤╦─Ż╩ĮŽ┬Ż¼ī┘ąįUSED_IN_SYNTHESIS║═USED_IN_IMPLEMENTATION¤o(w©▓)ĻP(gu©Īn)Šoę¬ĪŻ

The following compilation Tcl script shows how to read two XDC files for different steps of

the flow:

ęįŽ┬ŠÄūgTcl─_▒Š’@╩Š┴╦╚ń║╬ūx╚Ī▓╗═¼▓Į¾EĄ─ā╔éĆ(g©©)XDC╬─╝■

┴„│╠Ż║

read_verilog [glob src/*.v]

read_xdc wave_gen_timing.xdc

synth_design -top wave_gen -part xc7k325tffg900-2

read_xdc wave_gen_pins.xdc

opt_design

place_design

route_design

Ordering Your Constraints

Because XDC constraints are applied sequentially, and are prioritized based on clear

precedence rules, you must review the order of your constraints carefully. For more

information, see Chapter 7, XDC Precedence.

ė╔ė┌XDC╝s╩°╩Ū░┤Ēśą“æ¬(y©®ng)ė├Ą─Ż¼▓óŪę╗∙ė┌├„┤_Ą─ā×(y©Łu)Ž╚╝ē(j©¬)ęÄ(gu©®)ät▀M(j©¼n)ąąā×(y©Łu)Ž╚╝ē(j©¬)┼┼ą“Ż¼ę“┤╦▒žĒÜūą╝Ü(x©¼)Öz▓ķ╝s╩°Ą─Ēśą“ĪŻ ėąĻP(gu©Īn)Ė³ČÓą┼ŽóŻ¼šł(q©½ng)ģóęŖĄ┌7š┬Ż¼XDCā×(y©Łu)Ž╚╝ē(j©¬)

ūóęŌŻ║╚ń╣¹ČÓéĆ(g©©)╬’└Ē╝s╩°░l(f©Ī)╔·ø_═╗Ż¼ätūŅą┬╝s╩°īó½@ä┘ĪŻ └²╚ńŻ¼╚ń╣¹I / OČ╦┐┌═©▀^(gu©░)ČÓéĆ(g©©)XDC╬─╝■Ęų┼õ┴╦▓╗═¼Ą─╬╗ų├Ż©LOCŻ®Ż¼ät×ķūŅą┬╬╗ų├

Ęų┼õĮoČ╦┐┌ā×(y©Łu)Ž╚ĪŻ

The Vivado IDE provides full visibility into your design. To validate your constraints step by

step:

Vivado IDE┐╔╚½├µ┴╦ĮŌ─·Ą─įO(sh©©)ėŗ(j©¼)ĪŻ ę¬ų▓Į“×(y©żn)ūC─·Ą─╝s╩°Ż║

1. Run the appropriate report commands.

2. Review the messages in the Tcl Console or the Messages window.

Į©ūhŻ║¤o(w©▓)šō╩Ū×ķįO(sh©©)ėŗ(j©¼)╩╣ė├ę╗éĆ(g©©)▀Ć╩ŪČÓéĆ(g©©)XDC╬─╝■Ż¼Č╝░┤ęįŽ┬Ēśą“ĮM┐Ś╝s╩°ĪŻ

## Timing Assertions Section # Primary clocks # Virtual clocks # Generated clocks # Clock Groups # Bus Skew constraints # Input and output delay constraints ## Timing Exceptions Section # False Paths # Max Delay / Min Delay # Multicycle Paths # Case Analysis # Disable Timing ## Physical Constraints Section # located anywhere in the file, preferably before or after the timing constraints # or stored in a separate constraint file

Note: The case analysis constraints that change the clock relationships or clock propagation should

be defined prior to defining the generated clocks. This includes cases analysis defined on clock

buffers that result in the output clock of the buffer to be impacted by the case analysis.

ūóŻ║æ¬(y©®ng)į┌Č©┴x╔·│╔Ą─Ģr(sh©¬)ńŖų«Ū░Č©┴xĖ³Ė─Ģr(sh©¬)ńŖĻP(gu©Īn)ŽĄ╗“Ģr(sh©¬)ńŖé„▓źĄ─░Ė└²Ęų╬÷╝s╩°ĪŻ ▀@░³└©į┌Ģr(sh©¬)ńŖ╔ŽČ©┴xĄ─░Ė└²Ęų╬÷

ŠÅø_ģ^(q©▒)ī¦(d©Żo)ų┬ŠÅø_ģ^(q©▒)Ą─▌ö│÷Ģr(sh©¬)ńŖ╩▄ĄĮ░Ė└²Ęų╬÷Ą─ė░ĒæĪŻ

Start with the clock definitions. The clocks must be created before they can be used by any

subsequent constraints. Any reference to a clock before it has been declared results in an

error and the corresponding constraint is ignored. This is true within an individual

constraint file, as well as across all the XDC files (or Tcl scripts) in your design.

The order of the constraint files matters. You must be sure that the constraints in each file

do not rely on the constraints of another file. If this is the case, you must read the file that

contains the constraint dependencies last. If two constraint files have interdependencies,

you must either merge them manually into one file that contains the proper sequence, or

divide the files into several separate files and order them correctly.

Å─Ģr(sh©¬)ńŖČ©┴xķ_╩╝ĪŻ ▒žĒÜŽ╚äō(chu©żng)Į©Ģr(sh©¬)ńŖŻ¼╚╗║¾▓┼─▄īó╦³éāė├ė┌╚╬║╬║¾└m(x©┤)╝s╩°ĪŻ ┬Ģ├„ų«Ū░ī”(du©¼)Ģr(sh©¬)ńŖĄ─╚╬║╬ę²ė├Č╝Ģ■(hu©¼)ī¦(d©Żo)ų┬Õe(cu©░)š`Ż¼▓ó║÷┬įŽÓæ¬(y©®ng)Ą─╝s╩°ĪŻ į┌å╬éĆ(g©©)╝s╩°╬─╝■ųąęį╝░įO(sh©©)ėŗ(j©¼)ųąĄ─╦∙ėąXDC╬─╝■Ż©╗“Tcl─_▒ŠŻ®ųąČ╝╩Ū╚ń┤╦ĪŻ

Å─Ģr(sh©¬)ńŖČ©┴xķ_╩╝ĪŻ ▒žĒÜŽ╚äō(chu©żng)Į©Ģr(sh©¬)ńŖŻ¼╚╗║¾▓┼─▄īó╦³éāė├ė┌╚╬║╬║¾└m(x©┤)╝s╩°ĪŻ ┬Ģ├„ų«Ū░ī”(du©¼)Ģr(sh©¬)ńŖĄ─╚╬║╬ę²ė├Č╝Ģ■(hu©¼)ī¦(d©Żo)ų┬Õe(cu©░)š`Ż¼▓ó║÷┬įŽÓæ¬(y©®ng)Ą─╝s╩°ĪŻ

į┌å╬éĆ(g©©)╝s╩°╬─╝■ųąęį╝░įO(sh©©)ėŗ(j©¼)ųąĄ─╦∙ėąXDC╬─╝■Ż©╗“Tcl─_▒ŠŻ®ųąČ╝╩Ū╚ń┤╦ĪŻ

╝s╩°╬─╝■Ą─Ēśą“║▄ųžę¬ĪŻ ─·▒žĒÜ┤_▒Ż├┐éĆ(g©©)╬─╝■ųąĄ─╝s╩°▓╗ę└┘ćė┌┴Ēę╗éĆ(g©©)╬─╝■Ą─╝s╩°ĪŻ ╚ń╣¹╩Ū▀@ĘNŪķørŻ¼ät▒žĒÜūŅ║¾ūx╚Ī░³║¼╝s╩°ę└┘ćĒŚ(xi©żng)Ą─╬─╝■ĪŻ

╚ń╣¹ā╔éĆ(g©©)╝s╩°╬─╝■Š▀ėąŽÓ╗źę└┘ćĻP(gu©Īn)ŽĄŻ¼ät▒žĒÜīó╦³éā╩ųäė(d©░ng)║Ž▓óĄĮę╗éĆ(g©©)░³║¼š²┤_ą“┴ąĄ─╬─╝■ųąŻ¼╗“š▀īó╬─╝■Ęų│╔ÄūéĆ(g©©)å╬¬Ü(d©▓)Ą─╬─╝■▓óš²┤_┼┼ą“ĪŻ

Constraints Sequence Editing

The Vivado IDE constraints manager saves any edited constraint back to its original location

in the XDC files, but not in Tcl scripts. Any new constraint is saved at the end of the XDC file

marked as target. In many cases, when your constraints set contains several XDC files, the

target constraint file is not the last file in the list, and will not be loaded last when opening

or reloading your design. As a consequence, the constraints sequence saved on disk can be

different from the one you had previously in memory.

Vivado IDE╝s╩°╣▄└ĒŲ„īó╚╬║╬ęčŠÄ▌ŗĄ─╝s╩°▒Ż┤µ╗žXDC╬─╝■ųąĄ─įŁ╩╝╬╗ų├Ż¼Ą½▓╗Ģ■(hu©¼)▒Ż┤µį┌Tcl─_▒ŠųąĪŻ ╚╬║╬ą┬╝s╩°Č╝▒Ż┤µį┌ś╦(bi©Īo)ėø×ķ─┐ś╦(bi©Īo)Ą─XDC╬─╝■Ą──®╬▓ĪŻ į┌įSČÓŪķørŽ┬Ż¼«ö(d©Īng)╝s╩°╝»░³║¼ČÓéĆ(g©©)XDC╬─╝■Ģr(sh©¬)Ż¼─┐ś╦(bi©Īo)╝s╩°╬─╝■▓╗╩Ū┴ą▒ĒųąĄ─ūŅ║¾ę╗éĆ(g©©)╬─╝■Ż¼▓óŪęį┌┤“ķ_╗“ųžą┬╝ė▌dįO(sh©©)ėŗ(j©¼)Ģr(sh©¬)▓╗Ģ■(hu©¼)ūŅ║¾╝ė▌dĪŻ ę“┤╦Ż¼▒Ż┤µį┌┤┼▒P╔ŽĄ─╝s╩°ą“┴ą┐╔─▄┼cų«Ū░į┌ā╚(n©©i)┤µųąĄ─╝s╩°ą“┴ą▓╗═¼ĪŻ

IMPORTANT: You must verify that the final sequence stored in the constraint files still works as

expected. If you must modify the sequence, you must modify it by directly editing the constraint files.

This is especially important for timing constraints

ųžę¬ą┼ŽóŻ║─·▒žĒÜ“×(y©żn)ūC┤µā”(ch©│)į┌╝s╩°╬─╝■ųąĄ─ūŅĮKą“┴ą╩Ūʱ╚į░┤ŅA(y©┤)Ų┌╣żū„ĪŻ ╚ń╣¹▒žĒÜą▐Ė─ą“┴ąŻ¼ät▒žĒÜ═©▀^(gu©░)ų▒ĮėŠÄ▌ŗ╝s╩°╬─╝■üĒ(l©ói)ą▐Ė─╦³ĪŻ ▀@ī”(du©¼)Ģr(sh©¬)ą“╝s╩°ė╚×ķųžę¬ĪŻ

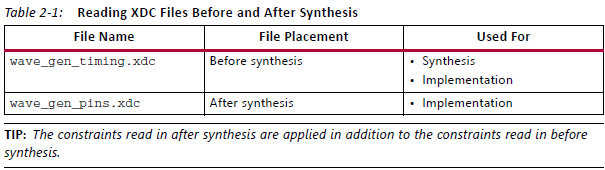

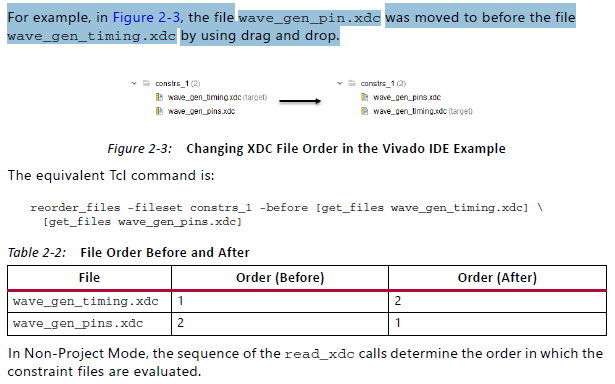

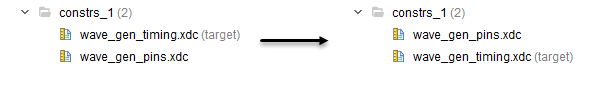

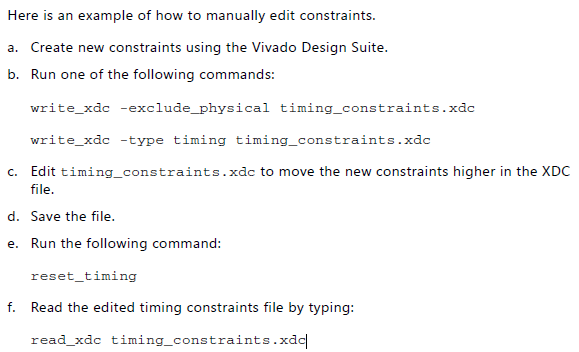

For example, in Figure 2-3, the file wave_gen_pin.xdc was moved to before the file

wave_gen_timing.xdc by using drag and drop.

į┌ø]ėą╚╬║╬IPĄ─ĒŚ(xi©żng)─┐┴„│╠ųąŻ¼╦∙ėą╝s╩°Č╝╬╗ė┌╝s╩°╝»ųąĪŻ ─¼šJ(r©©n)ŪķørŽ┬Ż¼Vivado IDEųą’@╩ŠĄ─XDC╬─╝■Ż©╗“Tcl─_▒ŠŻ®Ą─Ēśą“Č©┴x┴╦īóelaborated design╗“synthesized design╝ė▌dĄĮā╚(n©©i)┤µĢr(sh©¬)╣żŠ▀╩╣ė├Ą─ūx╚ĪĒśą“ĪŻ ╩ūŽ╚ūx╚Ī┴ą▒ĒĒö▓┐Ą─╬─╝■Ż¼ūŅ║¾ūx╚ĪĄū▓┐Ą─╬─╝■ĪŻ ─·ų╗ąĶį┌IDEųą▀xō±╬─╝■▓óīóŲõęŲäė(d©░ng)ĄĮ┴ą▒ĒųąĄ─╦∙ąĶ╬╗ų├╝┤┐╔Ė³Ė─Ēśą“ĪŻ

└²╚ńŻ¼į┌łD1ųąŻ¼╩╣ė├═ŽĘ┼▓┘ū„īó╬─╝■wave_gen_pin.xdcęŲäė(d©░ng)ĄĮ╬─╝■wave_gen_timing.xdcų«Ū░ĪŻ

Figure 1: Changing XDC File Order in the Vivado IDE Example

The equivalent Tcl command is:

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] [get_files wave_gen_pins.xdc]

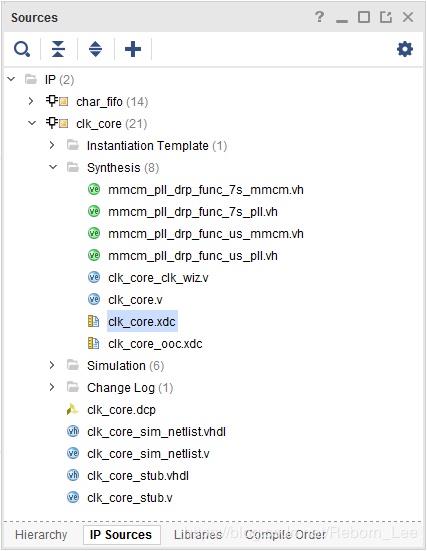

Figure 2: XDC Files in the IP Sources

Figure 1: Changing XDC File Order in the Vivado IDE Example

The equivalent Tcl command is:

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] [get_files wave_gen_pins.xdc]

į┌ĘŪĒŚ(xi©żng)─┐─Ż╩ĮŽ┬Ż¼read_xdcš{(di©żo)ė├Ą─Ēśą“øQČ©┴╦╝s╩°╬─╝■Ą─ėŗ(j©¼)╦ŃĒśą“ĪŻ

Constraint Files Order with IP Cores

įSČÓIPā╚(n©©i)║╦ļSĖĮę╗éĆ(g©©)╗“ČÓéĆ(g©©)XDC╬─╝■ĪŻ į┌RTLĒŚ(xi©żng)─┐ųą╔·│╔┤╦ŅÉIPā╚(n©©i)║╦Ģr(sh©¬)Ż¼▀ĆĢ■(hu©¼)į┌Ė„ĘNįO(sh©©)ėŗ(j©¼)ŠÄūg▓Į¾Eųą╩╣ė├ŲõXDC╬─╝■ĪŻ

└²╚ńŻ¼łD2’@╩ŠĒŚ(xi©żng)─┐ųąĄ─ę╗éĆ(g©©)IP║╦Ħėąę╗éĆ(g©©)XDC╬─╝■ĪŻ

Figure 2: XDC Files in the IP Sources

─¼šJ(r©©n)ŪķørŽ┬Ż¼į┌ė├æ¶XDC╬─╝■ų«Ū░ūx╚ļIP XDC╬─╝■ĪŻ ęį▀@ĘNĘĮ╩Į╠Ä└Ē╦³į╩įSIPäō(chu©żng)Į©┐╔į┌XDCųąę²ė├Ą─Ģr(sh©¬)ńŖī”(du©¼)Ž¾ĪŻ ╦³▀Ćį╩įS─·Ė▓╔wė╔IPā╚(n©©i)║╦įO(sh©©)ų├Ą─╬’└Ē╝s╩°Ż¼ę“?y©żn)ķį┌IPų«║¾įu(p©¬ng)╣└ė├æ¶╝s╩°ĪŻ ī”(du©¼)ė┌ę└┘ćė┌ė╔ė├æ¶╗“Ųõ╦¹IPäō(chu©żng)Į©Ą─Ģr(sh©¬)ńŖī”(du©¼)Ž¾Ą─IP║╦Ż¼┤╦Ēśą“ėąę╗éĆ(g©©)└²═ŌŻ©└²╚ńŻ¼get_clocks -of_objects [get_ports clka]Ż®ĪŻ į┌▀@ĘNŪķørŽ┬Ż¼į┌ė├æ¶╬─╝■ų«║¾ūx╚ĪIP XDCĪŻ

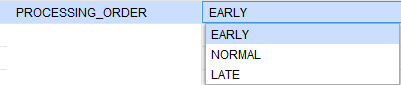

┤╦ąą×ķė╔PROCESSING_ORDERī┘ąį┐žųŲŻ¼×ķ├┐éĆ(g©©)XDC╬─╝■įO(sh©©)ų├Ż║

•EARLYŻ║▒žĒÜŽ╚ūx╚ĪĄ─╬─╝■

•NORMALŻ║─¼šJ(r©©n)

•LATEŻ║▒žĒÜūŅ║¾ūx╚ĪĄ─╬─╝■

IP XDCīóŲõPROCESSING_ORDERī┘ąįįO(sh©©)ų├×ķEARLY╗“LATEĪŻ ø]ėą──éĆ(g©©) IP╠ß╣®ī┘ė┌NORMAL╝s╩°ĮMĄ─XDC╬─╝■ĪŻ ī”(du©¼)ė┌ī┘ė┌═¼ ę╗PROCESSING_ORDERĮMĄ─ė├æ¶XDCŻ©╗“TclŻ®╬─╝■Ż¼Vivado IDEųą’@╩ŠĄ─ŽÓī”(du©¼)Ēśą“øQČ©┴╦╦³éāĄ─ūx╚ĪĒśą“ĪŻ ┐╔ęį═©▀^(gu©░)ęŲäė(d©░ng)Vivado IDE╝s╩°╝»ųąĄ─╬─╝■╗“╩╣ė├reorder_files├³┴ŅüĒ(l©ói)ą▐Ė─ĮMųąĄ─Ēśą“ĪŻ

ī”(du©¼)ė┌ī┘ė┌═¼ę╗PROCESSING_ORDERĮMĄ─IP XDC╬─╝■Ż¼Ēśą“ė╔IPā╚(n©©i)║╦Ą─ī¦(d©Żo)╚ļ╗“äō(chu©żng)Į©Ēśą“┤_Č©ĪŻ äō(chu©żng)Į©ĒŚ(xi©żng)─┐║¾Ż¼¤o(w©▓)Ę©Ė³Ė─┤╦Ēśą“ĪŻ

ūŅ║¾Ż¼ė├æ¶ĮM║═IP XDC PROCESSING_ORDERĮMų«ķgĄ─ŽÓī”(du©¼)Ēśą“╚ńŽ┬Ż║

1.ś╦(bi©Īo)ėø×ķEARLYĄ─ė├æ¶╝s╩°

2.ś╦(bi©Īo)ėø×ķEARLYĄ─IP╝s╩°Ż©─¼šJ(r©©n)Ż®

3.ś╦(bi©Īo)ėø×ķNORMALĄ─ė├æ¶╝s╩°

4.ś╦(bi©Īo)ėø×ķL(zh©Żng)ATEĄ─IP╝s╩°Ż©░³║¼Ģr(sh©¬)ńŖę└┘ćąįŻ®

5.ś╦(bi©Īo)ėø×ķL(zh©Żng)ATEĄ─ė├æ¶╝s╩°

ūóęŌŻ║īóŲõPROCESSING_ORDERįO(sh©©)ų├×ķL(zh©Żng)ATEŻ©ęį▒Ńį┌ė├æ¶╝s╩°║¾▀M(j©¼n)ąą╠Ä└ĒŻ®Ą─IP XDC╬─╝■├³├¹×ķ<IP_NAME> _clocks.xdcĪŻ

Ž┬łD’@╩Š┴╦╚ń║╬įO(sh©©)ų├PROCESSING_ORDERī┘ąįĄ─╩Š└²Ż║

Figure 3: Setting the XDC File PROCESSING_ORDER Example

The equivalent Tcl command is:

set_property PROCESSING_ORDER EARLY [get_files wave_gen_pins.xdc]

Į©ūhŻ║╩╣ė├Tcl┐žųŲ┼_(t©ói)ųąĄ─report_compile_order -constraints├³┴Ņł¾(b©żo)Ėµė╔╣żŠ▀Ė∙ō■(j©┤)╔Ž╩÷ī┘ąį┤_Č©Ą─XDC╬─╝■ūx╚ĪĒśą“Ż¼░³└©IS_ENABLEDŻ¼USED_IN_SYNTHESIS║═USED_IN_IMPLEMENTATIONĪŻ

Changing Read Order

ę¬į┌╝s╩°╝»ųąĖ³Ė─XDC╬─╝■╗“ĘŪ═ą╣▄Tcl─_▒ŠĄ─ūx╚ĪĒśą“Ż¼šł(q©½ng)ł╠(zh©¬)ąąęįŽ┬▓┘ū„Ż║

1.į┌Ī░į┤Ī▒┤░┐┌ųąŻ¼▀xō±ę¬ęŲäė(d©░ng)Ą─XDC╬─╝■╗“Tcl─_▒ŠĪŻ

2.īó╬─╝■═ŽĘ┼ĄĮ╝s╩°╝»ųąĄ─╦∙ąĶ╬╗ų├ĪŻ

ī”(du©¼)ė┌łD1ųą╦∙╩ŠĄ─╩Š└²Ż¼Ą╚ą¦Ą─Tcl├³┴Ņ╩ŪŻ║

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] [get_files wave_gen_pins.xdc]

į┌ĘŪĒŚ(xi©żng)─┐─Ż╩ĮŽ┬Ż¼read_xdc╗“source├³┴ŅĄ─Ēśą“øQČ©┴╦╝s╩°╬─╝■Ą─ūx╚ĪĒśą“ĪŻ

╚ń╣¹╩╣ė├Ħėą╝s╩°Ą─IPā╚(n©©i)║╦Ż¼ätĢ■(hu©¼)ūįäė(d©░ng)╠Ä└Ēā╔ĮM╝s╩°Ż¼╚ńŽ┬╦∙╩ŠŻ║

•▓╗ę└┘ćė┌Ģr(sh©¬)ńŖĄ─╝s╩°▒╗ĘųĮMĄĮXDC╬─╝■ųąŻ¼PROCESSING_ORDERįO(sh©©)ų├×ķEARLYŻ¼

•ę└┘ćė┌Ģr(sh©¬)ńŖĄ─╝s╩°į┌PROCESSING_ORDERįO(sh©©)ų├×ķL(zh©Żng)ATEĄ─XDC╬─╝■ųąĘųĮMĪŻ

─¼šJ(r©©n)ŪķørŽ┬Ż¼ė├æ¶XDC╬─╝■ī┘ė┌PROCESSING_ORDER NORMALĮMĪŻ ╦³éā?c©©)┌EARLY XDC╬─╝■ų«║¾║═LATE XDC╬─╝■ų«Ū░╝ė▌dĪŻ ī”(du©¼)ė┌├┐éĆ(g©©)PROCESSING_ORDERĮMŻ¼IP XDC╬─╝■Ą─╝ė▌dĒśą“┼cIP Sources┤░┐┌ųąIP║╦Ą─┴ą▒ĒĒśą“ŽÓ═¼ĪŻ └²╚ńŻ¼Ž┬łD’@╩Š┴╦XDC╬─╝■ĖĮĦĄ─ĒŚ(xi©żng)─┐IPā╚(n©©i)║╦ų«ę╗ĪŻ

Figure 4: XDC Files in the IP Sources

┤“ķ_įO(sh©©)ėŗ(j©¼)Ģr(sh©¬)Ż¼╚šųŠ╬─╝■’@╩ŠūŅ║¾╝ė▌d┴╦IP XDC╬─╝■Ż║ Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/clk_core/clk_core.xdc] for cell 'clk_gen_i0/clk_core_i0/inst' Finished Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/clk_core/clk_core.xdc] for cell 'clk_gen_i0/clk_core_i0/inst' Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo.xdc] for cell 'char_fifo_i0/U0' Finished Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo.xdc] for cell 'char_fifo_i0/U0' Parsing XDC File [C:/project_wave_gen_hdl.srcs/constrs_1/imports/verilog/wave_gen_timing.xdc] Finished Parsing XDC File [C:/project_wave_gen_hdl.srcs/constrs_1/imports/verilog/wave_gen_timing.xdc] Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo_clocks.xdc ] for cell 'char_fifo_i0/U0' Finished Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo_clocks.xdc ] for cell 'char_fifo_i0/U0' Completed Processing XDC Constraints

┼cė├æ¶XDC╬─╝■▓╗═¼Ż¼─·¤o(w©▓)Ę©ų▒ĮėĖ³Ė─ī┘ė┌═¼ę╗PROCESSING_ORDERĮMĄ─IP XDC╬─╝■Ą─ūx╚ĪĒśą“ĪŻ ╚ń╣¹▒žĒÜą▐Ė─ėåå╬Ż¼šł(q©½ng)ł╠(zh©¬)ąąęįŽ┬▓┘ū„Ż║

1.Į¹ė├ŽÓæ¬(y©®ng)Ą─IP XDC╬─╝■Ż©IS_ENABLEDįO(sh©©)ų├×ķfalseŻ®ĪŻ

2.Å═(f©┤)ųŲ╦¹éāĄ─ā╚(n©©i)╚▌ĪŻ

3.īóā╚(n©©i)╚▌š│┘NĄĮ╝s╩°╝»ųą░³║¼Ą─ę╗éĆ(g©©)XDC╬─╝■ųąĪŻ

4.į┌ąĶꬥ─ĄžĘĮ╩╣ė├═Ļš¹Ą─ĘųīėŠW(w©Żng)▒Ēī”(du©¼)Ž¾┬ĘÅĮ├¹Ė³ą┬Å═(f©┤)ųŲĄ─IP XDC├³┴ŅĪŻ ▀@śėū÷╩Ū▒žąĶĄ─Ż¼ę“?y©żn)ķIP XDC╝s╩°ęį▀@śėĄ─ĘĮ╩ĮŠÄīæŻ¼╝┤╦³éā┐╔ęįū„ė├ė┌IPīŹ(sh©¬)└²ĪŻ

5.▓ķ┐┤ęį╠ž╩ŌĘĮ╩Į╠Ä└ĒĘČć·╝s╩°Ą─get_ports▓ķįāĪŻ

Entering Constraints

The Vivado IDE provides several ways to enter constraints. Unless you directly edit the XDC

file in a text editor, you must open a design database (elaborated, synthesized or

implemented) in order to access the constraints windows in the Vivado IDE.

Vivado IDE╠ß╣®┴╦ÄūĘN▌ö╚ļ╝s╩°Ą─ĘĮĘ©ĪŻ │²ĘŪ─·į┌╬─▒ŠŠÄ▌ŗŲ„ųąų▒ĮėŠÄ▌ŗXDC╬─╝■Ż¼Ę±ät▒žĒÜ┤“ķ_įO(sh©©)ėŗ(j©¼)öĄ(sh©┤)ō■(j©┤)Äņ(k©┤)Ż©įö╝Ü(x©¼)šf(shu©Ł)├„Ż¼ŠC║Ž╗“?q©▒)Ź¼F(xi©żn)Ż®▓┼─▄įLå¢Vivado IDEųąĄ─╝s╩°┤░┐┌ĪŻ

Saving Constraints in Memory

You must have a design in memory to validate your constraints during editing. When you

edit a constraint using the Vivado IDE user interface, the equivalent XDC command is issued

in the Tcl Console in order to apply it in memory. An edited timing constraint must be

applied in memory before it can be saved to the XDC file.

Before you can run synthesis or implementation, you must save the constraints in memory

back to an XDC file that belongs to the project. The Vivado IDE prompts you to save your

constraints whenever necessary.

─·▒žĒÜį┌ā╚(n©©i)┤µųąįO(sh©©)ėŗ(j©¼)ę╗éĆ(g©©)įO(sh©©)ėŗ(j©¼)▓┼─▄į┌ŠÄ▌ŗŲ┌ķg“×(y©żn)ūC─·Ą─╝s╩°ĪŻ ╩╣ė├Vivado IDEė├æ¶Įń├µŠÄ▌ŗ╝s╩°Ģr(sh©¬)Ż¼īóį┌Tcl┐žųŲ┼_(t©ói)ųą░l(f©Ī)│÷Ą╚ą¦Ą─XDC├³┴ŅŻ¼ęį▒ŃīóŲõæ¬(y©®ng)ė├ė┌ā╚(n©©i)┤µĪŻ ▒žĒÜŽ╚īóęčŠÄ▌ŗĄ─Ģr(sh©¬)ą“╝s╩°æ¬(y©®ng)ė├ė┌ā╚(n©©i)┤µŻ¼╚╗║¾▓┼─▄īóŲõ▒Ż┤µĄĮXDC╬─╝■ųąĪŻŻ©╔ČęŌ╦╝Ż┐īóęčŠÄ▌ŗĄ─Ģr(sh©¬)ą“╝s╩°æ¬(y©®ng)ė├ė┌ā╚(n©©i)┤µ╚╗║¾▓┼─▄▒Ż┤µXDC╬─╝■Ż┐Ż┐Ż┐Ż®

į┌▀\(y©┤n)ąąŠC║Ž╗“?q©▒)Ź¼F(xi©żn)ų«Ū░Ż¼▒žĒÜīóā╚(n©©i)┤µųąĄ─╝s╩°▒Ż┤µ╗žī┘ė┌ĒŚ(xi©żng)─┐Ą─XDC╬─╝■ĪŻ Vivado IDEĢ■(hu©¼)į┌▒žę¬Ģr(sh©¬)╠ß╩Š─·▒Ż┤µ╝s╩°ĪŻ

Do one of the following to save your constraints manually:

ł╠(zh©¬)ąąęįŽ┬▓┘ū„ų«ę╗ęį╩ųäė(d©░ng)▒Ż┤µ╝s╩°Ż║

•å╬ō¶Ī░▒Ż┤µ╝s╩°Ī▒ĪŻ

•▀xō±Ī░╬─╝■Ī▒>Ī░╝s╩°Ī▒>Ī░▒Ż┤µĪ▒ĪŻ

Note: When you save the in-memory constraints, a dialog box opens to remind you that this could

cause the synthesis and implementation to go out of date. Select the Remember Preference check

box on this dialog box to disable future instances of this warning.

ūóęŌŻ║▒Ż┤µā╚(n©©i)┤µųąĄ─╝s╩°Ģr(sh©¬)Ż¼Ģ■(hu©¼)┤“ķ_ę╗éĆ(g©©)ī”(du©¼)įÆ┐“Ż¼╠ßąč─·▀@┐╔─▄ī¦(d©Żo)ų┬║Ž│╔║═īŹ(sh©¬)¼F(xi©żn)▀^(gu©░)Ģr(sh©¬)ĪŻ ▀xųą┤╦ī”(du©¼)įÆ┐“╔ŽĄ─Ī░ėøūĪ╩ū▀xĒŚ(xi©żng)Ī▒Å═(f©┤)▀x┐“ęįĮ¹ė├┤╦Š»ĖµĄ─╬┤üĒ(l©ói)īŹ(sh©¬)└²ĪŻ

When you run these commands, Vivado does the following:

• Saves all new constraints to the XDC file marked target in the constraints set

associated with your design.

• Saves all edited constraints back to the XDC file from which they originated.

Note: The constraints management system preserves the original XDC files format as much as

possible.

▀\(y©┤n)ąą▀@ą®├³┴ŅĢr(sh©¬)Ż¼VivadoĢ■(hu©¼)ł╠(zh©¬)ąąęįŽ┬▓┘ū„Ż║

•īó╦∙ėąą┬╝s╩°▒Ż┤µĄĮ┼cįO(sh©©)ėŗ(j©¼)ĻP(gu©Īn)┬ō(li©ón)Ą─╝s╩°╝»ųąś╦(bi©Īo)ėø×ķ─┐ś╦(bi©Īo)Ą─XDC╬─╝■ĪŻ

•īó╦∙ėąęčŠÄ▌ŗĄ─╝s╩°▒Ż┤µ╗žį┤ūį╦³éāĄ─XDC╬─╝■ĪŻ

ūóęŌŻ║╝s╩°╣▄└ĒŽĄĮy(t©»ng)▒M┐╔─▄▒Ż┴¶įŁ╩╝XDC╬─╝■Ė±╩ĮĪŻ

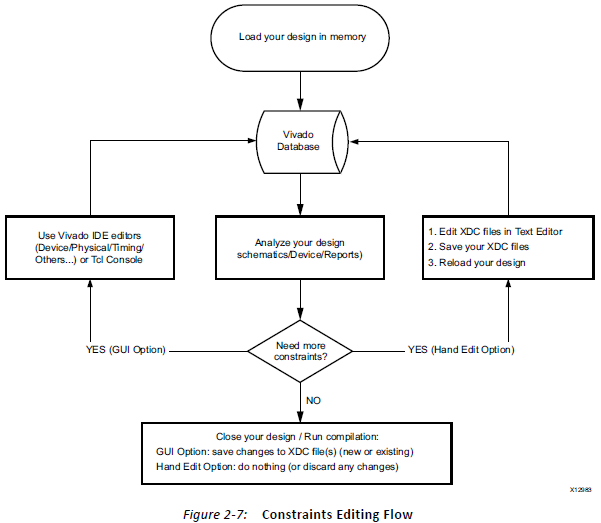

Constraints Editing Flow Options

Figure 2-7 shows the recommended flow options. Do not use both options at the same

time. Mixing these options might cause you to lose constraints. The recommended flow

options are:

łD2-7’@╩Š┴╦═Ų╦]Ą─┴„┴┐▀xĒŚ(xi©żng)ĪŻ ▓╗ę¬═¼Ģr(sh©¬)╩╣ė├▀@ā╔éĆ(g©©)▀xĒŚ(xi©żng)ĪŻ ╗ņ║Ž▀@ą®▀xĒŚ(xi©żng)┐╔─▄Ģ■(hu©¼)ī¦(d©Żo)ų┬─·╩¦╚ź╝s╩°ĪŻ ═Ų╦]Ą─┴„│╠▀xĒŚ(xi©żng)░³└©Ż║

• User Interface Option

• Hand Edit Option

User Interface Option

Because the Vivado IDE manages your constraints, you must not edit your XDC files at the

same time. When the Vivado IDE saves the memory content, the following occurs:

• The modified constraints replace the original constraints in their original file.

• The new constraints are appended to the file marked as target.

• All manual edits in the XDC files are overwritten.

ė├æ¶Įń├µ▀xĒŚ(xi©żng)

ė╔ė┌Vivado IDE╣▄└Ē─·Ą─╝s╩°Ż¼ę“┤╦─·▓╗─▄═¼Ģr(sh©¬)ŠÄ▌ŗXDC╬─╝■ĪŻ «ö(d©Īng)Vivado IDE▒Ż┤µā╚(n©©i)┤µā╚(n©©i)╚▌Ģr(sh©¬)Ż¼Ģ■(hu©¼)░l(f©Ī)╔·ęįŽ┬ŪķørŻ║

•ą▐Ė─Ą─╝s╩°╠µōQįŁ╩╝╬─╝■ųąĄ─įŁ╩╝╝s╩°ĪŻ

•ą┬╝s╩°īóĖĮ╝ėĄĮś╦(bi©Īo)ėø×ķ─┐ś╦(bi©Īo)Ą─╬─╝■ųąĪŻ

•īóĖ▓╔wXDC╬─╝■ųąĄ─╦∙ėą╩ųäė(d©░ng)ŠÄ▌ŗĪŻ

Hand Edit Option

When you use the Hand Edit option, you are in charge of editing and maintaining the XDC

files. While you will probably use the Tcl Console to verify the syntax of some constraints,

you must discard the changes made in memory when closing or reloading your design.

In case of a conflict when saving the constraints, you are prompted to choose one of the

following:

• Discarding the changes made in memory

• Saving the changes in a new file

• Overwriting the XDC files

╩ųŠÄ▌ŗ▀xĒŚ(xi©żng)

╩╣ė├Ī░╩ųäė(d©░ng)ŠÄ▌ŗĪ▒▀xĒŚ(xi©żng)Ģr(sh©¬)Ż¼─·žō(f©┤)ž¤(z©”)ŠÄ▌ŗ║═ŠSūo(h©┤)XDC╬─╝■ĪŻ ļm╚╗─·┐╔─▄Ģ■(hu©¼)╩╣ė├Tcl┐žųŲ┼_(t©ói)üĒ(l©ói)“×(y©żn)ūC─│ą®╝s╩°Ą─šZ(y©│)Ę©Ż¼

ĻP(gu©Īn)ķ]╗“ųžą┬╝ė▌dįO(sh©©)ėŗ(j©¼)Ģr(sh©¬)Ż¼▒žĒÜĘ┼Śēį┌ā╚(n©©i)┤µųą╦∙ū÷Ą─Ė³Ė─ĪŻ

╚ń╣¹į┌▒Ż┤µ╝s╩°Ģr(sh©¬)░l(f©Ī)╔·ø_═╗Ż¼ŽĄĮy(t©»ng)Ģ■(hu©¼)╠ß╩Š─·▀xō±Ųõųąę╗éĆ(g©©)

ęįŽ┬Ż║

•Ę┼Śēį┌ā╚(n©©i)┤µųą▀M(j©¼n)ąąĄ─Ė³Ė─

•īóĖ³Ė─▒Ż┤µį┌ą┬╬─╝■ųą

•Ė▓╔wXDC╬─╝■

Constraints creation is iterative. You can use IDE editors in some cases, and hand edit the

constraint files in others.

į┌łD2-7ųą├Ķ╩÷Ą─├┐┤╬Ą³┤·ųąŻ¼▓╗ę¬═¼Ģr(sh©¬)╩╣ė├▀@ā╔éĆ(g©©)▀xĒŚ(xi©żng)ĪŻ

╚ń╣¹į┌ā╔éĆ(g©©)▀xĒŚ(xi©żng)ų«ķgŪąōQŻ¼ät▒žĒÜŽ╚▒Ż┤µ╝s╩°╗“ųžą┬╝ė▌dįO(sh©©)ėŗ(j©¼)Ż¼ęį┤_▒Żā╚(n©©i)┤µųąĄ─╝s╩°┼cXDC╬─╝■š²┤_═¼▓ĮĪŻ

Pin Assignment

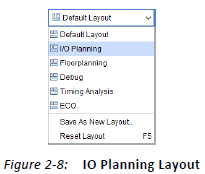

To create and edit existing top-level ports placement when using the RTL Analysis,

Synthesis, or Implementation views:

į┌╩╣ė├RTL AnalysisŻ¼Synthesis╗“ImplementationęĢłDĢr(sh©¬)äō(chu©żng)Į©║═ŠÄ▌ŗ¼F(xi©żn)ėąĄ─Ēö╝ē(j©¬)Č╦┐┌Ę┼ų├Ż║

1. Select the I/O Planning pre-configured layout.

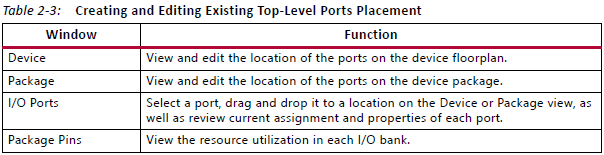

2. Open the windows shown in Table 2-3.

ėąĻP(gu©Īn)ę²─_Ęų┼õĄ─Ė³ČÓą┼ŽóŻ¼šł(q©½ng)ģóķåĪ░Vivado Design Suiteė├æ¶ųĖ─ŽĪ▒ųąĄ─┤╦µ£ĮėŻ║

I / O║═Ģr(sh©¬)ńŖęÄ(gu©®)äØŻ©UG899Ż®[ģó┐╝3]ĪŻ

▓╝ŠųęÄ(gu©®)äØ

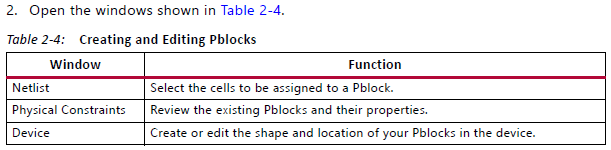

į┌╩╣ė├RTLĘų╬÷Ż¼ŠC║Ž╗“?q©▒)Ź╩®ęĢłDĢr(sh©¬)äō(chu©żng)Į©║═ŠÄ▌ŗPblockŻ║

1.▀xō±▓╝ŠųęÄ(gu©®)äØŅA(y©┤)┼õų├▓╝ŠųĪŻ

To create cell placement constraints on a particular BEL or SITE:

1. Select the cell in the Netlist view.

2. Drag and drop the cell to the target location in the Device view.

ę¬į┌╠žČ©Ą─BEL╗“SITE╔Žäō(chu©żng)Į©å╬į¬Ė±Ę┼ų├╝s╩°Ż║

1.į┌Ī░ŠW(w©Żng)▒ĒĪ▒ęĢłDųą▀xō±å╬į¬Ė±ĪŻ

2.īóå╬į¬Ė±═ŽĘ┼ĄĮĪ░įO(sh©©)éõĪ▒ęĢłDųąĄ──┐ś╦(bi©Īo)╬╗ų├ĪŻ

ėąĻP(gu©Īn)▓╝ŠųęÄ(gu©®)äØĄ─Ė³ČÓą┼ŽóŻ¼šł(q©½ng)ģóķåĪ░Vivado Design Suiteė├æ¶ųĖ─ŽĪ▒ųąĄ─ęįŽ┬µ£ĮėŻ║

įO(sh©©)ėŗ(j©¼)Ęų╬÷║═ĻP(gu©Īn)ķ]╝╝ąg(sh©┤)Ż©UG906Ż®[ģó┐╝╬─½I(xi©żn)4]ĪŻ

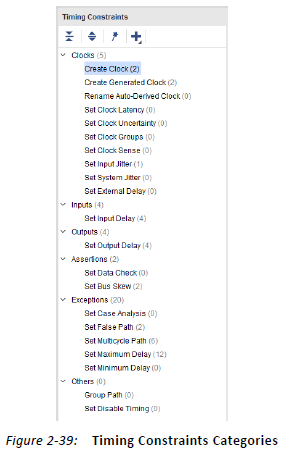

Timing Constraints Wizard

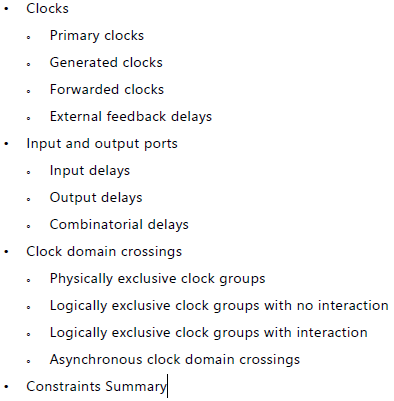

The Timing Constraints Wizard identifies missing timing constraints on a synthesized or

implemented design. It analyzes the netlist, the clock nets connectivity, and the existing

timing constraints in order to provide recommendations as per the UltraFast Design

Methodology Guide for the Vivado Design Suite (UG949) [Ref 5]. Three categories of

constraints are covered by the following 11 pages of the wizard, followed by a summary.

The following steps are included:

Ģr(sh©¬)ą“╝s╩°Ž“?q©▒)?br />Ģr(sh©¬)ą“╝s╩°Ž“?q©▒)¦ūR(sh©¬)äe║Ž│╔╗“?q©▒)Ź¼F(xi©żn)Ą─įO(sh©©)ėŗ(j©¼)╔Ž╚▒╔┘Ą─Ģr(sh©¬)ą“╝s╩°ĪŻ ╦³Ęų╬÷ŠW(w©Żng)▒ĒŻ¼Ģr(sh©¬)ńŖŠW(w©Żng)Įj(lu©░)▀BĮė║═¼F(xi©żn)ėąĄ─Ģr(sh©¬)ą“╝s╩°Ż¼ęį▒ŃĖ∙ō■(j©┤)VivadoįO(sh©©)ėŗ(j©¼)╠ū╝■Ż©UG949Ż®Ą─UltraFastįO(sh©©)ėŗ(j©¼)ĘĮĘ©ųĖ─Ž[ģó┐╝╬─½I(xi©żn)5]╠ß╣®Į©ūhĪŻ Ž“?q©▒)¦Ą─ęįŽ?1Ēō(y©©)░³║¼╚²ŅÉ╝s╩°Ż¼║¾├µ╩Ūš¬ę¬ĪŻ

░³└©ęįŽ┬▓Į¾EŻ║

į┌├┐éĆ(g©©)▓Į¾EųąŻ¼─·┐╔ęįĮė╩▄Į©ūhĄ─╝s╩°╗“═©▀^(gu©░)▀xųą╗“╚ĪŽ¹▀xųą├┐éĆ(g©©)Į©ūhĄ─╝s╩°üĒ(l©ói)ą▐Ė─┴ą▒ĒĪŻ Ą½╩ŪŻ¼į┌Ž“?q©▒)¦Ą─įńŲ┌╚ĪŽ¹▀xųąĮ©ūhĄ─╝s╩°┐╔─▄Ģ■(hu©¼)ūĶų╣į┌║¾└m(x©┤)▓Į¾EųąūR(sh©¬)äeŲõ╦¹╚▒╔┘Ą─╝s╩°ĪŻ └²╚ńŻ¼╚ń╣¹─·øQČ©╠°▀^(gu©░)äō(chu©żng)Į©Ģr(sh©¬)ńŖŻ¼ätŽ“?q©▒)¦īó▓╗Ģ?hu©¼)ūR(sh©¬)äe▓ó═Ų╦]╚╬║╬ę²ė├┤╦Ģr(sh©¬)ńŖ╗“Ųõūįäė(d©░ng)┼╔╔·Ģr(sh©¬)ńŖĄ─╝s╩°ĪŻ

Ž“?q©▒)¦Ą─ūŅ║¾ę╗Ē?y©©)╠ß╣®┴╦īóę¬?ji©Żng)?chu©żng)Į©Ą─╝s╩°Ą─š¬ę¬ĪŻ ─·┐╔ęįå╬ō¶├┐éĆ(g©©)å╬¬Ü(d©▓)Ą─│¼µ£Įėęį▓ķ┐┤╝s╩°įö╝Ü(x©¼)ą┼ŽóŻ¼╗“į┌═╦│÷Ž“?q©▒)¦║¾į┌Ī░Ģr(sh©¬)ą“╝s╩°Ī▒┤░┐┌ųą’@╩Šą┬╝s╩°ĪŻ

─·▀Ć┐╔ęį▀xō±į┌å╬ō¶Ī░═Ļ│╔Ī▒║¾╔·│╔ęįŽ┬Į©ūhĄ─ł¾(b©żo)ĖµŻ¼ęį“×(y©żn)ūCįO(sh©©)ėŗ(j©¼)╩Ūʱ═Ļ╚½╩▄╝s╩°Ż║

Create Timing Summary report: Timing slack is reported with the new constraints, in

addition to a check_timing report. Timing violations will likely display if the period

or I/O delay constraints that you entered are too difficult.

• Create Check Timing report: This report identifies missing or inappropriate

constraints by running the check_timing command.

• Create DRC Report using only Timing Checks: this report runs the Timing DRCs.

ųžę¬ą┼ŽóŻ║│²ĘŪå╬ō¶Ī░╚ĪŽ¹Ī▒Ż¼Ę±ätą┬╠Ē╝ėĄ─╝s╩°īóūįäė(d©░ng)▒Ż┤µĄĮ─┐ś╦(bi©Īo)XDC╬─╝■ųąĪŻ ═╦│÷Ž“?q©▒)¦║¾Ż¼─·┐╔ęįį┌Timing Constraints┤░┐┌ųąŠÄ▌ŗ╗“äh│²ą┬╝s╩°ĪŻ

The Timing Constraint Wizard does not recommend a constraint if it introduces unsafe timing analysis. Also, the wizard does not fix inappropriate constraints that already existed when loading the design in memory. Nevertheless, some invalid constraints might become valid after creating all the missing clocks when using Vivado Design Suite in project mode;

for more details, see Constraints Processing Order and Invalid Constraints, below. Also, after using the wizard, if check_timing or report_drc still flag some constraints issues, it is usually due to a constraint problem that already existed in the source XDC files. You must address these problems directly instead of using the wizard to resolve them.

╚ń╣¹Č©Ģr(sh©¬)╝s╩°Ž“?q©▒)¦ę²╚ļ┴╦▓╗░▓╚½Ą─Ģr(sh©¬)ą“Ęų╬÷Ż¼ät▓╗Į©ūh╩╣ė├╝s╩°ĪŻ ┤╦═ŌŻ¼Ž“?q©▒)¦▓╗Ģ?hu©¼)ą▐Å═(f©┤)į┌ā╚(n©©i)┤µųą╝ė▌dįO(sh©©)ėŗ(j©¼)Ģr(sh©¬)ęč┤µį┌Ą─▓╗▀m«ö(d©Īng)╝s╩°ĪŻ ╚╗Č°Ż¼į┌ĒŚ(xi©żng)─┐─Ż╩ĮŽ┬╩╣ė├Vivado Design SuiteĢr(sh©¬)Ż¼äō(chu©żng)Į©╦∙ėąüG╩¦Ą─Ģr(sh©¬)ńŖ║¾Ż¼─│ą®¤o(w©▓)ą¦╝s╩°┐╔─▄Ģ■(hu©¼)╔·ą¦;

ėąĻP(gu©Īn)Ė³ČÓįö╝Ü(x©¼)ą┼ŽóŻ¼šł(q©½ng)ģóķåŽ┬├µĄ─╝s╩°╠Ä└ĒĒśą“║═¤o(w©▓)ą¦╝s╩°ĪŻ ┤╦═ŌŻ¼į┌╩╣ė├Ž“?q©▒)¦ų«║¾Ż¼╚ń╣¹check_timing╗“report_drc╚įś╦(bi©Īo)ėøę╗ą®╝s╩°å¢Ņ}Ż¼ät═©│Ż╩Ūė╔ė┌į┤XDC╬─╝■ųąęč┤µį┌Ą─╝s╩°å¢Ņ}ĪŻ ─·▒žĒÜų▒ĮėĮŌøQ▀@ą®å¢Ņ}Ż¼Č°▓╗╩Ū╩╣ė├Ž“?q©▒)¦ü?l©ói)ĮŌøQ╦³éāĪŻ

╝s╩°╠Ä└ĒĒśą“║═¤o(w©▓)ą¦╝s╩°

Ģr(sh©¬)ą“╝s╩°Ž“?q©▒)¦Į©ūh╚▒╔┘Č©┴xĢr(sh©¬)ńŖ╗“ę²ė├Ģr(sh©¬)ńŖĄ─╝s╩°Ż¼▀@ą®╝s╩°īóį┌ĒŚ(xi©żng)─┐─Ż╩ĮŽ┬▒Ż┤µį┌─┐ś╦(bi©Īo)XDC╬─╝■Ą──®╬▓Ż¼╗“š▀į┌Ųõ╦¹─Ż╩ĮĄ─╦∙ėą╝s╩°ĮY(ji©”)╩°Ģr(sh©¬)▒Ż┤µĪŻ│÷ė┌▀@éĆ(g©©)įŁę“Ż¼─Ń▒žĒÜ├„░ū

ęįŽ┬ęÄ(gu©®)ätŻ║

•ĒŚ(xi©żng)─┐─Ż╩ĮŻ║į┌åóäė(d©░ng)Ī░ėŗ(j©¼)Ģr(sh©¬)╝s╩°Ī▒Ž“?q©▒)¦ų«Ū░Ż¼▒žĒÜųĖČ©─┐ś?bi©Īo)XDC╬─╝■Ż¼Ųõ╠Ä└ĒĒśą“įO(sh©©)ų├×ķĪ░š²│ŻĪ▒ĪŻ─┐ś╦(bi©Īo)XDC╬─╝■▒žĒÜī┘ė┌į┌ā╚(n©©i)┤µųą┤“ķ_Ūę«ö(d©Īng)Ū░▀xČ©Ą─įO(sh©©)ėŗ(j©¼)Ą─╝s╩°╝»ĪŻ─┐ś╦(bi©Īo)XDC╬─╝■į┌Ųõ╦¹XDC╬─╝■ųąĄ─╬╗ų├║▄ųžę¬Ż¼ę“?y©żn)ķ╦³ųĖČ©┴╦ęį║¾æ?y©®ng)ė├║═▒Ż┤µĮ©ūh╝s╩°Ą─╬╗ų├ĪŻ┤╦═ŌŻ¼Ž“?q©▒)¦Ģ?hu©¼)ćLįćųžą┬æ¬(y©®ng)ė├ī┘ė┌─┐ś╦(bi©Īo)ų«║¾ĮŌ╬÷Ą─XDC╬─╝■Ą─╚╬║╬¤o(w©▓)ą¦╝s╩°

XDC╬─╝■ęį╠ß╣®ūŅ═Ļš¹║═£╩(zh©│n)┤_Ą─Į©ūhĪŻ

└²╚ńŻ¼┐╝æ]üĒ(l©ói)ūįsynth_1Ą─ŠW(w©Żng)▒Ēį┌ā╚(n©©i)┤µųą╩╣ė├╝s╩°╝»constr_1▀\(y©┤n)ąąĪŻ┤╦╝s╩°╝»░³║¼ą“┴ąa.xdcŻ¼b.xdc║═c.xdcųąĄ─╚²éĆ(g©©)XDC╬─╝■ĪŻ╚ń╣¹▀xō±b.xdcū„×ķ─┐ś╦(bi©Īo)XDC╬─╝■▓óŪę├┐éĆ(g©©)╬─╝■░³║¼¤o(w©▓)ą¦╝s╩°Ż¼ätTiming ConstraintsŽ“?q©▒)¦īóæ?y©®ng)ė├═Ų╦]Ą─Ģr(sh©¬)ńŖŻ¼╚╗║¾į┌└^└m(x©┤)ł╠(zh©¬)ąąŽ┬ę╗▓Į▓ó░l(f©Ī)¼F(xi©żn)Ųõ╦¹╚▒╔┘Ą─╝s╩°ų«Ū░Å─c.xdcųžą┬æ¬(y©®ng)ė├¤o(w©▓)ą¦╝s╩°ĪŻ

─·¤o(w©▓)Ę©į┌▀@ą®─Ż╩ĮŽ┬ųĖČ©─┐ś╦(bi©Īo)XDC╬─╝■Ż¼ę“┤╦Ī░Ģr(sh©¬)ą“╝s╩°Ī▒Ž“?q©▒)¦Ģ?hu©¼)į┌╝s╩°ą“┴ąĄ─ūŅ║¾╬╗ų├═Ų╦]▓óæ¬(y©®ng)ė├ą┬╝s╩°ĪŻ ▀@ŽÓ«ö(d©Īng)ė┌į┌Tcl┐žųŲ┼_(t©ói)ųą▌ö╚ļą┬╝s╩°╗“═©▀^(gu©░)Timing Constraints┤░┐┌▌ö╚ļą┬╝s╩°ĪŻ į┌▀@ą®─Ż╩ĮŽ┬Ż¼Ž“?q©▒)¦▓╗Ģ?hu©¼)ćLįćųžą┬æ¬(y©®ng)ė├¤o(w©▓)ą¦╝s╩°ĪŻ ╚ń╣¹ąĶę¬į┌š¹éĆ(g©©)╝s╩°ą“┴ąųąĖ³įńĄžæ¬(y©®ng)ė├ą┬╝s╩°ęįĮŌøQ╝s╩°ę└┘ćąį╗“ā×(y©Łu)Ž╚╝ē(j©¬)å¢Ņ}Ż¼ät▒žĒÜ╩ųäė(d©░ng)ŠÄ▌ŗ╝s╩°ą“┴ąĪŻ

ęįŽ┬╩Ū╚ń║╬╩ųäė(d©░ng)ŠÄ▌ŗ╝s╩°Ą─╩Š└²

You cannot specify a target XDC file in these modes, so the Timing Constraints wizard recommends and applies new constraints at the last position of the constraints sequence. This is equivalent to entering new constraints in the Tcl Console or via the Timing Constraints window. In these modes, the wizard does not attempt to re-apply invalid constraints. If the new constraints need to be applied earlier in the overall constraints sequence in order to resolve constraints dependencies or precedence issues, you must edit the constraints sequence manually.

─·¤o(w©▓)Ę©į┌▀@ą®─Ż╩ĮŽ┬ųĖČ©─┐ś╦(bi©Īo)XDC╬─╝■Ż¼ę“┤╦Ī░Ģr(sh©¬)ą“╝s╩°Ī▒Ž“?q©▒)¦Ģ?hu©¼)į┌╝s╩°ą“┴ąĄ─ūŅ║¾╬╗ų├═Ų╦]▓óæ¬(y©®ng)ė├ą┬╝s╩°ĪŻ ▀@ŽÓ«ö(d©Īng)ė┌į┌Tcl┐žųŲ┼_(t©ói)ųą▌ö╚ļą┬╝s╩°╗“═©▀^(gu©░)Timing Constraints┤░┐┌▌ö╚ļą┬╝s╩°ĪŻ į┌▀@ą®─Ż╩ĮŽ┬Ż¼Ž“?q©▒)¦▓╗Ģ?hu©¼)ćLįćųžą┬æ¬(y©®ng)ė├¤o(w©▓)ą¦╝s╩°ĪŻ ╚ń╣¹ąĶę¬į┌š¹éĆ(g©©)╝s╩°ą“┴ąųąĖ³įńĄžæ¬(y©®ng)ė├ą┬╝s╩°ęįĮŌøQ╝s╩°ę└┘ćąį╗“ā×(y©Łu)Ž╚╝ē(j©¬)å¢Ņ}Ż¼ät▒žĒÜ╩ųäė(d©░ng)ŠÄ▌ŗ╝s╩°ą“┴ąĪŻ

─·┐╔ęį╩╣ė├Timing Constraints┤░┐┌▓ķ┐┤Ė³ą┬Ą─Ģr(sh©¬)ą“╝s╩°ą“┴ąĪŻ ▓ķ┐┤ą┬╝s╩°║¾Ż¼┐╔ęįīóą“┴ą▒Ż┤µĄĮDCPųą

Ž“?q©▒)¦┤“ķ_Ģr(sh©¬)┐╔ė├Ą─ł¾(b©żo)Ėµ╣”─▄«ö(d©Īng)Ī░Ģr(sh©¬)ą“╝s╩°Ī▒Ž“?q©▒)¦┤“ķ_Ģr(sh©¬)Ż¼╦³Ģ■(hu©¼)ūĶų╣Vivado IDEųąĄ─┤¾ČÓöĄ(sh©┤)▓┘ū„Ż¼░³└©╩╣ė├Tcl┐žųŲ┼_(t©ói)╗“▀\(y©┤n)ąąĢr(sh©¬)ą“Ęų╬÷Ż¼ęį▒▄├ŌöĄ(sh©┤)ō■(j©┤)Äņ(k©┤)▓Ņ«ÉĪŻ Ž“?q©▒)¦┤░┐┌╩╝ĮK╬╗ė┌Ųõ╦¹Vivado IDE┤░┐┌Ą─Ū░├µĪŻ ╚ń╣¹ąĶę¬įLå¢Vivado IDE▓╦å╬╗“┤░┐┌Ż¼ät▒žĒÜīóŽ“?q©▒)¦┤░┐┌ęŲĄĮé?c©©)├µĪŻ

Timing ConstraintsŽ“?q©▒)¦┤“ķ_Ģr(sh©¬)Ż¼ų╗ėąęįŽ┬╣”─▄┐╔ė├Ż║

•ł¾(b©żo)Ėµ║═┐╔ęĢ╗»Ģr(sh©¬)ńŖŠW(w©Żng)Įj(lu©░)

Most pages of the wizard have buttons to generate and access the clock network report in order to visualize the clock topologies, their source point, and the shared segments for some of the clocks.

Ž“?q©▒)¦Ą─┤¾ČÓö?sh©┤)Ēō(y©©)├µČ╝ėą░┤ŌoüĒ(l©ói)╔·│╔║═įLå¢Ģr(sh©¬)ńŖŠW(w©Żng)Įj(lu©░)ł¾(b©żo)ĖµŻ¼ęį▒Ń┐╔ęĢ╗»Ģr(sh©¬)ńŖ═ž?f©┤)õŻ¼╦³éāĄ─į┤³c(di©Żn)ęį╝░─│ą®Ģr(sh©¬)ńŖĄ─╣▓ŽĒČ╬ĪŻ

ėąĻP(gu©Īn)Ģr(sh©¬)ńŖŠW(w©Żng)Įj(lu©░)ł¾(b©żo)ĖµĄ─Ė³ČÓįö╝Ü(x©¼)ą┼ŽóŻ¼šł(q©½ng)ģóķåĪ░VivadoįO(sh©©)ėŗ(j©¼)╠ū╝■ė├æ¶ųĖ─ŽŻ║įO(sh©©)ėŗ(j©¼)Ęų╬÷║═ĻP(gu©Īn)ķ]╝╝ąg(sh©┤)Ī▒Ż©UG906Ż®[ģó┐╝4]ĪŻ

Searching a name in source files or an object in the design in memory

The Find and Find In Files dialog boxes are available from the Edit menu. You can use these dialog boxes to retrieve some information about the design while entering the constraints in the wizard.

• Creating and Viewing schematics

You can select design objects in the main Vivado IDE window and visualize them in schematics. All schematics features are available. Only the last step of the Timing Constraints wizard, Asynchronous Clock Domain Crossings, supports convenient schematics cross-probing when selecting one or several entries in the Timing Paths tab.

Refer to the Vivado Design Suite User Guide: Using the Vivado IDE (UG893) [Ref 7] for more info on using schematics.

į┌į┤╬─╝■ųą╦č╦„├¹ĘQ╗“į┌ā╚(n©©i)┤µųą╦č╦„įO(sh©©)ėŗ(j©¼)ųąĄ─ī”(du©¼)Ž¾

Ī░ŠÄ▌ŗĪ▒▓╦å╬ųą╠ß╣®┴╦Ī░▓ķšę║═▓ķšę╬─╝■Ī▒ī”(du©¼)įÆ┐“ĪŻ į┌Ž“?q©▒)¦ųą▌ö╚ļ╝s╩°Ģr(sh©¬)Ż¼┐╔ęį╩╣ė├▀@ą®ī”(du©¼)įÆ┐“Öz╦„ėąĻP(gu©Īn)įO(sh©©)ėŗ(j©¼)Ą─ę╗ą®ą┼ŽóĪŻ

•äō(chu©żng)Į©║═▓ķ┐┤įŁ└ĒłD

─·┐╔ęįį┌ų„Vivado IDE┤░┐┌ųą▀xō±įO(sh©©)ėŗ(j©¼)ī”(du©¼)Ž¾Ż¼▓óį┌įŁ└ĒłDųąīóŲõ┐╔ęĢ╗»ĪŻ ╦∙ėąįŁ└ĒłD╣”─▄Š∙┐╔ė├ĪŻ ų╗ėąĢr(sh©¬)ą“╝s╩°Ž“?q©▒)¦Ą─ūŅ║¾ę╗▓ĮŻ¼«É▓ĮĢr(sh©¬)ńŖė“Į╗▓µŻ¼į┌Ī░Ģr(sh©¬)ą“┬ĘÅĮĪ▒▀xĒŚ(xi©żng)┐©ųą▀xō±ę╗éĆ(g©©)╗“ČÓéĆ(g©©)Śl─┐Ģr(sh©¬)Ż¼ų¦│ųĘĮ▒ŃĄ─įŁ└ĒłDĮ╗▓µ╠Į£y(c©©)ĪŻ

ėąĻP(gu©Īn)╩╣ė├įŁ└ĒłDĄ─Ė³ČÓą┼ŽóŻ¼šł(q©½ng)ģóķåĪ░Vivado Design Suiteė├æ¶ųĖ─ŽŻ║╩╣ė├Vivado IDEŻ©UG893Ż®[ģó┐╝7]Ī▒ĪŻ

Visualizing constraints in memory with the Timing Constraints window Each page of the wizard includes a tab that shows the existing constraints of the same type as recommended by the step. This is convenient for quickly reviewing the details of constraints already created in the XDC files. For a complete view of all timing constraints in memory, the Timing Constraints window shows the full sequence of constraints, organized by XDC file, including scoping information. It also displays the invalid constraints.

╩╣ė├Ī░Ģr(sh©¬)ą“╝s╩°Ī▒┤░┐┌┐╔ęĢ╗»ā╚(n©©i)┤µųąĄ─╝s╩°Ž“?q©▒)¦Ą─├┐éĆ(g©©)Ēō(y©©)├µČ╝░³║¼ę╗éĆ(g©©)▀xĒŚ(xi©żng)┐©Ż¼įō▀xĒŚ(xi©żng)┐©’@╩Š┼c▓Į¾EĮ©ūhĄ─ŽÓ═¼ŅÉą═Ą─¼F(xi©żn)ėą╝s╩°ĪŻ ▀@ī”(du©¼)ė┌┐ņ╦┘▓ķ┐┤ęčį┌XDC╬─╝■ųąäō(chu©żng)Į©Ą─╝s╩°Ą─įö╝Ü(x©¼)ą┼Žó║▄ĘĮ▒ŃĪŻ ėąĻP(gu©Īn)ā╚(n©©i)┤µųą╦∙ėąĢr(sh©¬)ą“╝s╩°Ą─═Ļš¹ęĢłDŻ¼Timing Constraints┤░┐┌’@╩Šė╔XDC╬─╝■ĮM┐ŚĄ─═Ļš¹╝s╩°ą“┴ąŻ¼░³└©ū„ė├ė“ą┼ŽóĪŻ ╦³▀Ć’@╩Š¤o(w©▓)ą¦╝s╩°ĪŻ

Constraints Editing within the Wizard

Each step of the wizard can recommend several constraints. Depending on the constraint,you must take one of the following actions:

• Uncheck the constraints you do not want to create, using one of the following

methods:

ĪŃ Remove each constraint from the list, one at a time, by unchecking each line.

ĪŃ Remove all constraints by unchecking the upper left check box of the table.

╝s╩°į┌Ž“?q©▒)¦ųąŠÄ▌?br />Ž“?q©▒)¦Ą─├┐éĆ(g©©)▓Į¾EČ╝┐╔ęį═Ų╦]ÄūéĆ(g©©)╝s╩°ĪŻ Ė∙ō■(j©┤)╝s╩°Ż¼─·▒žĒÜł╠(zh©¬)ąąęįŽ┬▓┘ū„ų«ę╗Ż║

•╩╣ė├ęįŽ┬ĘĮĘ©ų«ę╗╚ĪŽ¹▀xųą─·▓╗Žļäō(chu©żng)Į©Ą─╝s╩°

ĘĮĘ©Ż║

ĪŃ═©▀^(gu©░)╚ĪŽ¹▀xųą├┐ę╗ąąŻ¼Å─┴ą▒Ēųąäh│²├┐éĆ(g©©)╝s╩°Ż¼ę╗┤╬ę╗éĆ(g©©)ĪŻ

ĪŃ═©▀^(gu©░)╚ĪŽ¹▀xųą▒ĒĖ±Ą─ū¾╔ŽĮŪÅ═(f©┤)▀x┐“üĒ(l©ói)äh│²╦∙ėą╝s╩°ĪŻ

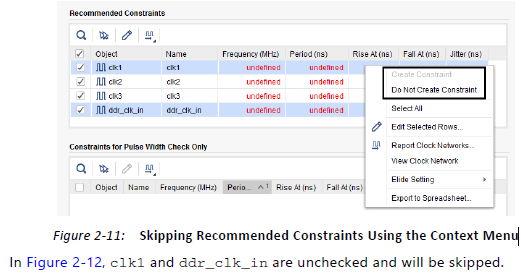

╠ß╩ŠŻ║╗“š▀Ż¼─·┐╔ęįėęµIå╬ō¶╝s╩°Ż¼╚╗║¾▀xō±Ī░▓╗äō(chu©żng)Į©╝s╩°Ī▒Ż¼╚ńłD╦∙╩Š

łD2-11ĪŻ

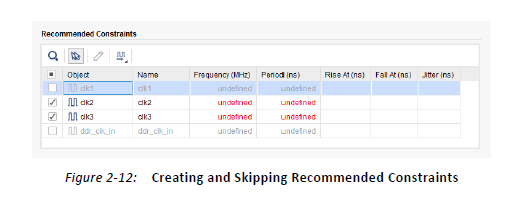

į┌łD2-12ųąŻ¼clk1║═ddr_clk_in╬┤▀xųąŻ¼īó▒╗╠°▀^(gu©░)ĪŻ

═©▀^(gu©░)å╬ō¶’@╩Š╬┤Č©┴xĄ─å╬į¬Ė±▌ö╚ļ╚▒╔┘Ą─ųĄŻ©└²╚ńŻ¼łD2-12ųąĄ─clk2║═clk3Ą─Ņl┬╩╗“ų▄Ų┌ųĄŻ®ĪŻ

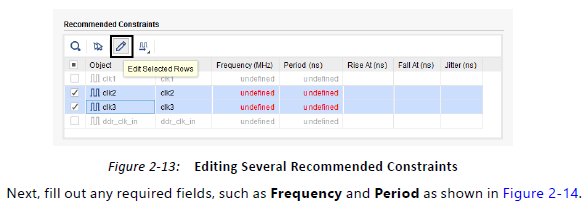

─·┐╔ęį═©▀^(gu©░)▀xō±ŽÓæ¬(y©®ng)Ą─ąą▓óå╬ō¶Edit Selected Rows░┤Ōo═¼Ģr(sh©¬)ŠÄ▌ŗČÓéĆ(g©©)╝s╩°Ż¼╚ńłD2-13╦∙╩ŠĪŻ

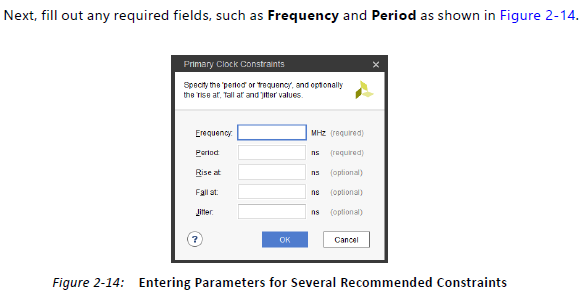

ĮėŽ┬üĒ(l©ói)Ż¼╠Ņīæ╦∙ėą▒ž╠ŅūųČ╬Ż¼╚ńFrequency║═PeriodŻ¼╚ńłD2-14╦∙╩ŠĪŻ

ę╗┤╬ŠÄ▌ŗČÓéĆ(g©©)╝s╩°ī”(du©¼)▌ö╚ļ║═▌ö│÷čė▀t╠žäeėąė├

Ž▐ųŲĪŻ

•╚ń╣¹▓╗ąĶę¬▓╔╚Ī╚╬║╬┤ļ╩®Ż¼ų╗ąĶ▓ķ┐┤╝s╩°ĪŻ

Öz▓ķ▓ó═Ļ│╔╦∙ėąęčÖz▓ķĄ─Į©ūh╝s╩°║¾Ż¼å╬ō¶Ī░Ž┬ę╗▓ĮĪ▒└^└m(x©┤)Ž┬ę╗Ēō(y©©)ĪŻ ─·Õe(cu©░)▀^(gu©░)Ą─╚╬║╬Śl─┐Č╝Ģ■(hu©¼)ūĶų╣Ž“?q©▒)¦▀M(j©¼n)╚ļŽ┬ę╗▓ĮĪŻ

─·┐╔ęį╩╣ė├Ī░║¾═╦Ī▒░┤Ōoųžą┬įLå¢Ēō(y©©)├µĪŻ ╚ń╣¹į┌╔Žę╗Ēō(y©©)╔ŽŠÄ▌ŗ╚╬║╬╝s╩°▓óå╬ō¶Ī░Ž┬ę╗▓ĮĪ▒Ż¼ätŽ“?q©▒)¦īóųžą┬Ęų╬÷įO(sh©©)ėŗ(j©¼)▓óŽÓæ¬(y©®ng)Ąž═Ų╦]ą┬╝s╩°ĪŻ į┌┤¾ČÓöĄ(sh©┤)ŪķørŽ┬Ż¼Ž╚Ū░Į©ūhĄ─╝s╩°▓╗╩▄ė░Ēæ

Ė³Ė─ęč╗ųÅ═(f©┤)ĪŻ ╚ń╣¹ų╗▓ķ┐┤╔Žę╗Ēō(y©©)Č°▓╗ą▐Ė─╚╬║╬Į©ūhĄ─╝s╩°Ż¼ätŽ“?q©▒)¦▓╗Ģ?hu©¼)ųžą┬▀\(y©┤n)ąą╚╬║╬Ęų╬÷Ż¼▀@═©│ŻĢ■(hu©¼)╣Ø(ji©”)╩Ī▀\(y©┤n)ąąĢr(sh©¬)ķgĪŻ

ųžę¬ą┼ŽóŻ║─·¤o(w©▓)Ę©╩╣ė├Ī░Ģr(sh©¬)ą“╝s╩°Ī▒Ž“?q©▒)¦ŠÄ▌ŗ¼F(xi©żn)ėąĢr(sh©¬)ą“╝s╩°ĪŻ ŽÓĘ┤Ż¼─·▒žĒÜ╩╣ė├Timing Constraints┤░┐┌ĪŻ

Constraints Recommended by the Wizard

Primary Clocks

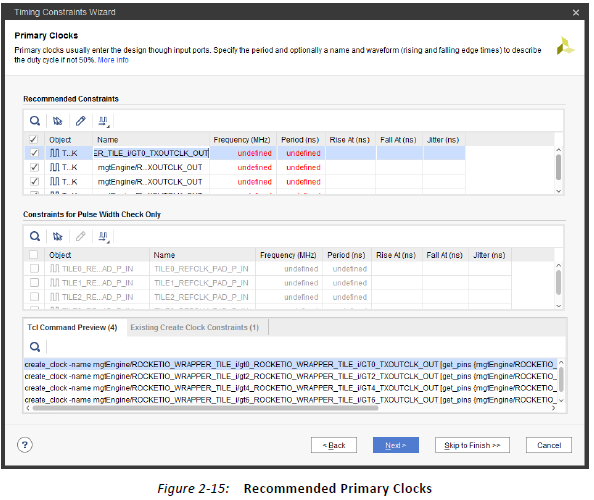

Two categories of clocks are identified by the wizard, as shown in Figure 2-15.

Ž“?q©▒)¦ś?bi©Īo)ūR(sh©¬)ā╔ŅÉĢr(sh©¬)ńŖŻ¼╚ńłD2-15╦∙╩ŠĪŻ

ėŗ(j©¼)╦ŃĢr(sh©¬)ą“╦╔│┌╦∙ąĶĄ─ų„ę¬Ģr(sh©¬)ńŖ

Į©ūh╝s╩°▒Ēųą’@╩ŠĮ©┴ó/▒Ż│ų/╗ųÅ═(f©┤)/äh│²Öz▓ķĪŻ

•āHł╠(zh©¬)ąą├}ø_īÆČ╚Öz▓ķ╦∙ąĶĄ─Ģr(sh©¬)ńŖŻ©min_periodŻ¼max_periodŻ¼max_skewŻ¼min_low_pulse_width║═min_high_pulse_widthŻ®│÷¼F(xi©żn)į┌Ī░āHŽ▐├}ø_īÆČ╚Öz▓ķŽ▐ųŲĪ▒▒ĒųąĪŻ ─¼šJ(r©©n)ŪķørŽ┬Ż¼▀@ą®Ģr(sh©¬)ńŖ╬┤▀xųąŻ¼ę“?y©żn)ķ╦³éāāHė├ė┌ł¾(b©żo)Ėµ─┐Ą─Č°▓╗Ģ■(hu©¼)ė░Ēæ

īŹ(sh©¬)╩®╣żŠ▀Ą─ĮY(ji©”)╣¹┘|(zh©¼)┴┐ĪŻ

Ž“?q©▒)¦Ģ?hu©¼)ūįäė(d©░ng)ūR(sh©¬)äe╝s╩°Ą─š²┤_Ģr(sh©¬)ńŖį┤³c(di©Żn)ĪŻ ╦³ī”(du©¼)æ¬(y©®ng)ė┌Ģr(sh©¬)ńŖśõĖ∙Ż¼ŲõųąĢr(sh©¬)ńŖą┼╠¢(h©żo)īŹ(sh©¬)ļH▀M(j©¼n)╚ļįO(sh©©)ėŗ(j©¼)ĪŻ į┌┤¾ČÓöĄ(sh©┤)ŪķørŽ┬Ż¼Ģr(sh©¬)ńŖį┤³c(di©Żn)╩Ū▌ö╚ļĢr(sh©¬)ńŖČ╦┐┌Ż¼į┌─│ą®╠ž╩ŌŪķørŽ┬Ż¼╦³╩Ūø]ėąČ©Ģr(sh©¬)╗ĪĄ─╗∙į¬Ą─▌ö│÷ĪŻ └²╚ńŻ¼į┌7ŽĄ┴ąįO(sh©©)éõųąŻ¼Ž“?q©▒)¦Ģ?hu©¼)ūR(sh©¬)äeGT_CHANNEL╗∙į¬▌ö│÷╔Ž╚▒╔┘Ą─ų„Ģr(sh©¬)ńŖĪŻ ī”(du©¼)ė┌UltraScale™Ų„╝■Ż¼Vivado Design Suite─▄ē“Ė∙ō■(j©┤)▌ö╚ļĢr(sh©¬)ńŖ╠žąįęį╝░GT_CHANNEL┼õų├║═▀BĮėūįäė(d©░ng)ī¦(d©Żo)│÷GT_CHANNEL▌ö│÷Ģr(sh©¬)ńŖĪŻ ę“┤╦Ż¼Ž“?q©▒)¦Ģ?hu©¼)Į©ūh╬╗ė┌įO(sh©©)ėŗ(j©¼)▀ģĮń╔ŽGT_CHANNELå╬į¬╔Žė╬Ą─ų„Ģr(sh©¬)ńŖĪŻ

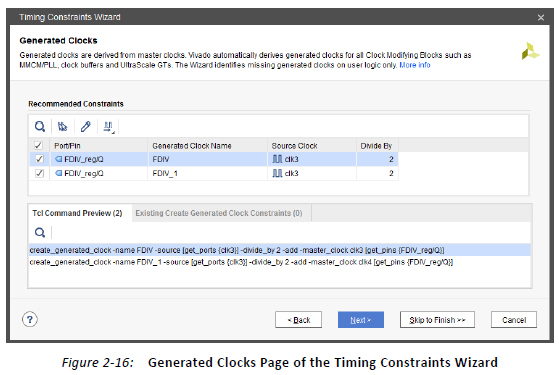

╔·│╔Ą─Ģr(sh©¬)ńŖ

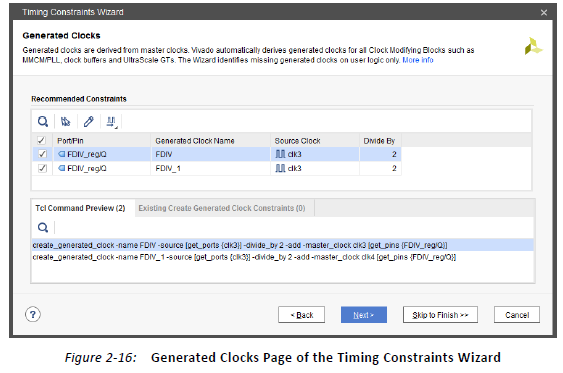

Timing ConstraintsŻ©Ģr(sh©¬)ą“╝s╩°Ż®Ž“?q©▒)¦Į©ūhį┌Ēśą“å╬į¬Ą─▌ö│÷╔Žų▒Įė╗“═©▀^(gu©░)─│ą®╗ź▀B▀ē▌ŗ“ī(q©▒)äė(d©░ng)Ųõ╦¹Ēśą“å╬į¬Ą─Ģr(sh©¬)ńŖę²─_Ģr(sh©¬)Ż¼äō(chu©żng)Į©╔·│╔Ģr(sh©¬)ńŖĪŻ ┼cPLL╗“MMCM▓╗═¼Ż¼ė├æ¶▀ē▌ŗ▓╗─▄│╦ęįų„Ģr(sh©¬)ńŖĄ─Ņl┬╩Ż¼ę“┤╦Ž“?q©▒)¦āH╠ß╣®ųĖČ©│²Ę©ŽĄöĄ(sh©┤)Ą─▀xĒŚ(xi©żng)Ż¼╚ńłD2-16╦∙╩ŠĪŻ

«ö(d©Īng)ČÓéĆ(g©©)ų„Ģr(sh©¬)ńŖĄĮ▀_(d©ó)╔·│╔Ą─Ģr(sh©¬)ńŖį┤³c(di©Żn)Ģr(sh©¬)Ż¼Ž“?q©▒)¦īó╩╣ė├╬©ę╗Ą─├¹ĘQ║═ī”(du©¼)Ė„éĆ(g©©)ų„Ģr(sh©¬)ńŖĄ─ŪÕ╬·ę²ė├üĒ(l©ói)äō(chu©żng)Į©╦∙ėąŽÓæ¬(y©®ng)Ą─╔·│╔Ģr(sh©¬)ńŖĪŻ łD2-16šf(shu©Ł)├„┴╦ā╔éĆ(g©©)Ģr(sh©¬)ńŖŻ©clk3║═clk4Ż®ĄĮ▀_(d©ó)Ą─Ūķør

Ēśą“å╬į¬FDIV_RegĪŻ ę“┤╦Ż¼Į©ūh╩╣ė├ā╔éĆ(g©©)╔·│╔Ą─Ģr(sh©¬)ńŖ╝s╩°Ż©FDIV║═FDIV_1Ż®ĪŻ

ūóęŌŻ║─│ą®Ģr(sh©¬)ńŖ═ž?f©┤)õŻ©└²╚ńĢr(sh©¬)ńŖ┬ĘÅĮ╔ŽĄ─╝ē(j©¬)┬ō(li©ón)╝─┤µŲ„Ż®┐╔─▄ąĶę¬ČÓ┤╬▀\(y©┤n)ąąĪ░Ģr(sh©¬)ą“╝s╩°Ī▒Ž“?q©▒)¦▓┼─▄░l(f©Ī)¼F(xi©żn)╦∙ėąüG╩¦Ą─╔·│╔Ģr(sh©¬)ńŖĪŻ

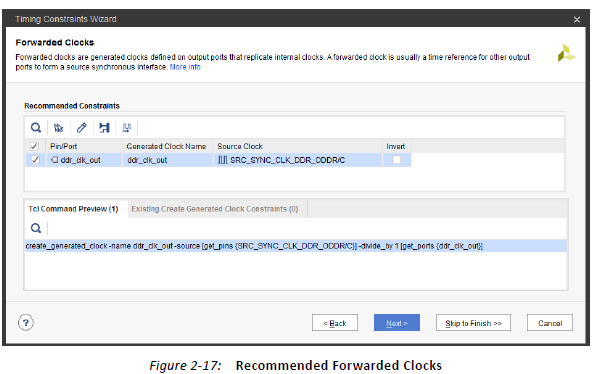

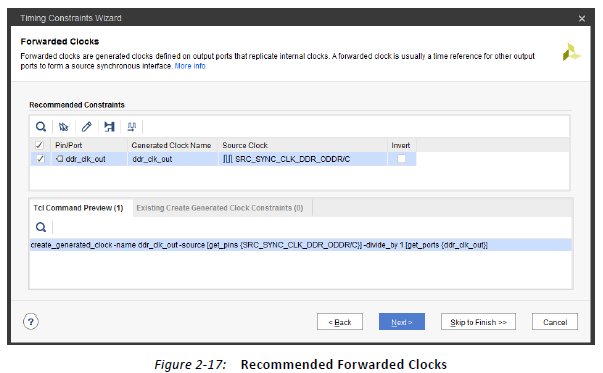

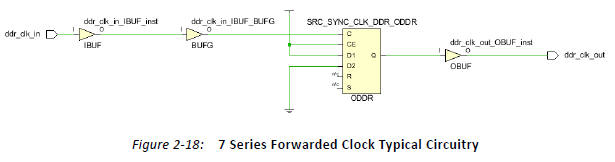

▐D(zhu©Żn)░l(f©Ī)Ģr(sh©¬)ńŖ

Timing ConstraintsŽ“?q©▒)¦Į©ūhį┌▌ö│÷Č╦┐┌╔Ž╔·│╔Ģr(sh©¬)ńŖ╝s╩°Ż¼įō▌ö│÷Č╦┐┌ė╔Š▀ėą│Ż┴┐▌ö╚ļĄ─ļp▒ČöĄ(sh©┤)ō■(j©┤)╦┘┬╩╝─┤µŲ„“ī(q©▒)äė(d©░ng)ĪŻ ╗∙ė┌▌ö╚ļ║ŃČ©▀BĮėąįŻ¼īó╔·│╔Ą─Ģr(sh©¬)ńŖŽÓ╬╗š{(di©żo)š¹×ķš²Ż©0Č╚ŽÓęŲŻ®╗“Ę┤ŽÓŻ©180Č╚ŽÓęŲŻ®ĪŻ ╝s╩°ųą╩╣ė├Ą─ų„Ģr(sh©¬)ńŖ╩ŪĄĮ▀_(d©ó)ļp▒ČöĄ(sh©┤)ō■(j©┤)╦┘┬╩╝─┤µŲ„Ą─Ģr(sh©¬)ńŖę²─_Ą─Ģr(sh©¬)ńŖĪŻ ▓ķ┐┤į┤Ģr(sh©¬)ńŖ

łD2-17ųą═Ų╦]╝s╩°▒ĒĄ─┴ąĪŻ

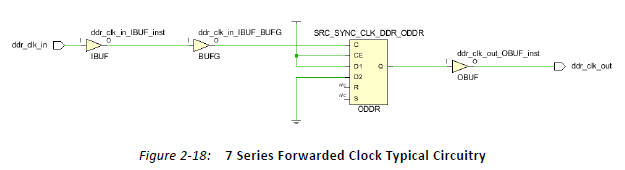

ī”(du©¼)ė┌7ŽĄ┴ąŲ„╝■ŽĄ┴ąŻ¼Ž“?q©▒)¦ūR(sh©¬)äeĄ─═ž?f©┤)õĮY(ji©”)śŗ(g©░u)╚ńŽ┬╦∙╩Š

łD2-18ĪŻ ų„Ģr(sh©¬)ńŖ╗“▌ö│÷ŠÅø_Ų„Ą─ąį┘|(zh©¼)ø]ėąŽ▐ųŲĪŻ

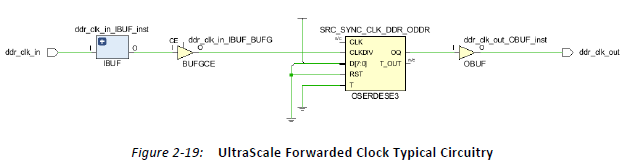

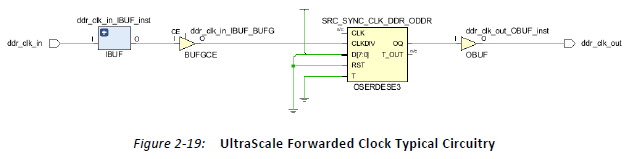

ī”(du©¼)ė┌UltraScaleŲ„╝■ŽĄ┴ąŻ¼ODDR║═ODDRE1įŁšZ(y©│)Ģ■(hu©¼)ūįäė(d©░ng)ųžČ©Ž“ĄĮOSERDESE3Ż¼Ųõī┘ąį×ķODDR_MODE = TRUEĪŻ Ž“?q©▒)¦ūR(sh©¬)äełD2-19ųą╦∙╩ŠĄ─═ž?f©┤)õŻ¼ŲõųąOSERDESE3 / D [0]▀BĮėĄĮ1║═

OSERDESE3 / D [4]▀BĮėĄĮ0Ż©¤o(w©▓)ŽÓęŲŻ®

═Ō▓┐Ę┤üčė▀t

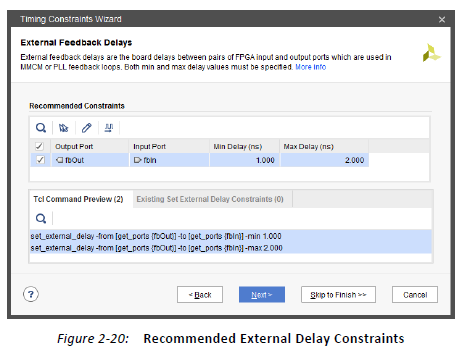

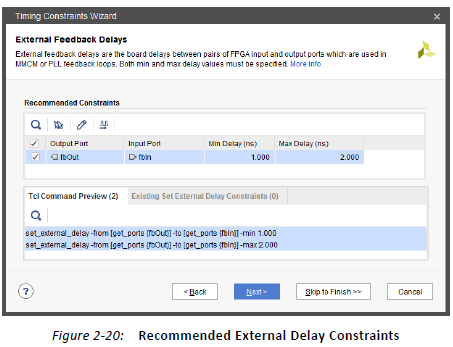

Timing ConstraintsŻ©Ģr(sh©¬)ą“╝s╩°Ż®Ž“?q©▒)¦Ęų╬÷įO(sh©©)ėŗ(j©¼)ųą┤µį┌Ą─MMCM║═PLLå╬į¬Ą─Ę┤üŁh(hu©ón)┬Ę▀BĮėĪŻ Į©ūh╩╣ė├═Ō▓┐čė▀t╝s╩°Ż©ūŅąĪ║═ūŅ┤¾Ż®

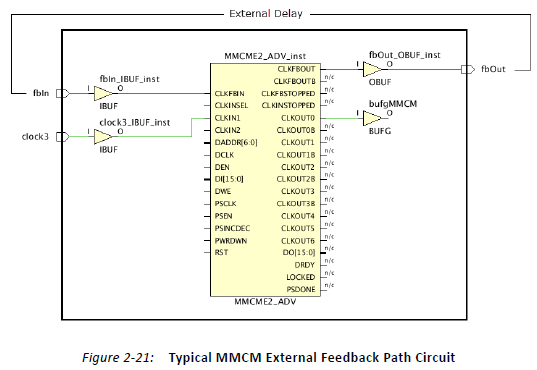

«ö(d©Īng)CLKFBIN║═CLKFBOUTę²─_═©▀^(gu©░)IOŠÅø_Ų„║═MMCM╗“PLLī┘ąįCOMPENSATION = EXTERNAL▀BĮėĄĮįO(sh©©)ėŗ(j©¼)Č╦┐┌Ģr(sh©¬)ĪŻ łD2-20šf(shu©Ł)├„┴╦═Ų╦]Ą─═Ō▓┐čė▀t╝s╩°ĪŻ

łD2-21’@╩Š┴╦Š▀ėą═Ō▓┐Ę┤ü┬ĘÅĮļŖ┬ĘĄ─Ąõą═MMCMĪŻ

In the current Vivado Design Suite release, the Timing Constraints wizard cannot

recommend external delay constraints when there is a sequential cell in the feedback path,

such as ODDR, which is used for generating a forwarded clock. In this case, you must create

the external delay constraints manually or using the Timing Constraints window after

exiting the wizard.

į┌«ö(d©Īng)Ū░Ą─Vivado Design Suite░µ▒ŠųąŻ¼«ö(d©Īng)Ę┤ü┬ĘÅĮųą┤µį┌▀B└m(x©┤)å╬į¬Ż©└²╚ńODDRŻ¼ė├ė┌╔·│╔▐D(zhu©Żn)░l(f©Ī)Ģr(sh©¬)ńŖŻ®Ģr(sh©¬)Ż¼Timing ConstraintsŽ“?q©▒)¦▓╗Į©ūh╩╣ė├═Ō▓┐čė▀t╝s╩°ĪŻ į┌▀@ĘNŪķørŽ┬Ż¼─·▒žĒÜį┌═╦│÷Ž“?q©▒)¦║¾╩ųä?d©░ng)╗“╩╣ė├Timing Constraints┤░┐┌äō(chu©żng)Į©═Ō▓┐čė▀t╝s╩°ĪŻ

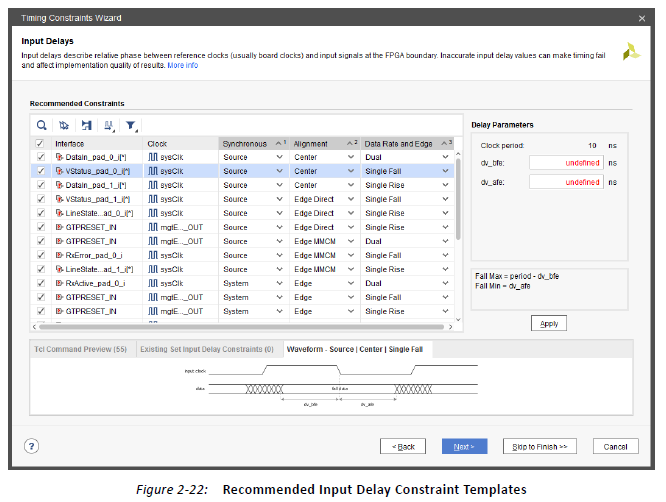

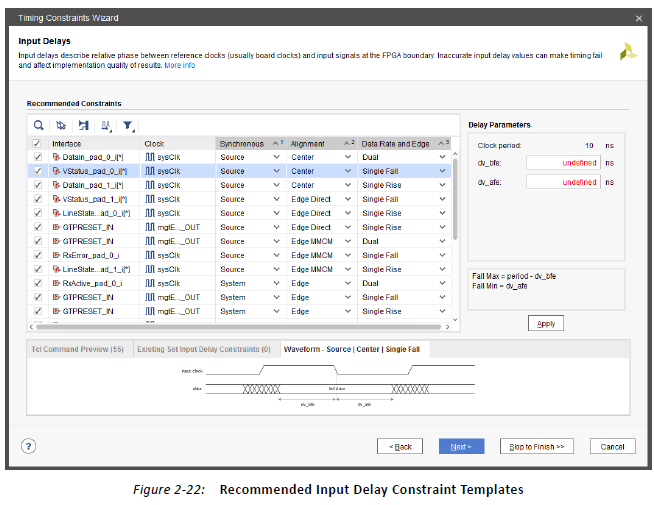

Input Delays

The Timing Constraints wizard analyzes all paths from input ports to identify their

destination clock inside the design and their active edges. Based on this information, the

wizard recommends basic system synchronous input delay constraints that are based on the

XDC templates available in the Vivado IDE (see XDC Templates, page 55 for templates). The

waveform associated with the selected template is displayed at the bottom of the window

in the Waveform tab when you select a constraint entry in the Recommended Constraints

table.

▌ö╚ļčė▀t

Timing ConstraintsŻ©Ģr(sh©¬)ą“╝s╩°Ż®Ž“?q©▒)¦Ęų╬÷ü?l©ói)ūį▌ö╚ļČ╦┐┌Ą─╦∙ėą┬ĘÅĮŻ¼ęįūR(sh©¬)äeįO(sh©©)ėŗ(j©¼)ųąĄ──┐ś╦(bi©Īo)Ģr(sh©¬)ńŖ╝░Ųõ╗Ņäė(d©░ng)▀ģŠēĪŻ Ė∙ō■(j©┤)┤╦ą┼ŽóŻ¼Ž“?q©▒)¦Ģ?hu©¼)Į©ūh╗∙ė┌Ą─╗∙▒ŠŽĄĮy(t©»ng)═¼▓Į▌ö╚ļčė▀t╝s╩°

Vivado IDEųą╠ß╣®Ą─XDC─Ż░ÕŻ©ėąĻP(gu©Īn)─Ż░ÕŻ¼šł(q©½ng)ģóķåXDC─Ż░ÕŻ¼Ą┌55Ēō(y©©)Ż®ĪŻ į┌Ī░═Ų╦]╝s╩°Ī▒▒Ēųą▀xō±╝s╩°Śl─┐Ģr(sh©¬)Ż¼┼c╦∙▀x─Ż░ÕĻP(gu©Īn)┬ō(li©ón)Ą─▓©ą╬īó’@╩Šį┌Ī░▓©ą╬Ī▒▀xĒŚ(xi©żng)┐©ųą┤░┐┌Ą─Ąū▓┐ĪŻ

łD2-22’@╩Š┴╦Ž“?q©▒)¦╠ß│÷▓óė╔ė├æ¶▀M(j©¼n)ąą▓┐ĘųŠÄ▌ŗĄ─ÄūéĆ(g©©)▌ö╚ļ╝s╩°Ą─╩Š└²ĪŻ

For each constraint, you can edit three characteristics in order to specify the appropriate waveform that corresponds to the actual interface timing on the board:

• Synchronous describes the nature of the clock-data relationship.

ĪŃ System (for System Synchronous interface): use this setting when the data is launched and captured by different clock edges that are 1 period or ½ period apart.

ĪŃ Source (for Source Synchronous interface): use this setting when the data is launched and captured by the same clock edge.

• Alignment describes the data transition alignment with respect to the active clock edge.

ĪŃ For System Synchronous interfaces only:

- Edge: use this setting when the clock and data transition at the same time.

ī”(du©¼)ė┌├┐éĆ(g©©)╝s╩°Ż¼─·┐╔ęįŠÄ▌ŗ╚²éĆ(g©©)╠žš„Ż¼ęįųĖČ©┼cļŖ┬Ę░Õ╔ŽīŹ(sh©¬)ļHĮė┐┌Ģr(sh©¬)ą“?q©▒)”æ?y©®ng)Ą─ŽÓæ¬(y©®ng)▓©ą╬Ż║

•═¼▓Į├Ķ╩÷Ģr(sh©¬)ńŖöĄ(sh©┤)ō■(j©┤)ĻP(gu©Īn)ŽĄĄ─ąį┘|(zh©¼)ĪŻ

ĪŃŽĄĮy(t©»ng)Ż©ė├ė┌ŽĄĮy(t©»ng)═¼▓ĮĮė┐┌Ż®Ż║«ö(d©Īng)öĄ(sh©┤)ō■(j©┤)═©▀^(gu©░)1éĆ(g©©)ų▄Ų┌╗“ŽÓĖ¶1/2ų▄Ų┌Ą─▓╗═¼Ģr(sh©¬)ńŖ▀ģčžåóäė(d©░ng)║═▓Č½@Ģr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

ĪŃSourceŻ©ė├ė┌į┤═¼▓ĮĮė┐┌Ż®Ż║«ö(d©Īng)öĄ(sh©┤)ō■(j©┤)ęįŽÓ═¼Ą─Ģr(sh©¬)ńŖ▀ģčžåóäė(d©░ng)║═▓Č½@Ģr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

•ī”(du©¼)²R├Ķ╩÷┴╦┼c╗Ņäė(d©░ng)Ģr(sh©¬)ńŖ▀ģ螎ÓĻP(gu©Īn)Ą─öĄ(sh©┤)ō■(j©┤)▐D(zhu©Żn)ōQī”(du©¼)²RĪŻ

ĪŃāH▀mė├ė┌ŽĄĮy(t©»ng)═¼▓ĮĮė┐┌Ż║

- EdgeŻ║«ö(d©Īng)Ģr(sh©¬)ńŖ║═öĄ(sh©┤)ō■(j©┤)═¼Ģr(sh©¬)▐D(zhu©Żn)ōQĢr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

āH▀mė├ė┌į┤═¼▓ĮĮė┐┌Ż║

- ųąą─Ż║«ö(d©Īng)Ģr(sh©¬)ńŖį┌öĄ(sh©┤)ō■(j©┤)ėąą¦┤░┐┌ųąķg▐D(zhu©Żn)ōQĢr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

- Edge DirectŻ║«ö(d©Īng)Ģr(sh©¬)ńŖį┌öĄ(sh©┤)ō■(j©┤)ėąą¦┤░┐┌Ą─ķ_Ņ^▐D(zhu©Żn)ōQĢr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

- Edge MMCMŻ║«ö(d©Īng)Ģr(sh©¬)ńŖį┌öĄ(sh©┤)ō■(j©┤)ėąą¦┤░┐┌ĮY(ji©”)╩°Ģr(sh©¬)▐D(zhu©Żn)ōQĢr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

•Data Rate║═Edge├Ķ╩÷┴╦╩▄─Ż░Õ╝s╩°Ą─╗Ņäė(d©░ng)Ģr(sh©¬)ńŖ▀ģčžĪŻ Ž“?q©▒)¦Į©ūhĄ──¼šJ(r©©n)ųĄ╗∙ė┌▓Č½@Ēśą“å╬į¬Ą─╗Ņäė(d©░ng)Ģr(sh©¬)ńŖ▀ģčžĪŻ

ĪŃSingle RiseŻ║╩╣ė├┤╦įO(sh©©)ų├ė├ė┌ų╗ėą╔Ž╔²Ģr(sh©¬)ńŖčžåóäė(d©░ng)FPGA═Ō▓┐öĄ(sh©┤)ō■(j©┤)Ą─ŪķørĪŻ

ĪŃSingle FallŻ║╩╣ė├┤╦įO(sh©©)ų├ė├ė┌āHŽ┬ĮĄĢr(sh©¬)ńŖ▀ģčžFPGA═Ō▓┐öĄ(sh©┤)ō■(j©┤)åóäė(d©░ng)Ą─ŪķørĪŻ

ĪŃDualŻ║╩╣ė├┤╦įO(sh©©)ų├ė├ė┌╔Ž╔²║═Ž┬ĮĄĢr(sh©¬)ńŖčžåóäė(d©░ng)FPGA═Ō▓┐öĄ(sh©┤)ō■(j©┤)Ą─ŪķørĪŻ

You can also choose to generate the following recommended reports upon clicking Finish to verify that the design is completely and properly constrained:

• Create Timing Summary report: Timing slack is reported with the new constraints, in addition to a check_timing report. Timing violations will likely display if the period or I/O delay constraints that you entered are too difficult.

• Create Check Timing report: This report identifies missing or inappropriate constraints by running the check_timing command.

• Create DRC Report using only Timing Checks: this report runs the Timing DRCs.

─·▀Ć┐╔ęį▀xō±į┌å╬ō¶Ī░═Ļ│╔Ī▒║¾╔·│╔ęįŽ┬Į©ūhĄ─ł¾(b©żo)ĖµŻ¼ęį“×(y©żn)ūCįO(sh©©)ėŗ(j©¼)╩Ūʱ═Ļ╚½╩▄╝s╩°Ż║

•äō(chu©żng)Į©Ģr(sh©¬)ą“š¬ę¬ł¾(b©żo)ĖµŻ║│²┴╦check_timingł¾(b©żo)Ėµų«═ŌŻ¼▀ĆĢ■(hu©¼)╩╣ė├ą┬╝s╩°ł¾(b©żo)ĖµĢr(sh©¬)ą“╦╔│┌ĪŻ ╚ń╣¹─·▌ö╚ļĄ─ų▄Ų┌╗“I / Očė▀tŽ▐ųŲ╠½ļyŻ¼ät┐╔─▄Ģ■(hu©¼)’@╩ŠĢr(sh©¬)ą“▀`ęÄ(gu©®)ĪŻ

•äō(chu©żng)Į©Öz▓ķĢr(sh©¬)ķgł¾(b©żo)ĖµŻ║┤╦ł¾(b©żo)Ėµ═©▀^(gu©░)▀\(y©┤n)ąącheck_timing├³┴ŅüĒ(l©ói)ūR(sh©¬)äe╚▒╩¦╗“▓╗▀m«ö(d©Īng)?sh©┤)─╝s╩°ĪŻ

•āH╩╣ė├Ģr(sh©¬)ą“Öz▓ķäō(chu©żng)Į©DRCł¾(b©żo)ĖµŻ║┤╦ł¾(b©żo)Ėµ▀\(y©┤n)ąąĢr(sh©¬)ą“DRCĪŻ

ųžę¬ą┼ŽóŻ║│²ĘŪå╬ō¶Ī░╚ĪŽ¹Ī▒Ż¼Ę±ätą┬╠Ē╝ėĄ─╝s╩°īóūįäė(d©░ng)▒Ż┤µĄĮ─┐ś╦(bi©Īo)XDC╬─╝■ųąĪŻ ═╦│÷║¾Ż¼─·┐╔ęįį┌Timing Constraints┤░┐┌ųąŠÄ▌ŗ╗“äh│²ą┬╝s╩°

Ž“?q©▒)¦Ģ?hu©¼)ūįäė(d©░ng)ūR(sh©¬)äe╝s╩°Ą─š²┤_Ģr(sh©¬)ńŖį┤³c(di©Żn)ĪŻ ╦³ī”(du©¼)æ¬(y©®ng)ė┌Ģr(sh©¬)ńŖśõĖ∙Ż¼ŲõųąĢr(sh©¬)ńŖą┼╠¢(h©żo)īŹ(sh©¬)ļH▀M(j©¼n)╚ļįO(sh©©)ėŗ(j©¼)ĪŻ į┌┤¾ČÓöĄ(sh©┤)ŪķørŽ┬Ż¼Ģr(sh©¬)ńŖį┤³c(di©Żn)╩Ū▌ö╚ļĢr(sh©¬)ńŖČ╦┐┌Ż¼į┌─│ą®╠ž╩ŌŪķørŽ┬Ż¼╦³╩Ūø]ėąČ©Ģr(sh©¬)╗ĪĄ─╗∙į¬Ą─▌ö│÷ĪŻ └²╚ńŻ¼į┌7ŽĄ┴ąįO(sh©©)éõųąŻ¼Ž“?q©▒)¦Ģ?hu©¼)ūR(sh©¬)äeGT_CHANNEL╗∙į¬▌ö│÷╔Ž╚▒╔┘Ą─ų„Ģr(sh©¬)ńŖĪŻ ī”(du©¼)ė┌UltraScale™Ų„╝■Ż¼Vivado Design Suite─▄ē“Ė∙ō■(j©┤)▌ö╚ļĢr(sh©¬)ńŖ╠žąį║═GT_CHANNEL┼õų├║═▀BĮėūįäė(d©░ng)ī¦(d©Żo)│÷GT_CHANNEL▌ö│÷Ģr(sh©¬)ńŖĪŻ ę“┤╦Ż¼Ž“?q©▒)¦Ģ?hu©¼)Į©ūh╬╗ė┌įO(sh©©)ėŗ(j©¼)▀ģĮń╔ŽGT_CHANNELå╬į¬╔Žė╬Ą─ų„Ģr(sh©¬)ńŖĪŻ

«ö(d©Īng)ČÓéĆ(g©©)ų„Ģr(sh©¬)ńŖĄĮ▀_(d©ó)╔·│╔Ą─Ģr(sh©¬)ńŖį┤³c(di©Żn)Ģr(sh©¬)Ż¼Ž“?q©▒)¦īó╩╣ė├╬©ę╗Ą─├¹ĘQ║═ī”(du©¼)Ė„éĆ(g©©)ų„Ģr(sh©¬)ńŖĄ─ŪÕ╬·ę²ė├üĒ(l©ói)äō(chu©żng)Į©╦∙ėąŽÓæ¬(y©®ng)Ą─╔·│╔Ģr(sh©¬)ńŖĪŻ łD2-16šf(shu©Ł)├„┴╦ā╔éĆ(g©©)Ģr(sh©¬)ńŖŻ©clk3║═clk4Ż®ĄĮ▀_(d©ó)Ą─Ūķør

Ēśą“å╬į¬FDIV_RegĪŻ ę“┤╦Ż¼Į©ūh╩╣ė├ā╔éĆ(g©©)╔·│╔Ą─Ģr(sh©¬)ńŖ╝s╩°Ż©FDIV║═FDIV_1Ż®ĪŻ

ūóęŌŻ║─│ą®Ģr(sh©¬)ńŖ═ž?f©┤)õŻ©└²╚ńĢr(sh©¬)ńŖ┬ĘÅĮ╔ŽĄ─╝ē(j©¬)┬ō(li©ón)╝─┤µŲ„Ż®┐╔─▄ąĶę¬ČÓ┤╬▀\(y©┤n)ąąĪ░Ģr(sh©¬)ą“╝s╩°Ī▒Ž“?q©▒)¦▓┼─▄░l(f©Ī)¼F(xi©żn)╦∙ėąüG╩¦Ą─╔·│╔Ģr(sh©¬)ńŖĪŻ

▐D(zhu©Żn)░l(f©Ī)Ģr(sh©¬)ńŖ

Timing ConstraintsŽ“?q©▒)¦Į©ūhį┌▌ö│÷Č╦┐┌╔Ž╔·│╔Ģr(sh©¬)ńŖ╝s╩°Ż¼įō▌ö│÷Č╦┐┌ė╔Š▀ėą│Ż┴┐▌ö╚ļĄ─ļp▒ČöĄ(sh©┤)ō■(j©┤)╦┘┬╩╝─┤µŲ„“ī(q©▒)äė(d©░ng)ĪŻ ╗∙ė┌▌ö╚ļ║ŃČ©▀BĮėąįŻ¼īó╔·│╔Ą─Ģr(sh©¬)ńŖŽÓ╬╗š{(di©żo)š¹×ķš²Ż©0Č╚ŽÓęŲŻ®╗“Ę┤ŽÓŻ©180Č╚ŽÓęŲŻ®ĪŻ ╝s╩°ųą╩╣ė├Ą─ų„Ģr(sh©¬)ńŖ╩ŪĄĮ▀_(d©ó)ļp▒ČöĄ(sh©┤)ō■(j©┤)╦┘┬╩╝─┤µŲ„Ą─Ģr(sh©¬)ńŖę²─_Ą─Ģr(sh©¬)ńŖĪŻ ▓ķ┐┤į┤Ģr(sh©¬)ńŖ

łD2-17ųą═Ų╦]╝s╩°▒ĒĄ─┴ąĪŻ

ī”(du©¼)ė┌7ŽĄ┴ąŲ„╝■ŽĄ┴ąŻ¼Ž“?q©▒)¦ūR(sh©¬)äeĄ─═ž?f©┤)õĮY(ji©”)śŗ(g©░u)╚ńŽ┬╦∙╩Š

łD2-18ĪŻ ų„Ģr(sh©¬)ńŖ╗“▌ö│÷ŠÅø_Ų„Ą─ąį┘|(zh©¼)ø]ėąŽ▐ųŲĪŻ

For the UltraScale device family, the ODDR and ODDRE1 primitives are automatically

retargeted to OSERDESE3 with the property ODDR_MODE=TRUE. The wizard recognizes the

topology shown in Figure 2-19, where OSERDESE3/D[0] is connected to 1 and

OSERDESE3/D[4] is connected to 0 (no phase-shift).

ī”(du©¼)ė┌UltraScaleŲ„╝■ŽĄ┴ąŻ¼ODDR║═ODDRE1įŁšZ(y©│)Ģ■(hu©¼)ūįäė(d©░ng)ųžČ©Ž“ĄĮOSERDESE3Ż¼Ųõī┘ąį×ķODDR_MODE = TRUEĪŻŽ“?q©▒)¦ūR(sh©¬)äełD2-19ųą╦∙╩ŠĄ─═ž?f©┤)õŻ¼ŲõųąOSERDESE3 / D [0]▀BĮėĄĮ1Ż¼OSERDESE3 / D[4]▀BĮėĄĮ0Ż©¤o(w©▓)ŽÓęŲŻ®ĪŻ

═Ō▓┐Ę┤üčė▀t

Timing ConstraintsŻ©Ģr(sh©¬)ą“╝s╩°Ż®Ž“?q©▒)¦Ęų╬÷įO(sh©©)ėŗ(j©¼)ųą┤µį┌Ą─MMCM║═PLLå╬į¬Ą─Ę┤üŁh(hu©ón)┬Ę▀BĮėĪŻ Į©ūh╩╣ė├═Ō▓┐čė▀t╝s╩°Ż©ūŅąĪ║═ūŅ┤¾Ż®

«ö(d©Īng)CLKFBIN║═CLKFBOUTę²─_═©▀^(gu©░)IOŠÅø_Ų„║═MMCM╗“PLLī┘ąįCOMPENSATION = EXTERNAL▀BĮėĄĮįO(sh©©)ėŗ(j©¼)Č╦┐┌Ģr(sh©¬)ĪŻ łD2-20šf(shu©Ł)├„┴╦═Ų╦]Ą─═Ō▓┐čė▀t╝s╩°ĪŻ

Timing ConstraintsŻ©Ģr(sh©¬)ą“╝s╩°Ż®Ž“?q©▒)¦Ęų╬÷ü?l©ói)ūį▌ö╚ļČ╦┐┌Ą─╦∙ėą┬ĘÅĮŻ¼ęįūR(sh©¬)äeįO(sh©©)ėŗ(j©¼)ųąĄ──┐ś╦(bi©Īo)Ģr(sh©¬)ńŖ╝░Ųõ╗Ņäė(d©░ng)▀ģŠēĪŻ Ė∙ō■(j©┤)┤╦ą┼ŽóŻ¼Ž“?q©▒)¦Ģ?hu©¼)Į©ūh╗∙ė┌Ą─╗∙▒ŠŽĄĮy(t©»ng)═¼▓Į▌ö╚ļčė▀t╝s╩°

Vivado IDEųą╠ß╣®Ą─XDC─Ż░ÕŻ©ėąĻP(gu©Īn)─Ż░ÕŻ¼šł(q©½ng)ģóķåXDC─Ż░ÕŻ¼Ą┌55Ēō(y©©)Ż®ĪŻ į┌Ī░═Ų╦]╝s╩°Ī▒▒Ēųą▀xō±╝s╩°Śl─┐Ģr(sh©¬)Ż¼┼c╦∙▀x─Ż░ÕĻP(gu©Īn)┬ō(li©ón)Ą─▓©ą╬īó’@╩Šį┌Ī░▓©ą╬Ī▒▀xĒŚ(xi©żng)┐©ųą┤░┐┌Ą─Ąū▓┐ĪŻ

łD2-22’@╩Š┴╦Ž“?q©▒)¦╠ß│÷▓óė╔ė├æ¶▀M(j©¼n)ąą▓┐ĘųŠÄ▌ŗĄ─ÄūéĆ(g©©)▌ö╚ļ╝s╩°Ą─╩Š└²ĪŻ

ī”(du©¼)ė┌├┐éĆ(g©©)╝s╩°Ż¼─·┐╔ęįŠÄ▌ŗ╚²éĆ(g©©)╠žš„Ż¼ęįųĖČ©┼cļŖ┬Ę░Õ╔ŽīŹ(sh©¬)ļHĮė┐┌Ģr(sh©¬)ą“?q©▒)”æ?y©®ng)Ą─ŽÓæ¬(y©®ng)▓©ą╬Ż║

•═¼▓Į├Ķ╩÷Ģr(sh©¬)ńŖöĄ(sh©┤)ō■(j©┤)ĻP(gu©Īn)ŽĄĄ─ąį┘|(zh©¼)ĪŻ

ĪŃŽĄĮy(t©»ng)Ż©ė├ė┌ŽĄĮy(t©»ng)═¼▓ĮĮė┐┌Ż®Ż║«ö(d©Īng)öĄ(sh©┤)ō■(j©┤)═©▀^(gu©░)1éĆ(g©©)ų▄Ų┌╗“ŽÓĖ¶1/2ų▄Ų┌Ą─▓╗═¼Ģr(sh©¬)ńŖ▀ģčžåóäė(d©░ng)║═▓Č½@Ģr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

ĪŃSourceŻ©ė├ė┌į┤═¼▓ĮĮė┐┌Ż®Ż║«ö(d©Īng)öĄ(sh©┤)ō■(j©┤)ęįŽÓ═¼Ą─Ģr(sh©¬)ńŖ▀ģčžåóäė(d©░ng)║═▓Č½@Ģr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

•ī”(du©¼)²R├Ķ╩÷┴╦┼c╗Ņäė(d©░ng)Ģr(sh©¬)ńŖ▀ģ螎ÓĻP(gu©Īn)Ą─öĄ(sh©┤)ō■(j©┤)▐D(zhu©Żn)ōQī”(du©¼)²RĪŻ

ĪŃāH▀mė├ė┌ŽĄĮy(t©»ng)═¼▓ĮĮė┐┌Ż║

- EdgeŻ║«ö(d©Īng)Ģr(sh©¬)ńŖ║═öĄ(sh©┤)ō■(j©┤)═¼Ģr(sh©¬)▐D(zhu©Żn)ōQĢr(sh©¬)╩╣ė├┤╦įO(sh©©)ų├ĪŻ

▌ö│÷čė▀t

┼c▌ö╚ļčė▀t▓Į¾EŅÉ╦ŲŻ¼Ģr(sh©¬)ą“╝s╩°Ž“?q©▒)¦Ęų╬÷╦∙ėą▌ö│÷Č╦┐┌Ą─┬ĘÅĮŻ¼ęįūR(sh©¬)äeįO(sh©©)ėŗ(j©¼)ųąĄ─į┤Ģr(sh©¬)ńŖ╝░Ųõ╗Ņäė(d©░ng)▀ģčžĪŻ ─Ż░Õ▀xō±ęÄ(gu©®)ät┼c▌ö╚ļčė▀tųą├Ķ╩÷Ą─ŽÓ═¼ĪŻ łD2-24’@╩Š┴╦Ž“?q©▒)¦╠ß│÷Ą─ÄūéĆ(g©©)▌ö│÷╝s╩°Ż¼▓óė╔ė├æ¶▀M(j©¼n)ąą┴╦▓┐ĘųŠÄ▌ŗĪŻ

ī”(du©¼)ė┌├┐éĆ(g©©)╝s╩°Ż¼┐╔ęįŠÄ▌ŗ╚²éĆ(g©©)╠žš„Ż¼ęį▒ŃųĖČ©┼c░Õ╔ŽīŹ(sh©¬)ļHĮė┐┌Ģr(sh©¬)ą“ŽÓī”(du©¼)æ¬(y©®ng)Ą─▀m«ö(d©Īng)▓©ą╬Ż║

•Synchronous├Ķ╩÷Ģr(sh©¬)ńŖöĄ(sh©┤)ō■(j©┤)ĻP(gu©Īn)ŽĄĄ─ąį┘|(zh©¼)Ż©ėąĻP(gu©Īn)įö╝Ü(x©¼)ą┼ŽóŻ¼šł(q©½ng)ģóķå▌ö╚ļčė▀tŻ¼Ēō(y©©)├µ33Ż®ĪŻ

•ī”(du©¼)²R├Ķ╩÷┴╦┼c╗Ņäė(d©░ng)Ģr(sh©¬)ńŖ▀ģ螎ÓĻP(gu©Īn)Ą─öĄ(sh©┤)ō■(j©┤)▐D(zhu©Żn)ōQī”(du©¼)²RĪŻ

ĪŃĮ©┴ó/▒Ż│ųŻ║«ö(d©Īng)Ė∙ō■(j©┤)FPGA═Ō▓┐Ą─öĄ(sh©┤)ō■(j©┤)ėąą¦┤░┐┌Ģr(sh©¬)ą“╠žąįųĖČ©─Ż░Õčė▀tģóöĄ(sh©┤)Ģr(sh©¬)Ż¼╩╣ė├┤╦įO(sh©©)ų├ĪŻ

ĪŃSkewŻ©āHŽ▐į┤═¼▓ĮŻ®Ż║Ė∙ō■(j©┤)FPGAĄ─▌ö│÷ę²─_Ą─Ų½ą▒ę¬Ū¾ųĖČ©─Ż░Õčė▀tģóöĄ(sh©┤)Ģr(sh©¬)Ż¼╩╣ė├┤╦įO(sh©©)ų├ĪŻ

•Data Rate║═Edge├Ķ╩÷┴╦╩▄─Ż░Õ╝s╩°Ą─╗Ņäė(d©░ng)Ģr(sh©¬)ńŖ▀ģ螯©šł(q©½ng)ģóķå

▌ö╚ļčė▀tŻ¼Ą┌33Ēō(y©©)┴╦ĮŌĖ³ČÓįöŪķŻ®ĪŻ

┼c═Ų╦]Ą─▌ö╚ļčė▀t╝s╩°ę╗śėŻ¼ģó┐╝Ģr(sh©¬)ńŖ═©│Ż╩ŪļŖ┬Ę░ÕĢr(sh©¬)ńŖŻ¼Ą½ęįŽ┬Ūķør│²═ŌŻ║

•ļŖ┬Ę░ÕĢr(sh©¬)ńŖ║═▌ö│÷┬ĘÅĮā╚(n©©i)▓┐Ģr(sh©¬)ńŖŠ▀ėą▓╗═¼Ą─Ģr(sh©¬)ńŖų▄Ų┌ĪŻ▌ö│÷╝s╩°ę²ė├┼cā╚(n©©i)▓┐Ģr(sh©¬)ńŖŠ▀ėąŽÓ═¼▓©ą╬Ą─╠ōöMĢr(sh©¬)ńŖŻ¼ęį▒Ńęį1ų▄Ų┌┬ĘÅĮę¬Ū¾ł╠(zh©¬)ąąįO(sh©©)ų├Ęų╬÷ĪŻ

ūįäė(d©░ng)äō(chu©żng)Į©╠ōöMĢr(sh©¬)ńŖĪŻ

•┼cļŖ┬Ę░ÕĢr(sh©¬)ńŖŽÓ▒╚Ż¼▌ö│÷┬ĘÅĮā╚(n©©i)▓┐Ģr(sh©¬)ńŖŠ▀ėąžō(f©┤)ŽÓęŲĪŻįōŽ“?q©▒)¦╩╣ė├╠ōöMĢr(sh©¬)ńŖū„×ķģó┐╝Ģr(sh©¬)ńŖĪŻ╩╣ė├┼cļŖ┬Ę░ÕĢr(sh©¬)ńŖŽÓ═¼Ą─▓©ą╬ūįäė(d©░ng)äō(chu©żng)Į©╠ōöMĢr(sh©¬)ńŖĪŻ┤╦═ŌŻ¼Ž“?q©▒)¦▀ĆųĖČ©╠ōöMĢr(sh©¬)ńŖ║═ā╚(n©©i)▓┐Ģr(sh©¬)ńŖų«ķgĄ─ČÓų▄Ų┌┬ĘÅĮ╝s╩°Ż¼ęįīó─¼šJ(r©©n)Ęų╬÷š{(di©żo)š¹×ķ1éĆ(g©©)ų▄Ų┌+įO(sh©©)ų├Ą─ŽÓęŲ┴┐ĪŻ╠ōöMĢr(sh©¬)ńŖ║═ČÓų▄Ų┌┬ĘÅĮ╝s╩°Ą─ĮM║Ž×ķVivado Design SuiteČ©Ģr(sh©¬)Ų„╠ß╣®┴╦Ė³║å(ji©Żn)å╬Ą─╝s╩°Ż¼┐╔ęį╠Ä└Ē▓óŪęų╗─▄ė░Ēæ▌ö│÷Č╦┐┌

─ŪéĆ(g©©)ī”(du©¼)╠ōöMĢr(sh©¬)ńŖĄ─ę²ė├ĪŻ

ūóęŌŻ║ī”(du©¼)ė┌š²ŽÓęŲŻ¼▓╗ąĶę¬╠ōöMĢr(sh©¬)ńŖ║═ČÓų▄Ų┌┬ĘÅĮ╝s╩°Ż¼ę“?y©żn)ķ─¼šJ(r©©n)įO(sh©©)ų├┬ĘÅĮę¬Ū¾╩Ū1éĆ(g©©)ų▄Ų┌£p╚źŽÓęŲ┴┐ĪŻ

A forwarded clock has been identified for timing the output path based on the shared

clocking connectivity.

The forwarded clock must have been created during the third step of the wizard

"Forwarded Clocks," or else the board clock or a virtual clock will be used as the output

delay constraint reference clock.

ęčĮø(j©®ng)ūR(sh©¬)äe│÷▐D(zhu©Żn)░l(f©Ī)Ģr(sh©¬)ńŖŻ¼ė├ė┌╗∙ė┌╣▓ŽĒĢr(sh©¬)ńŖ▀BĮėī”(du©¼)▌ö│÷┬ĘÅĮ▀M(j©¼n)ąąČ©Ģr(sh©¬)ĪŻ

▒žĒÜį┌Ž“?q©▒)¦Ī░▐D(zhu©Żn)░l(f©Ī)Ģr(sh©¬)ńŖĪ▒Ą─Ą┌╚²▓Įųąäō(chu©żng)Į©▐D(zhu©Żn)░l(f©Ī)Ģr(sh©¬)ńŖŻ¼Ę±ätļŖ┬Ę░ÕĢr(sh©¬)ńŖ╗“╠ōöMĢr(sh©¬)ńŖīóė├ū„▌ö│÷čė▀t╝s╩°ģó┐╝Ģr(sh©¬)ńŖĪŻ

Ģr(sh©¬)ķgŽ▐ųŲļŖūė▒ĒĖ±

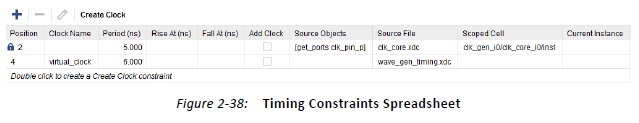

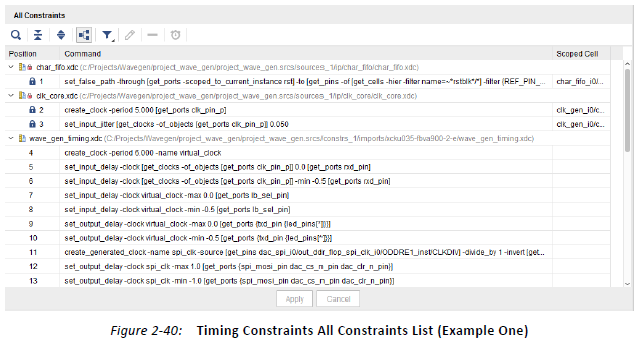

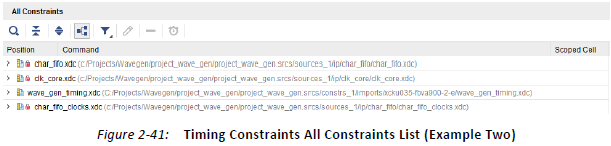

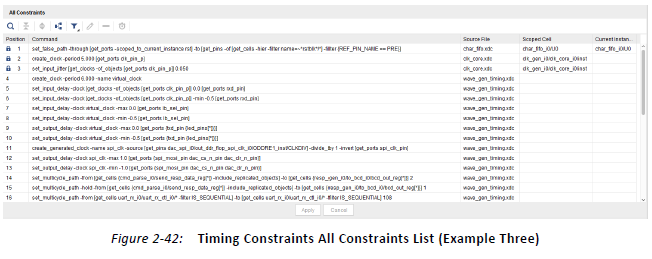

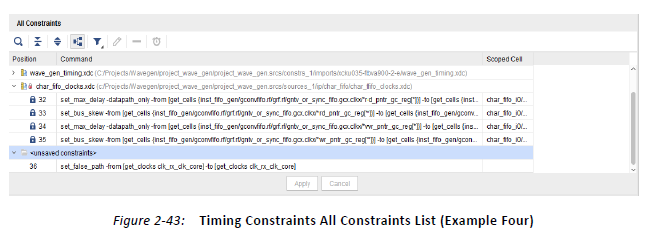

Ģr(sh©¬)ą“╝s╩°ļŖūė▒ĒĖ±’@╩Š╠žČ©ŅÉą═Ą─╦∙ėą¼F(xi©żn)ėą╝s╩°Ą─įö╝Ü(x©¼)ą┼ŽóĪŻ╩╣ė├Ģr(sh©¬)ą“╝s╩°ļŖūė▒ĒĖ±▓ķ┐┤║═ŠÄ▌ŗ╝s╩°▀xĒŚ(xi©żng)ĪŻ

įōąĪĮMĄ─ūŅ║¾ā╔┴ą’@╩ŠŻ║

•į┤╬─╝■Ż║╝s╩°üĒ(l©ói)ūįĄ─XDC╬─╝■╗“Tcl─_▒ŠĄ─├¹ĘQ

•Scoped CellŻ║æ¬(y©®ng)ė├╝s╩°Ģr(sh©¬)Ą─«ö(d©Īng)Ū░īŹ(sh©¬)└²Ą─├¹ĘQĪŻ ┤╦├¹ĘQ═©│Żī”(du©¼)æ¬(y©®ng)ė┌╩╣ė├īŻė├╝s╩°é„▀fĄ─IPīŹ(sh©¬)└²ĪŻ ėąĻP(gu©Īn)Ė³ČÓą┼ŽóŻ¼šł(q©½ng)ģóķå╝s╩°ĘČć·Ż¼Ą┌67Ēō(y©©)ĪŻ

═©▀^(gu©░)ļpō¶ļŖūė▒ĒĖ±Ą─ūŅ║¾ę╗ąąŻ¼┐╔ęįäō(chu©żng)Į©╦∙▀xŅÉą═Ą─ą┬╝s╩°ĪŻ īó┤“ķ_ŽÓæ¬(y©®ng)Ą─╝s╩°äō(chu©żng)Į©ī”(du©¼)įÆ┐“Ż¼─·┐╔ęį╠Ņīæą┬╝s╩°Ą─įö╝Ü(x©¼)ą┼ŽóĪŻ å╬ō¶Ī░┤_Č©Ī▒īó╝s╩°æ¬(y©®ng)ė├ė┌ā╚(n©©i)┤µ▓óĻP(gu©Īn)ķ]

┤░┐┌ĪŻ ļŖūė▒ĒĖ±ųąĄ─ą┬ąą’@╩Šą┬Ą─╝s╩°ą┼ŽóĪŻ

─·┐╔ęį═©▀^(gu©░)ų▒Įėį┌ļŖūė▒ĒĖ±ųąą▐Ė─ųĄüĒ(l©ói)ŠÄ▌ŗ╚╬║╬¼F(xi©żn)ėą╝s╩°ĪŻ

═Ļ│╔ŠÄ▌ŗ║¾Ż¼å╬ō¶Ī░æ¬(y©®ng)ė├Ī▒ęįīóą▐Ė─Ą─╝s╩°æ¬(y©®ng)ė├ė┌ā╚(n©©i)┤µĪŻ

ųžę¬ą┼ŽóŻ║æ¬(y©®ng)ė├ą┬╝s╩°╗“ęčą▐Ė─╝s╩°▓╗Ģ■(hu©¼)īóŲõ▒Ż┤µį┌XDC╬─╝■ųąĪŻ ─·▒žĒÜå╬ō¶Ī░▒Ż┤µ╝s╩°Ī▒ęį▒Ż┤µ╦³ĪŻ

ųžę¬ą┼ŽóŻ║¤o(w©▓)Ę©ŠÄ▌ŗ╗“äh│²IP╝s╩°ĪŻ ꬹ▐Ė─╩╣ė├IP╠ß╣®Ą─╝s╩°Ż¼▒žĒÜĮ¹ė├ŽÓæ¬(y©®ng)Ą─IP XDC╬─╝■Ż¼īó╝s╩°Å═(f©┤)ųŲĄĮXDC╬─╝■Ż¼╚╗║¾Ė∙ō■(j©┤)ąĶꬊÄ▌ŗ╝s╩°ĪŻ

Constraints Creation, Grouped by Category

When you select a constraint type, the corresponding spreadsheet appears on the right

sub-window panel. This allows you to view all the constraints of the same type that have

already been created.

╝s╩°äō(chu©żng)ū„Ż¼░┤ŅÉäeĘųĮM

▀xō±╝s╩°ŅÉą═Ģr(sh©¬)Ż¼ŽÓæ¬(y©®ng)Ą─ļŖūė▒ĒĖ±īó’@╩Šį┌ėęé╚(c©©)ūė┤░┐┌├µ░Õ╔ŽĪŻ ▀@į╩įS─·▓ķ┐┤ęčäō(chu©żng)Į©Ą─ŽÓ═¼ŅÉą═Ą─╦∙ėą╝s╩°ĪŻ

ę¬?ji©Żng)?chu©żng)Į©ą┬╝s╩°Ż¼šł(q©½ng)ļpō¶─┐ś╦(bi©Īo)╝s╩°Ą─├¹ĘQĪŻ ╩╣ė├ī”(du©¼)įÆ┐“┐╔ęįųĖČ©├┐éĆ(g©©)▀xĒŚ(xi©żng)Ą─ųĄĪŻ å╬ō¶Ī░┤_Č©Ī▒║¾Ż¼įō╣żŠ▀īół╠(zh©¬)ąąęįŽ┬▓┘ū„Ż║

1.“×(y©żn)ūCšZ(y©│)Ę©ĪŻ

2.īóšZ(y©│)Ę©æ¬(y©®ng)ė├ė┌ā╚(n©©i)┤µĪŻ

3.į┌ļŖūė▒ĒĖ±Ą──®╬▓╠Ē╝ėą┬╝s╩°ĪŻ

4.į┌═Ļš¹╝s╩°┴ą▒ĒĄ──®╬▓╠Ē╝ėą┬╝s╩°ĪŻ

╦∙ėą╝s╩°

┤░┐┌Ąū▓┐’@╩Šā╚(n©©i)┤µųą╝ė▌dĄ─╝s╩°Ą─═Ļš¹┴ą▒ĒŻ¼ŲõĒśą“┼cæ¬(y©®ng)ė├Ą─Ēśą“ŽÓ═¼ĪŻ ╝s╩°Ė∙ō■(j©┤)XDC╬─╝■╗“╦³éā╦∙į┤ūįĄ─Tcl─_▒Š▀M(j©¼n)ąąĘųĮMĪŻ «ö(d©Īng)XDC╬─╝■Ą─ĘČć·Ž▐Č©×ķ

╠žČ©Ą─Ęųīėå╬į¬Ė±Ż¼å╬į¬Ė±├¹ĘQ’@╩Šį┌╬─╝■├¹┼į▀ģĪŻ

─·┐╔ęįš╣ķ_║═š█»B├┐éĆ(g©©)ĻP(gu©Īn)┬ō(li©ón)į┤╬─╝■Ą─╝s╩°Ż¼ę▓┐╔ęį═©▀^(gu©░)å╬ō¶├µ░Õū¾é╚(c©©)Ą─ā╔éĆ(g©©)ŽÓæ¬(y©®ng)░┤Ōo═Ļ╚½š╣ķ_║═š█»B╝s╩°ĪŻ

╠ß╩ŠŻ║š█»BęĢłD╠ß╣®┴╦į┌ā╚(n©©i)┤µųą╝ė▌d──ą®╝s╩°╬─╝■ęį╝░╩╣ė├ĘČć·ÖC(j©®)ųŲĄ─╬╗ų├Ą─║å(ji©Żn)ę¬Ė┼╩÷ĪŻ ═©▀^(gu©░)report_compile_order -constraints├³┴Ņ┐╔ęį½@Ą├ŽÓ═¼Ą─ą┼ŽóĪŻ

╚ĪŽ¹▀xō±Ī░░┤į┤ĘųĮMĪ▒łDś╦(bi©Īo)Ż¼īóęĢłDŪąōQĄĮę╗éĆ(g©©)▒ĒŻ¼Ųõųąį┤╝s╩°╬─╝■║═ū„ė├ė“å╬į¬Ė±ą┼Žó’@╩Šį┌ėęé╚(c©©)ā╔┴ąųąĪŻ

ę¬?ji©Żng)h│²╝s╩°Ż¼šł(q©½ng)▀xō±╦³▓óå╬ō¶X.

•ę¬ŠÄ▌ŗĘŪų╗ūxĄ─╝s╩°Ż¼šł(q©½ng)╩╣ė├ļŖūė▒ĒĖ±ęĢłDĪŻ į┌╣żŠ▀ūóāį(c©©)┴╦Ė³Ė─║¾Ż¼▒žĒÜå╬ō¶Ī░æ¬(y©®ng)ė├Ī▒ęį╦óą┬ā╚(n©©i)┤µųąĄ─╝s╩°ĪŻ

•ę¬╠Ē╝ėą┬╝s╩°Ż¼šł(q©½ng)╩╣ė├Ū░├µ╦∙╩÷Ą─ī”(du©¼)įÆ┐“Ż¼╗“į┌Tcl┐žųŲ┼_(t©ói)ųąµI╚ļ╝s╩°ĪŻ ą┬╝s╩°į┌├¹×ķ<unsaved_constraints>Ą─roupųą│÷¼F(xi©żn)į┌┴ą▒ĒĄ──®╬▓ĪŻ

▒Ż┤µ╝s╩°Ģr(sh©¬)Ż¼ą┬╝s╩°īó▒Ż┤µį┌ś╦(bi©Īo)ėø×ķ─┐ś╦(bi©Īo)Ą─XDC╬─╝■Ą──®╬▓ĪŻ ╚ń╣¹┼cā╚(n©©i)┤µųąĄ─įO(sh©©)ėŗ(j©¼)ĻP(gu©Īn)┬ō(li©ón)Ą─╝s╩°╝»ųąø]ėą─┐ś╦(bi©Īo)XDC╬─╝■Ż¼╗“š▀╝s╩°╝»ųąų╗ėąę╗éĆ(g©©)Tcl─_▒ŠŻ¼ätĢ■(hu©¼)╠ß╩Š─·ųĖČ©▒Ż┤µ╝s╩°Ą─╬╗ų├ĪŻ

Regularly save your constraints. Click Save, or select File > Constraints > Save.

ųžę¬ą┼ŽóŻ║¤o(w©▓)Ę©īóą┬╝s╩°║═ęčą▐Ė─╝s╩°▒Ż┤µ╗žTcl─_▒ŠĪŻ

Š»ĖµŻĪ ╚ń╣¹╔ą╬┤æ¬(y©®ng)ė├Timing Constraints┤░┐┌ųąĄ─╚╬║╬╝s╩°Ż¼šł(q©½ng)▓╗ę¬į┌Tcl┐žųŲ┼_(t©ói)ųą▌ö╚ļą┬╝s╩°ĪŻ ŠÄ▌ŗŲ„ųąĄ─ūŅĮK╝s╩°Ēśą“┐╔─▄┼cā╚(n©©i)┤µųąĄ─╝s╩°Ēśą“▓╗═¼ĪŻ ×ķ▒▄├Ō╗ņŽ²Ż¼├┐┤╬ŠÄ▌ŗ¼F(xi©żn)ėą╝s╩°Ģr(sh©¬)Č╝▒žĒÜųžą┬æ¬(y©®ng)ė├╦∙ėą╝s╩°ĪŻ

╔Žę╗Ų¬Ż║╩╣ė├╝s╩°

Ž┬ę╗Ų¬Ż║N76E003Ą─Łh(hu©ón)Š│┤ŅĮ©

Æ▀┤aĻP(gu©Īn)ūó╬ęéā

Ó]ŽõŻ║ivy@yingtexin.net

ĄžųĘŻ║╔Ņ█┌╩ą²ł╚Aģ^(q©▒)├±ų╬ĮųĄ└├±ų╬┤¾Ą└973╚f(w©żn)▒ŖØÖ(r©┤n)žSäō(chu©żng)śI(y©©)ł@AŚØ2śŪA09