ę╗ĘN£p╔┘VDMOS╝─╔·ļŖ╚▌Ą─ą┬ĮY(ji©”)śŗ(g©░u)

ę╗ĘN£p╔┘VDMOS╝─╔·ļŖ╚▌Ą─ą┬ĮY(ji©”)śŗ(g©░u)

0 ę² čį

VDMOS┼cļpśOŠ¦¾w╣▄ŽÓ▒╚Ż¼╦³Ą─ķ_ĻP(gu©Īn)╦┘Č╚┐ņŻ¼ķ_ĻP(gu©Īn)ōp║─ąĪŻ¼▌ö╚ļļŖūĶĖ▀Ż¼“ī(q©▒)äėļŖ┴„ąĪŻ¼Ņl┬╩╠žąį║├Ż¼┐ńī¦(d©Żo)Ė▀Č╚ŠĆąįĄ╚ā×(y©Łu)³c(di©Żn)ĪŻ╠žäeųĄĄ├ųĖ│÷Ą─╩ŪŻ¼╦³Š▀ėąžō(f©┤)£žČ╚ŽĄöĄ(sh©┤)Ż¼ø]ėąļpśO╣”┬╩╣▄Ą─Č■┤╬ō¶┤®å¢Ņ}Ż¼░▓╚½╣żū„ģ^(q©▒)┤¾ĪŻę“┤╦Ż¼▓╗šō╩Ūķ_ĻP(gu©Īn)æ¬(y©®ng)ė├▀Ć╩ŪŠĆąįæ¬(y©®ng)ė├Ż¼VDMOSČ╝╩Ū└ĒŽļĄ─╣”┬╩Ų„╝■ĪŻVDMOSĄ─ķ_ĻP(gu©Īn)╦┘Č╚╩Ūį┌Ė▀Ņlæ¬(y©®ng)ė├ĢrĄ─ę╗éĆųžę¬Ą─ģóöĄ(sh©┤)Ż¼ę“┤╦╠ß│÷ę╗ĘN£pąĪ╝─╔·ļŖ╚▌Ą─ą┬ą═VDMOSĮY(ji©”)śŗ(g©░u)ĪŻ

1 ╗∙▒ŠįŁ└Ē

╣”┬╩VDMOSĄ─ķ_ĻP(gu©Īn)╠žąį╩Ūė╔Ųõ▒Šš„ļŖ╚▌║═╝─╔·ļŖ╚▌üĒøQČ©Ą─ĪŻVDMOSĄ─ļŖ╚▌ų„ę¬ė╔╚²éĆ▓┐Ęų¢┼į┤ļŖ╚▌Cgs¢┼┬®ļŖ╚▌Cgdęį╝░į┤┬®ļŖ╚▌CdsĮM│╔Ż¼╚ńłD1╦∙╩ŠĪŻļŖ╚▌Ą─│õĘ┼ļŖ╩ŪŽ▐ųŲŲõķ_ĻP(gu©Īn)╦┘Č╚Ą─ų„ę¬ę“╦žĪŻ¢┼į┤ų«ķgĄ─ļŖ╚▌╩Ūė╔╚²éĆ▓┐ĘųĮM│╔Ż¼╝┤Ż║

Cgs=Cgs(N+)+Cgs(P)+Cgs(M)

Cgs(N+)╩Ū¢┼į┤Į╗»BļŖ╚▌Ż╗Cgs(M)╩Ū¢┼┼cį┤Įī┘ķgĄ─ļŖ╚▌Ż╗Cgs(P)╩Ū¢┼┼cP-baseų«ķgĄ─ļŖ╚▌ĪŻ▀@╚²éĆļŖ╚▌Ą─┤¾ąĪČ╝╩Ūė╔VDMOS▒Š╔ĒįO(sh©©)ėŗ(j©¼)╔ŽĄ─ģóöĄ(sh©┤)øQČ©Ą─Ż¼ūŅų„ę¬╚ĪøQė┌Įķ┘|(zh©¼)īėĄ─║±Č╚ĪŻ

¢┼┬®ų«ķgĄ─ļŖ╚▌Cgd╩Ūā╔éĆļŖ╚▌Ą─┤«┬ō(li©ón)Ż║![]()

«ö(d©Īng)¢┼ē║╬┤▀_(d©ó)ĄĮķōųĄļŖē║ĢrŻ¼Ų»ęŲģ^(q©▒)┼cP-baseą╬│╔Ą─║─▒MīėĮY(ji©”)║Žį┌ę╗ŲŻ¼ą╬│╔├µĘe║▄┤¾Ą─║─▒MīėļŖ╚▌Ż¼¢┼Ž┬Ų»ęŲģ^(q©▒)┐šķgļŖ║╔║─▒Mģ^(q©▒)ļŖ╚▌Cgd(dep)ų╗╩ŪŲõųąę╗▓┐ĘųŻ¼┤╦Ģr║─▒MīėīÆČ╚ūŅ┤¾Ż¼║─▒MļŖ╚▌ūŅąĪĪŻ«ö(d©Īng)¢┼ē║▀_(d©ó)ĄĮķōųĄļŖē║║¾Ż¼Ų„╝■ķ_åóĢrŻ¼┬®ģ^(q©▒)ļŖä▌ĮĄĄ═Ż¼║─▒MīėīÆČ╚£pąĪŻ¼Cgd(dep)čĖ╦┘į÷┤¾ĪŻ

┬®į┤ų«ķgĄ─ļŖ╚▌Cds╩Ūę╗éĆPNĮY(ji©”)ļŖ╚▌Ż¼╦³Ą─┤¾ąĪ╩Ūė╔Ų„╝■į┌į┤┬®ų«ķg╦∙╝ėĄ─ļŖē║VDS╦∙øQČ©Ą─ĪŻ

ę╗░ŃVDMOSČ╝░³║¼┴╦Cgs,Cgd║═CdsŻ¼Ą½╩Ū╣”┬╩VDMOSČ╝▓╗╩Ū▓╔ė├▀@╚²éĆļŖ╚▌ū„ģó┐╝Ż¼Č°╩Ū▓╔ė├CissŻ¼Coss║═Crssū„×ķįu╣└VDMOSŲ„╝■Ą─ļŖ╚▌ąį─▄Ż¼CissŻ¼Coss║═CrssģóöĄ(sh©┤)ĘųäeČ©┴x×ķŻ║▌ö╚ļļŖ╚▌Ż║Ciss=Cgs+Cgd▌ö│÷ļŖ╚▌Ż║Coss=Cds+CgdŻ╗Ę┤üļŖ╚▌Ż║Crss=CgdĪŻīŹ(sh©¬)ļHųą▓╔ė├CissŻ¼Coss║═Crssū„×ķ║Ō┴┐VDMOSŲ„╝■Ņl┬╩╠žąįĄ─ģóöĄ(sh©┤)Ż¼╦³éā▓ó▓╗╩ŪČ©ųĄŻ¼Č°╩ŪļSų°Ųõ═Ō▓┐╩®╝ėĮoŲ„╝■▒Š╔ĒĄ─ļŖē║ūā╗»Ą─ĪŻ

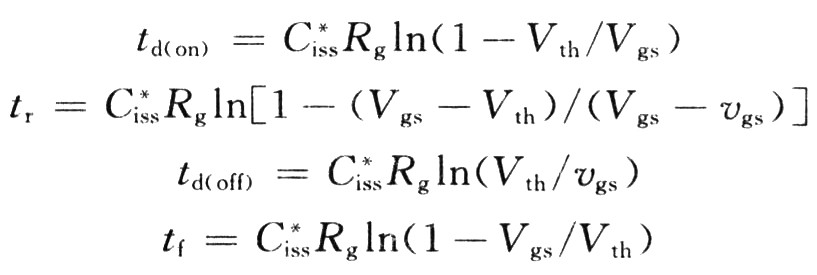

VDMOSĄ─ķ_åóčė▀tĢrķgtd(on)Īó╔Ž╔²ĢrķgtrĪóĻP(gu©Īn)öÓčė▀tĢrķgtd(off)ĪóŽ┬ĮĄĢrķgtfĄ─ĻP(gu©Īn)ŽĄ╩Į┐╔Ęųäe▒Ē▀_(d©ó)×ķŻ║

╩ĮųąŻ║Rg×ķķ_ĻP(gu©Īn)£yįćļŖ┬ĘųąŲ„╝■═ŌĮė?x©┤n)┼ļŖūĶŻ╗Vth×ķķōųĄļŖē║Ż╗Vgs╩Ū═Ō╝ė?x©┤n)┼į┤ļŖē║Ż╗vgs╩Ū╩╣Ų„╝■┬®į┤ļŖē║Ž┬ĮĄĄĮ═Ō╝ėųĄ10ŻźĢrĄ─¢┼į┤ļŖē║Ż╗Ciss*╩ŪŲ„╝■Ą─▌ö╚ļļŖ╚▌Ż╗į┌td(on)║═td(off)╩ĮųąŻ║Ciss*=Cgs+CgdŻ╗į┌tr║═tf╩ĮųąŻ║Ciss*=Cgs+(1+k)Cgd(┐╝æ]├▄└šą¦æ¬(y©®ng))ĪŻė╔╔Ž╩÷ĻP(gu©Īn)ŽĄ╩Į┐╔ęŖŻ¼Cgdų▒Įėė░ĒæŲ„╝■Ą─▌ö╚ļļŖ╚▌║═ķ_ĻP(gu©Īn)ĢrķgŻ¼Cgd═©▀^├▄└šą¦æ¬(y©®ng)╩╣▌ö╚ļļŖ╚▌į÷┤¾Ż¼Å─Č°╩╣Ų„╝■╔Ž╔²Ģrķgtr║═Ž┬ĮĄtfĢrķgūā┤¾Ż¼ę“┤╦£pąĪ¢┼┬®ļŖ╚▌Cgdė╚×ķųžę¬ĪŻ

2 ą┬ĮY(ji©”)śŗ(g©░u)Ą─╠ß│÷

Ė∙ō■(j©┤)╔Ž├µī”VDMOSļŖ╚▌Ą─Ęų╬÷Ż¼╠ß│÷ę╗ĘNą┬Ą─ĮY(ji©”)śŗ(g©░u)ęį£p╔┘Ų„╝■Ą─╝─╔·ļŖ╚▌ĪŻė╔Ęų╬÷┐╔Ą├│÷Ż¼¢┼Ž┬║─▒MīėĄ─ą╬ĀŅī”VDMOSļŖ╚▌ėą▌^┤¾ė░ĒæŻ¼ūŅų„ę¬ė░ĒæCgdĪŻ

łD2ųąĮo│÷┴╦ą┬Ą─VDMOSå╬į¬AŻ¼į┌VDMOSneckģ^(q©▒)ė“öÓķ_ČÓŠ¦╣ĶŚlŻ¼═¼Ģrį┌öÓķ_╠Äūó╚ļę╗Č©Ą─Pą═ģ^(q©▒)Ż¼Ė─ūāVDMOS¢┼Ž┬║─▒Mģ^(q©▒)Ą─ą╬ĀŅĪŻ▀@ĘNą┬ĮY(ji©”)śŗ(g©░u)Ż¼į┌ę╗Č©│╠Č╚╔Ž╝ė┤¾║─▒Mģ^(q©▒)Ą─īÆČ╚Ż¼Å─Č°£pąĪCgdĪŻ╚ńłD2ĮY(ji©”)śŗ(g©░u)ųąPodyŽ┬P-ģ^(q©▒)ūó╚ļ?y©▓n)^(q©▒)ė“?y©żn)ķneckģ^(q©▒)ųąķg3”╠mŻ¼ūó╚ļ─▄┴┐╩Ū40 keVŻ¼ūó╚ļä®┴┐╩Ū1e13Ī¬3 cmŻ¼é„Įy(t©»ng)ĮY(ji©”)śŗ(g©░u)ČÓŠ¦╣Ķ¢┼═Ļ╚½Ė▓╔wP-bodyŹuķgŲ»ęŲģ^(q©▒)Ż¼š²╩Ūė╔ČÓŠ¦╣Ķ¢┼║═Ų»ęŲģ^(q©▒)Ą─Į╗»Bą╬│╔Ą─¢┼┬®ļŖ╚▌į┌│õļŖĢrąĶ┤¾┴┐ļŖ║╔Ż¼ī¦(d©Żo)ų┬Ų„╝■ķ_ĻP(gu©Īn)ōp║─║▄┤¾Ż¼ą┬ĮY(ji©”)śŗ(g©░u)īóČÓŠ¦¢┼║═Ų»ęŲģ^(q©▒)Ą─Į╗»B▓┐ĘųęŲ│²Ż¼┐╔ęį┤¾┤¾ĮĄĄ═¢┼ļŖ║╔Ż¼╠ßĖ▀Ų„╝■Ą─äėæB(t©żi)ąį─▄ĪŻ

3 ą┬ĮY(ji©”)śŗ(g©░u)Ą──ŻöMĮY(ji©”)╣¹

łD3Įo│÷┴╦ą┬ą═ĮY(ji©”)śŗ(g©░u)AĄ─╝─╔·ļŖ╚▌─ŻöMĮY(ji©”)╣¹Ż¼Å──ŻöMĮY(ji©”)╣¹üĒ┐┤Ż¼ą┬ą═ĮY(ji©”)śŗ(g©░u)Aį÷┤¾┴╦¢┼Ž┬║─▒Mģ^(q©▒)īÆČ╚Ż¼Ė─ūā┴╦¢┼Ž┬║─▒Mģ^(q©▒)Ą─ą╬ĀŅŻ¼£pąĪ┴╦¢┼┬®ļŖ╚▌Cgdī”▌ö╚ļļŖ╚▌Īó▌ö│÷ļŖ╚▌ø]ėą▌^┤¾ė░ĒæŻ¼į┌ę╗Č©│╠Č╚╔Ž£pąĪ┴╦Ę┤üļŖ╚▌ĪŻ

¢┼ļŖ║╔╩Ū▒╚▌ö╚ļļŖ╚▌Ė³ėąė├Ą─ģóöĄ(sh©┤)Ż¼Å─ļŖ┬ĘįO(sh©©)ėŗ(j©¼)Ą─ĮŪČ╚Ż¼ė╔Qg=Igt┐╔Ą├ĄĮ╩╣Ų„╝■į┌└ĒŽļķ_åóĢrķgā╚(n©©i)╦∙ąĶĄ─¢┼ļŖ┴„ųĄĪŻ¢┼ļŖ║╔Qg╩Ū╣”┬╩MOSFETā╔éĆūŅųžę¬Ą─ģóöĄ(sh©┤)ų«ę╗(┴Ēę╗ģóöĄ(sh©┤)×ķRon)ĪŻ╩╣ė├ĘŪ┴ŃĄ─Vds╠ß╣®Qg-VgsŪ·ŠĆęčĮø(j©®ng)│╔×ķę╗ĘN╣żśI(y©©)ś╦(bi©Īo)£╩(zh©│n)ĪŻį┌Ū·ŠĆ└’░³║¼╬ÕĘNą┼ŽóŻ║╣▓į┤▌ö╚ļļŖ╚▌CissŻ╗╣▓į┤Ę┤Ž“é„▌öļŖ╚▌CrssŻ╗╩╣Ų„╝■ķ_åó▒žĒÜ╝ėį┌¢┼╔ŽĄ─ļŖ║╔┴┐Ż╗Ą├ĄĮŲ„╝■└ĒŽļķ_ĻP(gu©Īn)╦┘Č╚╦∙ąĶĄ─¢┼ļŖ║╔Ż╗Ų„╝■į┌ķ_ĻP(gu©Īn)Ų┌ķg╦∙ōp║─Ą──▄┴┐ĪŻ

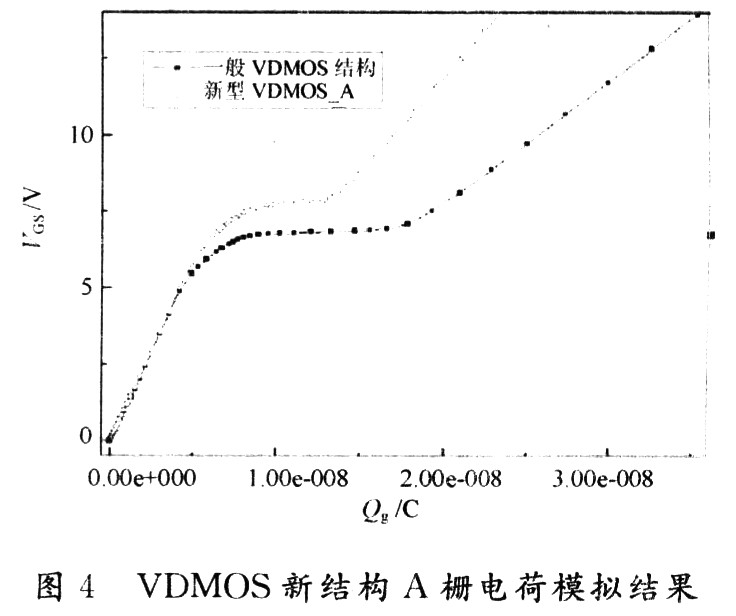

ļŖį┤ļŖ┬ĘįO(sh©©)ėŗ(j©¼)╣ż│╠Ĥ╩╣ė├▀@ą®ą┼ŽóįO(sh©©)ėŗ(j©¼)“ī(q©▒)äėļŖ┬ĘŻ¼▓ó╣└ųŁŲ„╝■ąį─▄ĪŻ▓╔ė├TCAD(ISE)ī”ą┬ą═ĮY(ji©”)śŗ(g©░u)A▀M(j©¼n)ąą┴╦─ŻöMŻ¼─ŻöMĮY(ji©”)╣¹╚ńłD4╦∙╩ŠĪŻ

┐╔ęį├„’@┐┤│÷ą┬ą═ĮY(ji©”)śŗ(g©░u)AĄ─¢┼ļŖ║╔├„’@▒╚ę╗░ŃĮY(ji©”)śŗ(g©░u)Ą─¢┼ļŖ║╔ąĪ║▄ČÓŻ¼QgČ©┴x×ķVgs=12 VĢr¢┼╔Ž╦∙┤µ┘AĄ─ļŖ║╔Ż¼ą┬ą═ĮY(ji©”)śŗ(g©░u)A║═ę╗░ŃVDMOSĮY(ji©”)śŗ(g©░u)¢┼ļŖ║╔Ęųäe×ķ20Ż«25 nC║═30Ż«57 nCŻ¼£pąĪ┴╦33Ż«67ŻźĪŻ

4 ĮY(ji©”) šZ

▒Š╬─╠ß│÷ę╗ĘN£pąĪVDMOS╝─╔·ļŖ╚▌Ż¼╠ßĖ▀ŲõäėæB(t©żi)╠žąįĄ─ą┬ĮY(ji©”)śŗ(g©░u)ĪŻ▓óė├TCAD(ISE)▄ø╝■ī”Ųõ─ŻöMĪŻÅ──ŻöMĘų╬÷ĮY(ji©”)╣¹┐╔┐┤│÷Ż¼ą┬ą═ĮY(ji©”)śŗ(g©░u)A┼cé„Įy(t©»ng)VDMOSŽÓ▒╚Ż¼─▄ėąą¦£pąĪĘ┤üļŖ╚▌╝░¢┼ļŖ║╔Ż¼╠ßĖ▀VDMOSŲ„╝■Ą─ķ_ĻP(gu©Īn)╦┘Č╚Ż¼╠ßĖ▀Ų„╝■Ą─äėæB(t©żi)ąį─▄ĪŻ

ŠÄ▌ŗŻ║admin ūŅ║¾ą▐Ė─ĢrķgŻ║2017-09-05