三星的14nm LPE工藝到底有啥特點(diǎn)?

三星(Samsung)即將量產(chǎn)用于其Exynos 8 SoC的14nmLow Power Plus (LPP)制程,這項(xiàng)消息持續(xù)引發(fā)一些產(chǎn)業(yè)媒體的關(guān)注。三星第二代14nm LPP制程為目前用于其Exynos 7 SoC與蘋果(Apple) A9 SoC的第一代14nm Low Power Early (LPE)制程提供了進(jìn)一步的更新。

業(yè)界目前共有三座代工廠有能力制造這種鰭式場效電晶體(FinFET):英特爾(Intel)、三星和臺(tái)積電(TSMC)。TechInsights曾經(jīng)在去年五月剖析用于Exynos 7420 SoC的三星14nm LPE制程,當(dāng)時(shí)在討論這項(xiàng)用于制造電晶體的制程技術(shù)時(shí)仍有所限制。而今,在幾乎過了一年后,大家已經(jīng)開始討論三星的升級(jí)版14nm LPP FinFET制程了。

然而,預(yù)計(jì)要到今年春季末取得三星的Exynos 8890 SoC或高通(Qualcomm)的Snapdragon 820 SoC樣本后,才可能完全掌握這項(xiàng)制程技術(shù)的細(xì)節(jié)。不過,我們可以進(jìn)一步揭密用于Exynos 7420 SoC的更多14 nm LPE制程技術(shù)細(xì)節(jié),同時(shí)也有助于預(yù)期下一代LPP制程的新進(jìn)展。

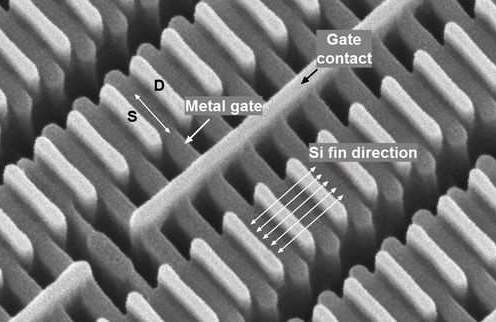

我們從觀察典型三星14 nm LPE FinFET電晶體的SEM側(cè)視圖開始(圖1)。電晶體通道如同矽鰭片(Si Fin)般地形成,而非由圖片的左下角向右上方生長。這些鰭片被埋在電介質(zhì)下方而無法直接看到,因此,我們以箭號(hào)指示其方向。金屬閘就位于正交方向,覆蓋在整個(gè)鰭片的兩側(cè)與頂部。在閘電極的任一側(cè)可看到較大的源極與汲極(S/D)觸點(diǎn)。

圖1:三星14 nm LPE FinFET電晶體的側(cè)視SEM圖

(來源:TechInsights)

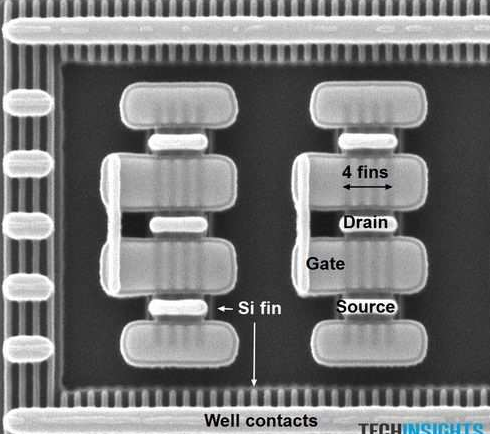

也許從另一張三星FinFET電晶體的平面圖(圖2)中能更清楚的看到閘極與鰭片的布局。四片矽鰭以垂直的方向排列在水平方向的金屬閘極正下方。這兩種電晶體結(jié)構(gòu)周圍都圍繞著一個(gè)阱觸環(huán),用于隔離其與晶片上的其他電路部份。

該鰭片間距約有49nm,必須采用雙重圖案制程來制造。在此提供了兩種選擇:英特爾所使用的‘雙微影蝕刻’(LELE),或是‘自對(duì)準(zhǔn)雙微影圖案法’(SADP)。我們認(rèn)為三星采用了LELE制程為鰭片制圖,但最后還需要額外使用光罩與微影制程,才能中斷電晶體的兩端。

圖2:三星14nm FinFET電晶體的平面圖

(來源:TechInsights)

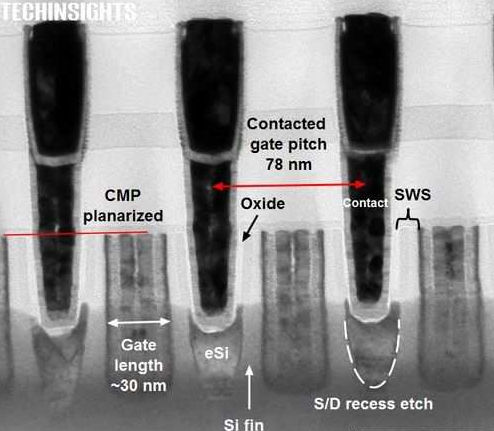

圖3是Exynos 7420所使用的典型NMOS電晶體之TEM橫截面圖,而且我們還注意到閘極長度經(jīng)測量約有30nm,這跟所宣稱的14 nm制程節(jié)點(diǎn)差距頗多,而在表1中所整理的英特爾和臺(tái)積電的情況也是一樣的。稍后我們將進(jìn)一步討論這個(gè)問題。

電晶體閘極使用替代性閘極制程制造,包括沈積犧牲層(通常為多晶矽)、圖案化與蝕刻,形成大約30個(gè)較寬的條形(stripe)區(qū)域。這些條形區(qū)域可定義出電晶體閘極長度。

圖3:三星Exynos 7420的NMOS電晶體橫截面圖

編輯:admin 最后修改時(shí)間:2017-09-05