��Ƭ�C��λ�·ԭ��D��

��λ�·����������늻��λ�^���У�����CPU�ď�λ��B(t��i)���@�Εr�g��(n��i)CPU���֏�λ��B(t��i)��������һ��늻�λ�ꮅ��������ֹCPU�l(f��)���e�`��ָ���(zh��)���e�`������Ҳ�������늴ż������ܡ�

�oՓ�Ñ�ʹ���ķN��͵Ć�Ƭ�C,��Ҫ�漰����Ƭ�C��λ�·���OӋ������Ƭ�C��λ�·�OӋ�ĺÉ�,ֱ��Ӱ푵�����ϵ�y(t��ng)�����Ŀɿ��ԡ��S���Ñ����OӋ���Ƭ�Cϵ�y(t��ng),���ڌ�����{(di��o)ԇ�ɹ���,�ڬF(xi��n)���s���F(xi��n)�ˡ����C�������������w���ȬF(xi��n)��,�@��Ҫ�dž�Ƭ�C�ď�λ�·�OӋ���ɿ�����ġ�

�����ď�λ��ʽ

��Ƭ�C�چ��ӕr����Ҫ��λ����ʹCPU��ϵ�y(t��ng)������̎�ڴ_���ij�ʼ��B(t��i)�����ij��B(t��i)�_ʼ������89ϵ�І�Ƭ�C�ď�λ��̖�Ǐ�RST���_ݔ�뵽оƬ��(n��i)��ʩ�����|�l(f��)���еġ���ϵ�y(t��ng)̎������������B(t��i)�r������ʎ����(w��n)�������RST���_����һ�����ƽ���S��2���C������(24����ʎ����)���ϣ��tCPU�Ϳ���푑�����ϵ�y(t��ng)��λ����Ƭ�Cϵ�y(t��ng)�ď�λ��ʽ�У��քӰ��o��λ����늏�λ

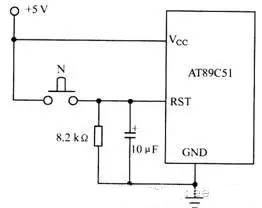

1���քӰ��o��λ

�քӰ��o��λ��Ҫ�˞��ڏ�λݔ���RST�ϼ�����ƽ���D1����һ����õ��k������RST�˺����ԴVcc֮�g��һ�����o�����˞鰴�°��o�r���tVcc��+5V�ƽ�͕�ֱ�Ӽӵ�RST�ˡ��քӰ��o��λ���·����ʾ�������˵Ą����ٿ�Ҳ��ʹ���o���ֽ�ͨ�_��(sh��)ʮ���룬���ԣ���ȫ�܉�M���λ�ĕr�gҪ��

�D1

�D2

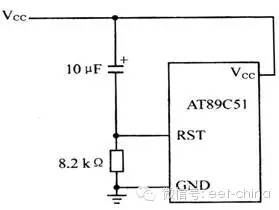

2����늏�λ

AT89C51����늏�λ�·��D2��ʾ��ֻҪ��RST��λݔ�����_�Ͻ�һ�����Vcc�ˣ��½�һ����赽�ؼ��ɡ�����CMOS�͆�Ƭ�C��������RST�˃�(n��i)����һ��������裬�ʿɌ��ⲿ���ȥ�������������ݜp��1µF����늏�λ�Ĺ����^�����ڼ�늕r����λ�·ͨ�^� �ݼӽoRST��һ���̕��ĸ��ƽ��̖���˸��ƽ��̖�S��Vcc����ݵij���^�̶���u���䣬��RST�˵ĸ��ƽ���m(x��)�r�gȡ�Q����ݵij�늕r�g�����˱��Cϵ�y(t��ng)�܉�ɿ��؏�λ��RST�˵ĸ��ƽ��̖��횾S������L�ĕr�g����늕r��Vcc�������r�g�s��10ms������ʎ��������r�gȡ�Q����ʎ�l�ʣ��羧���l�ʞ�10MHz������r�g��1ms�������l�ʞ�1MHz������r�g�t��10ms���ڈD2�ď�λ�·�У���Vcc��늕r����Ȼ��ʹRST��늉�Ѹ���½���0V���£����ǣ����ڃ�(n��i)���·���������ã��@��ؓ늉��������������a(ch��n)���p�������⣬�ڏ�λ���g���˿����_̎���S�C��B(t��i)����λ��ϵ�y(t��ng)���˿��Þ�ȫ��l(f��)���B(t��i)�����ϵ�y(t��ng)����늕r�ò�����Ч�ď�λ���t����Ӌ��(sh��)��PC���ò���һ�����m�ij�ֵ����ˣ�CPU���ܕ���һ��δ�����x��λ���_ʼ��(zh��)�г���

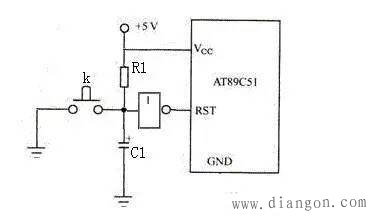

2���e������늏�λ

���õ���늻��_�P��λ�·��D3��ʾ����늺��������C3�ij�늺ͷ����T�����ã�ʹRST���m(x��)һ�Εr�g�ĸ��ƽ������Ƭ�C�����\�Ю��Еr������λ�IK�����_��Ҳ��ʹRST��һ�Εr�g�ĸ��ƽ���Ķ����F(xi��n)��늻��_�P��λ�IJ�����

����(j��)���H�����Ľ�(j��ng)����o���@�N��λ�·����ݡ���腢��ֵ��

�D3��C����1uF��Rl��lk��R2��10k

�D3 �e������늏�λ�·

����оƬ��λ�·��

��늏�λ�· �ڿ���ϵ�y(t��ng)�е������dž��ӆ�Ƭ�C�_ʼ�����������Դ����Լ������������r늉�������ɔ_�r���Դ����һЩ����(w��n)�������أ����Ƭ�C�����ķ�(w��n)���Կ�������ص�Ӱ푡���ˣ����Դ��늕r�ӕrݔ���oоƬݔ��һ��λ��̖���Ϗ�λ�·��һ�������ǣ��O(ji��n)ҕ���������r�Դ늉������Դ�Ю����t���M�Џ��Ə�λ����λݔ���_ݔ�����ƽ��Ҫ���m(x��)����(12/fc s)���߸����ָ�����ڣ���λ�����_ʼ��ʼ��оƬ��(n��i)���ij�ʼ��B(t��i)���ȴ�����ݔ����̖�������b��������̖�ȣ���

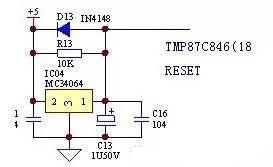

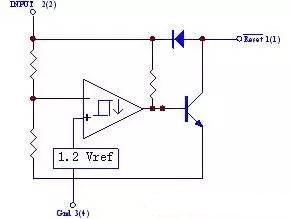

�D4 ��늏�λ�·ԭ��D

��늏�λ�·ԭ������

5V�Դͨ�^MC34064��2�_ݔ�룬1�_���ݔ��һ�������أ��|�l(f��)оƬ�ď�λ�_��늽����C13���{(di��o)��(ji��)��λ�ӕr�r�g�ġ����Դ�P���r��늽����C13�ϵĚ���늺�ͨ�^D13��MC34064��(n��i)���·���ɻ�·��ጷŵ�늺ɡ��Ԃ��´Ώ�λ���á�

�ġ���늏�λ�·���P�I������

�P�I��������MC34064 ��

�D6 ��(n��i)���Y����D

ݔ��ݔ������������

��늏�λ�·�P�I�c늚Ⅲ��(sh��)

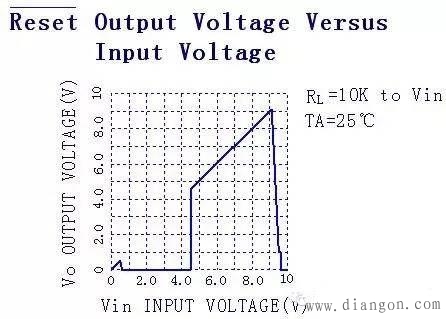

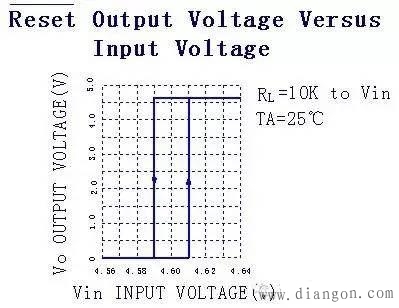

MC34064��ݔ���_1�_��ݔ��(��(w��n)��֮���ݔ��)���D��ʾ��

���O��Ƿ����λ�·

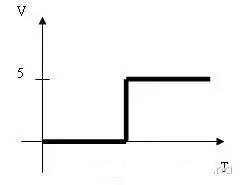

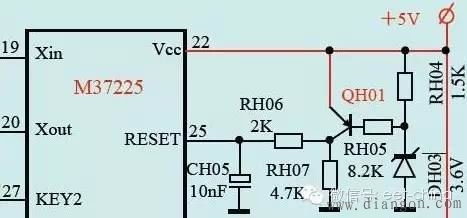

Ƿ����λ�·����ԭ�����D6��w ��ͨ�Դ����5V늉��ġ�0V���_ʼ������������3.6V֮ǰ����(w��n)�����O��DH03��̎�ڽ�ֹ��B(t��i)��QH01(PNP��)Ҳ̎�ڽ�ֹ��B(t��i)���o��λ늉�ݔ����w ����5V�Դ늉�����3.6V�Ժ�(w��n)�����O��DH03�������������ɶ�늉�����λ����3.6V������5V�Դ늉�����4.3V�Ժ�QH01�_ʼ��ͨ����λ늉��_ʼ�γɣ�����5V�Դ늉��ӽ���5V�r��QH01�ѽ�(j��ng)͌�ͨ����λ늉��_����(w��n)����B(t��i)��

�D6 Ƿ����λ�·�D

���T���͏�λ�·

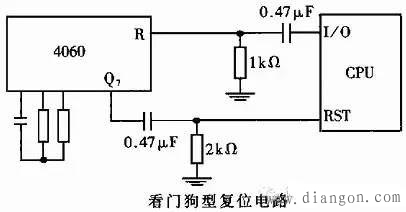

���T���͏�λ�·��Ҫ����CPU���������r,���r��λӋ��(sh��)��,ʹ��Ӌ��(sh��)����ֵ�����^ijһֵ;��CPU�������������r,����Ӌ��(sh��)�����ܱ���λ,�����Ӌ��(sh��)�����^ijһֵ,�Ķ��a(ch��n)����λ�}�_,ʹ��CPU�֏�����������B(t��i)�����͑��õ�Watchdog��λ�·��D7��ʾ���ˏ�λ�·�Ŀɿ�����Ҫȡ�Q��ܛ���OӋ,�������r���λ�·�l(f��)���}�_�ij�����ں�̎��һ���OӋ,���˶γ�����ڶ��r���Д�����ӳ����С�Ȼ��,�Еr�@�N�OӋ��Ȼ������������w������������ԭ����Ҫ�ǣ����������w���l(f��)���r���r����ʼ���Լ��_�Д�֮���Ԓ,�@�N�����w����r���п��ܲ�����Watchdog��λ�·У��������鶨�r���Д�һ���ڮa(ch��n)��,��ʹ��������,WatchdogҲ�ܱ�������λ�����������r�����A�O���OӋ���������ڳ�ʼ���r����ї�һ����ַ,�ڴ˵�ַ��(n��i)��(zh��)�е���һ�l�P�Д��һ�l��ѭ�h(hu��n)�Z�䡣�����в���������aռ�õĵ�ַ�M���ܵ����ӳ���ָ��RET���档�@��,���������w��,���M������Ŀ����Ԍ�������ӡ���һ���M������,���r��ֹͣ���������P�]�Д�,�Ķ�ʹWatchdog��λ�·���a(ch��n)��һ����λ�}�_��CPU��λ����Ȼ�@�N���g���ڌ��r���^���Ŀ��ƻ�̎��ܛ������һ�������y��

�D7 ���T���͏�λ�·

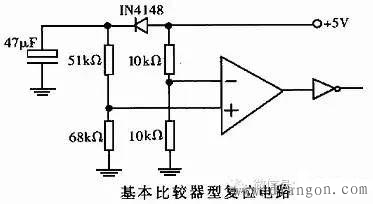

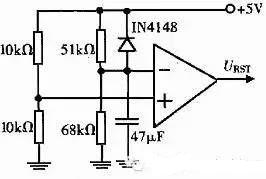

���^���͏�λ�·

���^���͏�λ�·�Ļ���ԭ����D8��ʾ����늏�λ�r,���ڽM����һ��RC��ͨ�W(w��ng)�j,���Ա��^��������ݔ��˵�늉���ؓ���ݔ��늉����tһ���r�g�������^����ؓ��˾W(w��ng)�j�ĕr�g����(sh��)�h�hС�������RC�W(w��ng)�j�ĕr�g����(sh��),���������늉�߀�]�г��^ؓ��늉��r,���^��ݔ�����ƽ,��(j��ng)��������a(ch��n)�����ƽ����λ�}�_�Č�����Ҫȡ�Q������늉��������ٶȡ�����ؓ��늉���늻�·�r�g����(sh��)�^��,��ˌ��Դ늉��IJ��Ӳ����С��������a(ch��n)�����¶��N�����F(xi��n)��1���Դ�����_�P�g��̫�̕r,��λ���ɿ�;��2�����Դ늉�������ӿ�F(xi��n)��r,��������ӿ��ʧ���ܮa(ch��n)����λ�}�_�����,�����M���^���ض��·,��D9��ʾ���@�����M�·����������һ�N�F(xi��n)��,���p�ٵڶ��N�F(xi��n)��Įa(ch��n)�������ˏص������@���N�F(xi��n)��,�������Ô�(sh��)��߉�ķ����c���^�����,�OӋ��D9��ʾ�ı��^���ض��·�����·�ԼӸ��M����������늏�λ�c���T����λ�·��ͬ��λ���·,�������ˏ�λ�Ŀɿ��ԡ�

�D8 ���^���͏�λ�·

�D9 ���M�ͱ��^���͏�λ�·

����admin ����ĕr�g��2018-05-08