╬óą═ėŗ╦ŃÖCĄ─ĮM│╔

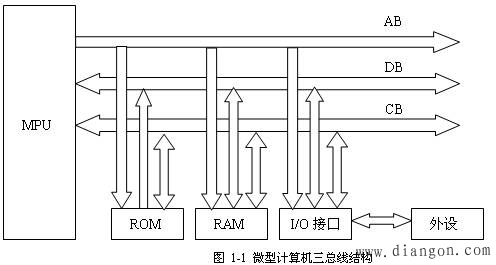

╬óą═ėŗ╦ŃÖCęį╬ó╠Ä└ĒŲ„×ķ║╦ą─Ż¼Ųõę╗┤¾╠ž³c╩Ū▓╔ė├┐éŠĆĮY(ji©”)śŗ(g©░u)Ż¼Ųõųą╚²┐éŠĆĮY(ji©”)śŗ(g©░u)ė╚×ķŲš▒ķŻ¼╚ńłD1-1╦∙╩ŠĪŻMPUŻ©╬ó╠Ä└ĒŲ„Ż®╩Ū═©▀^ABŻ©ĄžųĘ┐éŠĆŻ®ĪóDBŻ©öĄ(sh©┤)ō■(j©┤)┐éŠĆŻ®║═CBŻ©┐žųŲ┐éŠĆŻ®▀@╚²┐éŠĆ┼cROMŻ©ų╗ūx┤µā”Ų„Ż®║═RAMŻ©ļSÖC┤µā”Ų„Ż®╝░I/OŻ©▌ö╚ļ/▌ö│÷Ż®Įė┐┌ŽÓ▀BĄ─ĪŻį┌Ęų╬÷╬óą═ėŗ╦ŃÖC╗∙▒Š╣żū„įŁ└ĒŪ░Ż¼Ž╚ī”Ė„▓┐╝■▀MąąĮķĮBĪŻ1Ż«┤µā”Ų„

┤µā”Ų„ėųĘQā╚(n©©i)┤µ╗“ų„┤µŻ¼╩Ūėŗ╦ŃÖCĄ─┤µā”▓┐╝■Ż¼ė├üĒ┤µĘ┼│╠ą“║═öĄ(sh©┤)ō■(j©┤)(įŁ╩╝öĄ(sh©┤)ō■(j©┤)ĪóųąķgĮY(ji©”)╣¹╝░ūŅ║¾ĮY(ji©”)╣¹)ĪŻ╬óą═ėŗ╦ŃÖCā╚(n©©i)┤µė╔░ļī¦(d©Żo)¾w┤µā”Ų„ROM║═RAMĮM│╔Ż¼╦³éāČ╝╩Ū▓╔ė├┤¾ęÄ(gu©®)─Ż╗“│¼┤¾ęÄ(gu©®)─Ż╝»│╔ļŖ┬Ę╣ż╦ćųŲ│╔Ą─┤µā”Ų„ąŠŲ¼Ż¼Š▀ėą¾wĘeąĪĪóųž┴┐▌pĪó╝»│╔Č╚Ė▀Ą╚╠ž³cĪŻ

ų╗ūx┤µā”Ų„ROMŻ©Read Only MemoryŻ®╩Ūę╗ĘNį┌š²│Ż╣żū„Ģrų╗ūx▓╗─▄īæĄ─┤µā”Ų„Ż¼└¹ė├╠ž╩Ō╩ųČ╬īó╣╠Č©│╠ą“║═│ŻöĄ(sh©┤)īæ╚ļROMŻ¼ę╗Ą®īæ╚ļ▒Ń─▄ķLŲ┌▒Ż┤µ(öÓļŖę▓▓╗üG╩¦)Ż¼ąĶę¬Ģr╝┤┐╔ūx│÷╩╣ė├ĪŻROM═©│Żė├üĒ┤µĘ┼▓╗ūāĄ─│╠ą“Ż¼╚ń╗∙▒ŠI/O│╠ą“Īó▒O(ji©Īn)┐ž│╠ą“ĪóģRŠÄ│╠ą“ĪóĖ▀╝ēšZčį/ĮŌßī│╠ą“Ą╚Ż¼▀Ć┤µā”Ė„ĘN│Żė├öĄ(sh©┤)ō■(j©┤)║═▒ĒĖ±ĪŻROMĄ─ĘNŅÉ║▄ČÓŻ¼░┤ššŠÄ│╠ĘĮ╩ĮŻ¼ų╗ūx┤µā”Ų„ROMĘų×ķč┌─ŻROMĪó┐╔ŠÄ│╠ROMĪó┐╔▓┴│²EPROMĪóļŖ▓┴│²E2PROM║═ķW╦┘┤µā”Ų„Flash PEROMĪŻFlash PEROM┐╔ęįį┌ŠĆīæ╚ļŻ©ūįäė▓┴│²Ż®Ż¼▓óŪę┐╔ęį░┤Ēō▀B└m(x©┤)ūų╣Ø(ji©”)īæ╚ļŻ¼ūx│÷╦┘Č╚ę▓║▄┐ņĪŻ

ļSÖC┤µ╚Ī┤µā”Ų„RAMŻ©Random Access MemoryŻ®╩Ūę╗ĘNį┌š²│Ż╣żū„Ģr╝╚─▄ūxėų─▄īæĄ─┤µā”Ų„Ż«ė├üĒ┤µĘ┼ė├æ¶ę¬▀\ąąĄ─│╠ą“╝░▀\ąą│╠ą“╦∙ąĶĄ─įŁ╩╝öĄ(sh©┤)ō■(j©┤)ĪóųąķgĮY(ji©”)╣¹ĪóūŅĮKĮY(ji©”)╣¹ęį╝░īŹĢröĄ(sh©┤)ō■(j©┤)Ą╚ĪŻRAMųą┤µā”Ą─ą┼Žó▓╗─▄ķLŠ├▒Ż┤µŻ¼═ŻļŖ║¾▒Ń┴ó╝┤Ž¹╩¦Ż¼ę“┤╦ėųĘQ×ķęū╩¦ąį╗“ęūō]░l(f©Ī)ąį┤µā”Ų„ĪŻRAM┤µā”Ų„Ą─ęÄ(gu©®)Ė±ŲĘĘNę▓║▄ČÓŻ¼╚ń4KBĪó8KBĪó32KBĪó64KBĪó256KSBĪól MBĄ╚Ą╚ĪŻ░┤šš┤µā”ļŖ┬ĘĄ─▓╗═¼Ż¼ļSÖC┤µ╚Ī┤µā”Ų„RAMėų┐╔Ęų×ķäėæB(t©żi)RAMŻ©DRAMŻ®ĪóņoæB(t©żi)RAMŻ©SRAMŻ®ĪŻDRAMąŠŲ¼ęįMOS╣▄¢┼śOļŖ╚▌╩Ūʱ│õėąļŖ║╔üĒ┤µā”▀ē▌ŗ1╗“0ą┼ŽóŻ¼ąĶę¬═ŌĮė╦óą┬ļŖ┬ĘüĒų▄Ų┌ąįĄžī”ŲõļŖ║╔▀Mąą╦óą┬ęįŠS│ų╦³╦∙┤·▒ĒĄ─öĄ(sh©┤)ō■(j©┤)ĪŻSRAMąŠŲ¼ęįė|░l(f©Ī)Ų„üĒ┤µā”▀ē▌ŗ1╗“0ą┼ŽóŻ¼¤oąĶ╦óą┬ļŖ┬ĘĪŻSRAM▒╚DRAM╝»│╔Č╚Ą═Īó│╔▒ŠĖ▀Īó╦┘Č╚┐ņĪŻSRAM║═DRAMŠ∙×ķęū╩¦ąį┤µā”Ų„ĪŻ

ROM║═RAMĄ─ų„ę¬ģ^(q©▒)äeį┌ė┌Ż║ę╗╩ŪöÓļŖ║¾ROMā╚(n©©i)Ą─ą┼Žó▓╗üG╩¦Ż¼Č°RAMųąĄ─ą┼Žó┴ó╝┤Ž¹╩¦Ż╗Č■╩ŪūxŻ»īæĘĮ╩Į▓╗═¼Ż¼ROM▓╔ė├╠ž╩ŌĘĮ╩Įīæ╚ļą┼ŽóŻ¼ą┼Žóīæ╚ļ║¾ų╗─▄ūxŻ¼Č°RAM╝╚─▄ūxėų─▄īæĪŻ

ROM║═RAM┤µā”Ų„ąŠŲ¼╔ŽĄ─ę²ŠĆ═©│ŻĘų×ķ╦─ĮMŻ║ĄžųĘŠĆė├ė┌Ž“┤µā”Ų„▌ö╦═ĄžųĘ┤aŻ╗öĄ(sh©┤)ō■(j©┤)ŠĆ╩ŪļpŽ“Ą─Ż¼é„╦═ī”ąŠŲ¼ųą─│ę╗å╬į¬▀MąąūxŻ»īæ▓┘ū„Ą─öĄ(sh©┤)ō■(j©┤)Ż╗┐žųŲŠĆė├ė┌é„╦═┐žųŲą┼╠¢Ż¼┐žųŲ▓┘ū„╩Ū▀Mąąūx▀Ć╩Ū▀MąąīæĄ╚Ą╚Ż╗ļŖį┤ŠĆ╣®ĮoąŠŲ¼Ż½5Vų▒┴„ļŖį┤ĪŻŲõųąĄžųĘŠĆ╝░öĄ(sh©┤)ō■(j©┤)ŠĆĄ─ę²─_öĄ(sh©┤)┼cąŠŲ¼Ą─┤µā”╚▌┴┐ėąĻP(gu©Īn)ĪŻ

ĄžųĘŠĆįĮČÓŻ¼┤µā”╚▌┴┐Š═įĮ┤¾Ż╗öĄ(sh©┤)ō■(j©┤)ŠĆįĮČÓŻ¼├┐éĆå╬į¬ųą┤µā”Ą─Č■▀MųŲöĄ(sh©┤)Ą─╬╗öĄ(sh©┤)Š═įĮķLĪŻ└²╚ńŻ¼ĄžųĘŠĆ×ķnŚlĄ─┤µā”Ų„ąŠŲ¼Ą─┤µā”╚▌┴┐×ķ éĆå╬į¬Ż¼öĄ(sh©┤)ō■(j©┤)ŠĆĄ─ŚlöĄ(sh©┤)m×ķ├┐éĆå╬į¬─▄┤µā”Ą─Č■▀MųŲöĄ(sh©┤)Ą─╬╗öĄ(sh©┤)Ż¼ät┤µā”Ų„ąŠŲ¼Ą─┤µā”╚▌┴┐×ķ2nĪ┴mbitŻ¼╝┤Ż║

┤µā”╚▌┴┐=2ĄžųĘŠĆĄ─ŚlöĄ(sh©┤)Ī┴öĄ(sh©┤)ō■(j©┤)ŠĆĄ─ŚlöĄ(sh©┤)Ż©bitŻ®

╚ńę╗éĆ┤µā”Ų„ėą16ŚlĄžųĘŠĆ║═8ŚlöĄ(sh©┤)ō■(j©┤)ŠĆŻ¼╦³Ą─16╬╗ĄžųĘ┐╔Ą├ĄĮ216éĆĄžųĘŠÄ┤aŻ¼┐╔īżųĘ216éĆå╬į¬Ż¼╝┤┤µā”╚▌┴┐×ķ216éĆå╬į¬Ż¼├┐éĆå╬į¬8╬╗Ż¼ät┤µā”╚▌┴┐×ķ216Ī┴8bitĪŻ

2Ż«╬ó╠Ä└ĒŲ„Ż©MPUŻ®

╬ó╠Ä└ĒŲ„MPU╩Ū╬óą═ėŗ╦ŃÖCĄ─▀\╦Ń║═ųĖō]┐žųŲųąą─Ż¼Ųõąį─▄øQČ©┴╦╬óą═ėŗ╦ŃÖCĄ─ąį─▄ĪŻļm╚╗Ė„ĘN╬ó╠Ä└ĒŲ„ąį─▄║═ā╚(n©©i)▓┐ĮY(ji©”)śŗ(g©░u)ėą▓Ņ«ÉŻ¼ųĖ┴ŅŽĄĮy(t©»ng)ę▓▓╗═¼Ż¼Ą½╦³éāĄ─╗∙▒ŠĮM│╔ŽÓ═¼Ż¼Č╝░³║¼ėą┐žųŲŲ„Īó▀\╦ŃŲ„║═ā╚(n©©i)▓┐┐éŠĆĪŻ╬ó╠Ä└ĒŲ„┼c┤µā”Ų„ų«ķgĄ─ĮY(ji©”)śŗ(g©░u)┐╔ģóššłD1-2ĪŻ

Ż©1Ż®▀\╦ŃŲ„

▀\╦ŃŲ„į┌┐žųŲŲ„Ą─┐žųŲŽ┬ī”Č■▀MųŲöĄ(sh©┤)▀Mąą╦Ńąg(sh©┤)▀\╦Ń╗“▀ē▌ŗ▓┘ū„ĪŻ▀\╦ŃŲ„ė╔╦Ńąg(sh©┤)▀ē▌ŗå╬į¬ähĪó└█╝ėŲ„AĪó═©ė├╝─┤µŲ„PSĪóĢ║┤µŲ„TMP║═│╠ą“ĀŅæB(t©żi)ūųPSWĄ╚╬Õ▓┐ĘųĮM│╔ĪŻ

ó┘╦Ńąg(sh©┤)▀ē▌ŗå╬į¬ALUŻ║ ALU╩Ū▀\╦ŃŲ„Ą─║╦ą─Ż¼╦³ęį╚½╝ėŲ„×ķ╗∙ĄA(ch©│)Ż¼▓ó▌oęįęŲ╬╗║═┐žųŲ▀ē▌ŗĮM║ŽČ°│╔Ż¼į┌┐žųŲą┼╠¢Ą─┐žųŲŽ┬Ż¼┐╔▀Mąą╝ė£p│╦│²Ą╚╦Ńąg(sh©┤)▀\╦Ń║═Ė„ĘN▀ē▌ŗ▀\╦ŃĪŻ

ó┌└█╝ėŲ„AŻ║A╩Ūė╔ė|░l(f©Ī)Ų„ĮM│╔Ą─ęŲ╬╗╝─┤µŲ„Ż¼į┌▀\╦ŃŪ░┤µĘ┼ę╗éĆ▓┘ū„öĄ(sh©┤)Ż¼▀\╦Ń║¾┤µĘ┼▀\╦ŃĮY(ji©”)╣¹ĪŻ

ó█Ģ║┤µŲ„TMPŻ║TMPę▓╩Ūę╗éĆ╝─┤µŲ„Ż¼ė├ė┌Ģ║┤µ┴Ēę╗▓┘ū„öĄ(sh©┤)ĪŻ

ó▄│╠ą“ĀŅæB(t©żi)ūųPSWŻ║PSWė╔8╬╗ė|░l(f©Ī)Ų„ĮM│╔Ż¼┤µĘ┼ALU▓┘ū„▀^│╠ųąą╬│╔Ą─ĀŅæB(t©żi)ĪŻ└²╚ńŻ║└█╝ėŲ„AųąĄ─▀\╦ŃĮY(ji©”)╣¹╩Ūʱ×ķ┴ŃŻ¼ūŅĖ▀╬╗╩Ūʱėą▀M╬╗╗“ĮĶ╬╗Ż¼Ą═4╬╗Ž“Ė▀4╬╗╩Ūʱėą▀M╬╗╗“ĮĶ╬╗Ą╚Ą╚Ż¼Č╝į┌PSWųąŽÓæ¬(y©®ng)╬╗╔Ž▀Mąąś╦(bi©Īo)ųŠĪŻ

ó▌═©ė├╝─┤µŲ„PSŻ║PSė├ė┌┤µĘ┼▓┘ū„öĄ(sh©┤)╗“▀\╦ŃĮY(ji©”)╣¹ĪŻ

į┌▀\╦ŃŪ░Ż¼īó▀\╦Ń╦∙ąĶ▓┘ū„öĄ(sh©┤)╦═╚ļ└█╝ėŲ„║═Ģ║┤µŲ„Ż¼ė╔┐žųŲą┼╠¢┐žųŲALU▀Mąą▀\╦ŃŻ¼░č▀\╦ŃĮY(ji©”)╣¹┤µĘ┼ĄĮ└█╝ėŲ„AŻ¼▓óĖ∙ō■(j©┤)▀\╦ŃĮY(ji©”)╣¹įO(sh©©)ų├│╠ą“ĀŅæB(t©żi)ūųPSWĀŅæB(t©żi)╬╗Ą─ųĄĪŻ

Ż©2Ż®┐žųŲŲ„

┐žųŲŲ„╩Ū░l(f©Ī)▓╝▓┘ū„├³┴ŅĄ─ÖCśŗ(g©░u)Ż¼╩Ūėŗ╦ŃÖCĄ─ųĖō]ųąą─Ż¼ŽÓ«ö(d©Īng)ė┌╚╦─XĄ─╔±Įø(j©®ng)ųąśąŻ¼┐žųŲėŗ╦ŃÖCĄ─Ė„▓┐Ęųģf(xi©”)š{(di©żo)╣żū„Ż¼ė├ė┌ūįäėł╠(zh©¬)ąą│╠ą“ĪŻ┐žųŲŲ„ė╔ųĖ┴Ņ▓┐╝■ĪóĢrą“▓┐╝■║═╬ó▓┘ū„┐žųŲ▓┐╝■Ą╚╚²▓┐ĘųĮM│╔ĪŻ

ó┘ųĖ┴Ņ▓┐╝■Ż║ųĖ┴Ņ▓┐╝■╩Ūė├üĒūx╚ĪųĖ┴ŅĪóĘų╬÷ųĖ┴Ņ║═×ķ═Ļ│╔ųĖ┴Ņ«a(ch©Żn)╔·┐žųŲą┼╠¢Ą─▀ē▌ŗ▓┐╝■Ż¼ę▓╩Ū┐žųŲŲ„Ą─║╦ą─ĪŻ═©│ŻŻ¼ųĖ┴Ņ▓┐╝■ė╔│╠ą“ėŗöĄ(sh©┤)Ų„PCĪóųĖ┴Ņ╝─┤µŲ„IR║═ųĖ┴Ņūg┤aŲ„IDĄ╚╚²▓┐ĘųĮM│╔ĪŻ

ó┌Ģrą“▓┐╝■Ż║Ģrą“▓┐╝■ė╔ĢrńŖŽĄĮy(t©»ng)║═├}ø_Ęų┼õŲ„ĮM│╔Ż¼ė├ė┌«a(ch©Żn)╔·╬ó▓┘ū„┐žųŲ▓┐╝■╦∙ąĶĄ─Č©Ģr├}ø_ą┼╠¢ĪŻĢrńŖŽĄĮy(t©»ng)«a(ch©Żn)╔·ÖCŲ„Ą─ĢrńŖ├}ø_ą“┴ąŻ¼├}ø_Ęų┼õŲ„ėųĘQ╣Ø(ji©”)┼─░l(f©Ī)╔·Ų„Ż¼ė├ė┌«a(ch©Żn)╔·╣Ø(ji©”)┼─ļŖ╬╗║═╣Ø(ji©”)┼─├}ø_ĪŻ

ó█╬ó▓┘ū„┐žųŲ▓┐╝■ ╬ó▓┘ū„┐žųŲ▓┐╝■×ķųĖ┴Ņūg┤aŲ„mĄ─▌ö│÷ą┼╠¢┼õ╔Ž╣Ø(ji©”)┼─ļŖ╬╗║═╣Ø(ji©”)┼─├}ø_Ż¼ę▓┐╔║══Ō▓┐▀MüĒĄ─┐žųŲą┼╠¢ĮM║ŽŻ¼╣▓═¼ą╬│╔ŽÓæ¬(y©®ng)Ą─╬ó▓┘ū„┐žųŲą“┴ąŻ¼ęį═Ļ│╔ęÄ(gu©®)Č©Ą─▓┘ū„ĪŻ

ėŗ╦ŃÖCĄ─╣żū„Š═╩Ūł╠(zh©¬)ąą│╠ą“ĪŻę¬ł╠(zh©¬)ąąę╗éĆ│╠ą“▒žĒÜīóįō│╠ą“Ę┼╚ļā╚(n©©i)┤µŻ¼Č°│╠ą“╩Ū╚¶Ė╔ųĖ┴ŅĄ─ėąą“┼┼┴ąŻ¼ę¬ł╠(zh©¬)ąą│╠ą“ų╗ę¬Å─Ą┌ę╗ŚlųĖ┴Ņķ_╩╝Ż¼ųŚlūx╚ĪųĖ┴ŅĪóĘų╬÷ųĖ┴ŅĪół╠(zh©¬)ąąųĖ┴Ņų▒ų┴ł╠(zh©¬)ąąĄĮ═ŻÖCųĖ┴Ņ╝┤═Ļ│╔│╠ą“ĪŻę¬Å─ā╚(n©©i)┤µųąūx╚ĪųĖ┴ŅŻ¼▒žĒÜĮo│÷ā╚(n©©i)┤µå╬į¬Ą─ĄžųĘŻ¼▀@Š═ąĶę¬ėąę╗éĆīŻķTĄ─╝─┤µŲ„ė├üĒ┤µĘ┼īóꬳ╠(zh©¬)ąąųĖ┴ŅĄ─ā╚(n©©i)┤µĄžųĘŻ¼▀@éĆ╝─┤µŲ„Š═╩Ū│╠ą“ėŗöĄ(sh©┤)Ų„PCĪŻ«ö(d©Īng)ėŗ╦ŃÖCĖ∙ō■(j©┤)PCųąĄžųĘ╚Ī│÷ꬳ╠(zh©¬)ąąųĖ┴ŅĄ─ę╗éĆūų╣Ø(ji©”)║¾Ż¼PCŠ═ūįäė╝ė1Ż¼ųĖŽ“ųĖ┴ŅĄ─Ž┬ę╗ūų╣Ø(ji©”)Ż¼×ķÖCŲ„Ž┬┤╬ūx╚ĪųĖ┴Ņū÷║├£╩(zh©│n)éõĪŻ

ųĖ┴Ņ╝─┤µŲ„IRė├üĒ┤µĘ┼Å─┤µā”Ų„ųą╚Ī│÷Ą─«ö(d©Īng)Ū░ꬳ╠(zh©¬)ąąųĖ┴ŅĄ─ųĖ┴Ņ┤aĪŻįōųĖ┴Ņ┤aį┌IRųąĄ├ĄĮ╝─┤µ║═ŠÅø_║¾▒╗╦═ĄĮųĖ┴Ņūg┤aŲ„IDųąūg┤aŻ¼Įø(j©®ng)ūg┤a║¾Š═ų¬Ą└įōųĖ┴Ņ╦∙ę¬▀MąąĄ─▓┘ū„Ż¼▓óį┌Ģrą“▓┐╝■║═╬ó▓┘ū„┐žųŲ▓┐╝■Ą─ū„ė├Ž┬┐žųŲŽÓæ¬(y©®ng)▓┐╝■▀Mąą▓┘ū„Ż¼ł╠(zh©¬)ąąųĖ┴ŅĪŻ

3Ż«I/OĮė┐┌║══ŌįO(sh©©)

I/OĮė┐┌╩Ū╝▄įO(sh©©)į┌╬ó╠Ä└ĒŲ„║══ŌįO(sh©©)ķgĄ─ś“┴║Ż¼╩Ūę╗ĘN▀^Č╔Ą─┤¾ęÄ(gu©®)─Ż╝»│╔ļŖ┬ĘąŠŲ¼ĪŻė╔ė┌┤¾ČÓöĄ(sh©┤)═ŌįO(sh©©)Č╝╩ŪÖCļŖą═Ą─Ż¼╣żū„╦┘Č╚▌^┬²Ż¼ę“┤╦╬ó╠Ä└ĒŲ„MPU═©│Ż▓╗─▄║═╦³éāų▒ĮėŽÓ▀BŻ¼Č°╩Ū═©▀^I/OĮė┐┌║══ŌįO(sh©©)ŽÓ▀BŻ¼ęį▒ŃīŹ¼F(xi©żn)╦┘Č╚ĪóļŖŲĮ║═ą┼╠¢ąį┘|(zh©¼)Ą─Ųź┼õĪŻ

4Ż«ĄžųĘ┐éŠĆĪóöĄ(sh©┤)ō■(j©┤)┐éŠĆ║═┐žųŲ┐éŠĆ

┐éŠĆ╩Ūį┌╬óą═ėŗ╦ŃÖCĖ„▓┐Ęųų«ķgé„╦═ą┼ŽóĄ─╣½╣▓═©Ą└Ż¼ę▓╩Ū£Ž═©╬óą═ėŗ╦ŃÖCĖ„ĘNŲ„╝■Ą─ś“┴║ĪŻ

Ż©1Ż®ĄžųĘ┐éŠĆAB

ĄžųĘ┐éŠĆABė├üĒé„╦═MPU░l(f©Ī)│÷Ą─ĄžųĘ┤aŻ¼╩Ūå╬Ž“┐éŠĆĪŻ«ö(d©Īng)╬ó╠Ä└ĒŲ„MPUī”┤µā”Ų„╗“═Ō▓┐įO(sh©©)éõ▀Mąąūxīæ▓┘ū„ĢrŻ¼╩ūŽ╚ę¬░č┤µā”å╬į¬╗“═ŌįO(sh©©)Ą─ĄžųĘ┤a╦═ĄĮĄžųĘ┐éŠĆ╔Ž▀xųą╦³Ż¼╚╗║¾▀MąąūxīæĪŻĄžųĘ┐éŠĆŚlöĄ(sh©┤)ė╔MPUą═╠¢øQČ©Ż¼į┌┤¾▓┐Ęų8╬╗ÖCųąŻ¼ĄžųĘ┐éŠĆ═©│Ż×ķ16ŚlĪŻ

Ż©2Ż®öĄ(sh©┤)ō■(j©┤)┐éŠĆDB

öĄ(sh©┤)ō■(j©┤)┐éŠĆDBė├üĒé„╦═öĄ(sh©┤)ō■(j©┤)║═ųĖ┴Ņ┤aŻ¼╩ŪļpŽ“┐éŠĆĪŻ═©▀^DBŻ¼MPU┐╔īóöĄ(sh©┤)ō■(j©┤)īæ╚ļ┤µā”Ų„╗“Ž“═ŌįO(sh©©)▌ö│÷öĄ(sh©┤)ō■(j©┤)Ż¼ę▓┐╔Å─┤µā”Ų„╗“▌ö╚ļįO(sh©©)éõ▌ö╚ļöĄ(sh©┤)ō■(j©┤)ĪŻöĄ(sh©┤)ō■(j©┤)┐éŠĆŚlöĄ(sh©┤)│Ż║═╦∙ė├╬ó╠Ä└ĒŲ„ūųķLŽÓĄ╚Ż¼Ą½ę▓ėąā╚(n©©i)▓┐×ķ16╬╗▀\╦ŃČ°═Ō▓┐╚į×ķ8╬╗öĄ(sh©┤)ō■(j©┤)┐éŠĆĄ─ŪķørĪŻ8╬╗ÖCųąöĄ(sh©┤)ō■(j©┤)┐éŠĆ═©│Żėą8ŚlĪŻ

Ż©3Ż®┐žųŲ┐éŠĆCB

┐žųŲ┐éŠĆCBė├üĒé„╦═MPU░l(f©Ī)│÷Ą─┐žųŲą┼╠¢Īó┤µā”Ų„╗“═ŌįO(sh©©)Ą─ĀŅæB(t©żi)ą┼╠¢║═Ģrą“ą┼╠¢Ą╚ĪŻ├┐Ė∙┐žųŲ┐éŠĆĄ─ą┼Žóé„╦═ĘĮŽ“╩Ū╣╠Č©Ą─Īóå╬Ž“Ą─Ż¼Č°┐žųŲ┐éŠĆū„×ķš¹¾w×ķļpŽ“Ą─Ż¼╚ńłD╦∙╩ŠĪŻ┐žųŲ┐éŠĆĄ─ŚlöĄ(sh©┤)ę“ÖCŲ„Č°«ÉŻ¼├┐Śl┐žųŲŠĆūŅČÓé„╦═ā╔éĆ┐žųŲą┼╠¢ĪŻ

╬óą═ėŗ╦ŃÖC▓╔ė├┐éŠĆĮY(ji©”)śŗ(g©░u)Ż¼╩╣Ą├╦³─▄ē“╩«ĘųĘĮ▒ŃĄžīŹ¼F(xi©żn)┤µā”Ų„Ą─öU│õ╝░I/OĮė┐┌░ÕĄ─į÷╝ė║═£p╔┘ĪŻ

ŠÄ▌ŗŻ║admin ūŅ║¾ą▐Ė─ĢrķgŻ║2018-05-08