NAND Flash оƬ�yԇ

DFT : Design For Testability

TTR :Test Time Reduction

KGD: Known Good Die

NAND Flash оƬ�yԇ��Ҫ�Ǟ��˺Y�x��Screen Out����Flash��С��g�a�����Ĵ�����ʧЧ��

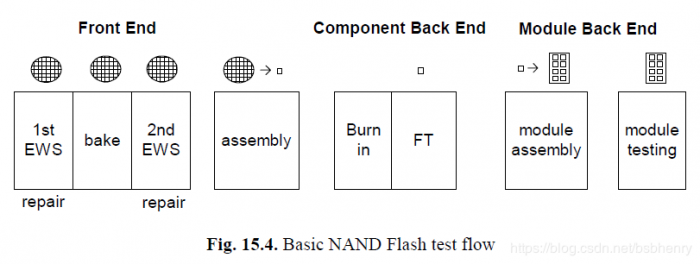

�yԇ���̣�Test Flow��

��wafer level����single component level��module level�����x��헜yԇ�Ĵ��Y�x�������^���ʧЧ��device����Ҫ�M�����_����õĜyԇ���w�ʣ���������؛�ĮaƷ����ʧЧ�ĮaƷ��ͬ�r��Ҫ�p�ٜyԇ�ĕr�g�c�ɱ���

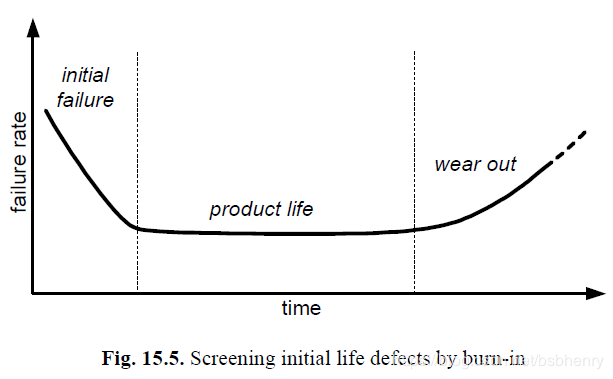

Burn-in�yԇ

�ձ���f���Ǟ����˽�aƷ�ĝ���ʧЧ��������һ���l���£��ߜ�/��늉�/һ����ȣ��¼���оƬ�ϻ��������ڹ�����ǰ���F(xi��n)���@�N�yԇ�����ڷ��b���P���棬�������W�͙Cе�����ء�

����ԡ���������aƷ������ʧЧ���^�ߣ����g�A�α��^��(w��n)���������Ñ��õ��ĮaƷʧЧ���^�ͣ���Ҫͨ�^burn-in�yԇ������ȱ�ݵĮaƷ����؛�ĮaƷ�ڳ��Sǰ�Ͷ��^��ز�ڡ����˜p�ٕr�g����Ҫ�M�м��٣����ڸ����ӵėl����ԇ�ߜ�/��늉�/һ����ȣ������Ҹ�����Փ����Ӌ�����ͬ�l���µļ������ӣ��������H�r�gӋ�����Ч�ĕr�g��

���Ɯyԇ�ɱ���һ����Ҫ��������ߜyԇ�IJ��жȡ�

�yԇ�C�_�ڜyԇһ���aƷ�r����횵ȴ����ЮaƷ����ɺ����_ʼ��һ�A�εĜyԇ��

�p�ٜyԇ�r�g����Ҫ��(y��u)�����ɷ��棺

1. ���x���r�g

2. ��������ͽY���@ȡ

���x���ĕr�g��оƬ���ԛQ��������Ŭ���ķ����������ͬ�r������chip��block�M�в�����

���оƬ�����Լ����ɜyԇ�������Ϳ��Թ�(ji��)�s����ݔ��ĕr�g���@�c����ͨ�^DFT���F(xi��n)���������ֱ�ӵõ��yԇ�ɹ�ʧ������Ϣ������Ҫ��ԭʼ�Ĕ�����ݔ���yԇ�C�ϣ�Ҳ���Թ�(ji��)�s�����r�g��

���ϣ�Winbond���A�ϵ�ЮaƷ���c���Y���������Ɇ���ǢՄ��������������ԃ�A��flashоƬ����-�����f�����Ƽ����f��������Winbond�����������߱Mȫ���������ա�0755-82591179.QQ:83652985

����simon ����ĕr�g��2019-07-03