PCB�O(sh��)Ӌ����ͨ��Ӌ����O(sh��)ӋҎ(gu��)��

PCB�O(sh��)Ӌ�в���ͨ�����Ӌ�㣿�c�O(sh��)ӋҎ(gu��)�t����ʲô�ӵ�(li��n)ϵ��

����ͨ��Ӌ��Ҏ(gu��)�t��

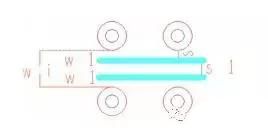

PCB�岼��ͨ���������㷽ʽ��

�ɂ��^��֮�g����ͨ����Ni=INT((Wi-2S-W1)/(W1+S1)+1)

����

Ni���������^���g����ͨ����(sh��)

Wi���^��߅���g��

S���^������߅���g��

W1������

S1�����g��

�ɂ��^��֮�g����ͨ��Ӌ��ʾ��D

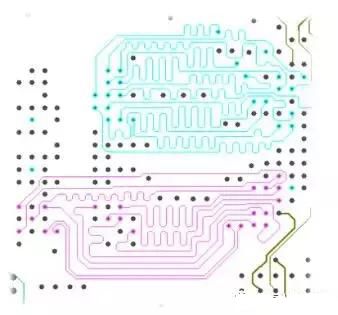

��־��r��

W1��=2*W2+S2 ͨ����(sh��)�����־�ͨ����(sh��)

W2����־�����

S2����־�����(n��i)���g��

��־�Ӌ��ͨ���r����һ����־���W2/S2����Ч��һ���ξ���������2*W2+S2��̎����

�f����50MIL���cϵ�y(t��ng)����ͨ��̖��5MIL������8MIL���g�ࣩ����2������ͨ���O(sh��)Ӌ���r���̖����1������ͨ���O(sh��)Ӌ�������̖����1����־�ͨ���O(sh��)Ӌ��

���܅^(q��)��Ҏ(gu��)��֪�R��

��1�����h����BGA������������Fanout������ʽ�����4�Ź��_����ͨ�^���Fanout������ͨ����

��2�� �����Դ���ع��_��Ҫֱ��Fanout��������ƽ��ӣ������������100mil�L��Fanout���������������ӵIJ���ͨ��Ҏ(gu��)����

��3������BGA�^(q��)���Ӕ�(sh��)�_��Ҏ(gu��)�t���£�

���ك�(n��i)�Ӳ����Ӕ�(sh��)=INT(M/N)+1

�����(n��i)�Ӳ����Ӕ�(sh��)=BGA���Դ�����ܹ��_�Ų��Ӕ�(sh��)/���^���g����ͨ����(sh��)-2

�f����M:�����4�ӹ��_��BGA�^(q��)��ķ��Դ�ز����B�ӿ���(sh��)+ǰ����ֱ��Fanout���M�IJ���ͨ����(sh��)��N:��5�Ź��_Fanout�h(hu��n)�^(q��)��IJ���ͨ������(sh��)

BGA�^(q��)�����г���4�ӵĹ��_��������Ҫռ�õ�5�ӭh(hu��n)�΅^(q��)��IJ���ͨ��������(j��)�˅^(q��)��IJ���ͨ����(sh��)�Ϳ��IJ����B�Ӕ�(sh��)�_�����ك�(n��i)�Ӳ����Ӕ�(sh��)��

��4������(j��)����ƿ�i�^(q��)�_��PCB�岼���Ӕ�(sh��)��ƿ�i�^(q��)��PCB�����ٲ����Ӕ�(sh��)=INT(M/N)+1

�f����M:ͨ�^ƿ�i�^(q��)��IJ����B�Ӕ�(sh��)��N:ƿ�i�^(q��)��IJ���ͨ����(sh��)

����BGA�^(q��)��Ҏ(gu��)����Ҫ��(y��u)���M�п����Ą��֣����x�ĸ��NBUS��Ȼ�����(j��)���N�����ķֲ��_�������Ĵ�� ^(q��)��������(j��)���M����������ͨ����(sh��)�M��Ԕ����ͨ���߷���Ͳ���Ҏ(gu��)����

��Ҫ��̖����Ҏ(gu��)��֪�R��

��1�����h200MHz���ϻ�r������С��0.2ns��ͬ�����п���Ҫ���ؓ�Y(ji��)��(g��u)���և���һ�£�ͬ�Ӳ��в�����ͬ���Q��

�f������DDR���ٲ��п����Y(ji��)��(g��u)�����_�������̖�|(zh��)����ͬ�MDQ/DQS��̖��ͬ�Ӳ�������ַ�Ϳ��ƿ���ͬ�Ӳ�����ͬ���Q�ӣ��քe���Ʊ�Ӻ̓�(n��i)�Ӳ������L

��2����ֹ��ͬ��Ϳ�����ϲ���

�f�������ֹDDR�cLocal bus��ϲ�����DDR��(sh��)��(j��)�c��ַ��ϲ����ȣ���������g������r�£����Բ��ò��ֻ�ϲ�������Ҫ���ַ���c��(sh��)��(j��)��Ҫ���C����3H�ľ��x��

��3��������̖��(y��u)�Ȳ���

��4�����h������̖�����Ӳ���

��5��3.125Gbps���ϸ�����̖��������x���^��Stub��С�IJ����ӣ����p���^�ה�(sh��)����

��6�����h3.125Gbps���¸�����̖������3.125Gbps����(y��u)���^��STUB��С�IJ�����

��7��3.125Gbps���ϸ�����̖����Ҏ(gu��)���r��(y��u)�ȿ��]�����L�ȣ�������̡�

��8��������̖������ҪҎ(gu��)�t��������������ƽ��ӵIJ�����

��9��ģ�M��̖��ֹ�ڔ�(sh��)����̖�^(q��)��

��10����ͬ�ƽ��̖��ֹ��ϲ���

�f������LVTTL�cCML�ƽ��̖

���ϱ���PCB�O(sh��)Ӌ�в���ͨ��Ӌ����O(sh��)ӋҎ(gu��)����

����admin ����ĕr�g��2018-01-08