─·║├Ż¼ÜgėŁ▀M(j©¼n)╚ļ╔Ņ█┌╩ąĘf╠žą┬┐Ų╝╝ėąŽ▐╣½╦Š╣┘ĘĮŠW(w©Żng)šŠŻĪ

─·║├Ż¼ÜgėŁ▀M(j©¼n)╚ļ╔Ņ█┌╩ąĘf╠žą┬┐Ų╝╝ėąŽ▐╣½╦Š╣┘ĘĮŠW(w©Żng)šŠŻĪ

ĻP(gu©Īn)ė┌▓Č½@

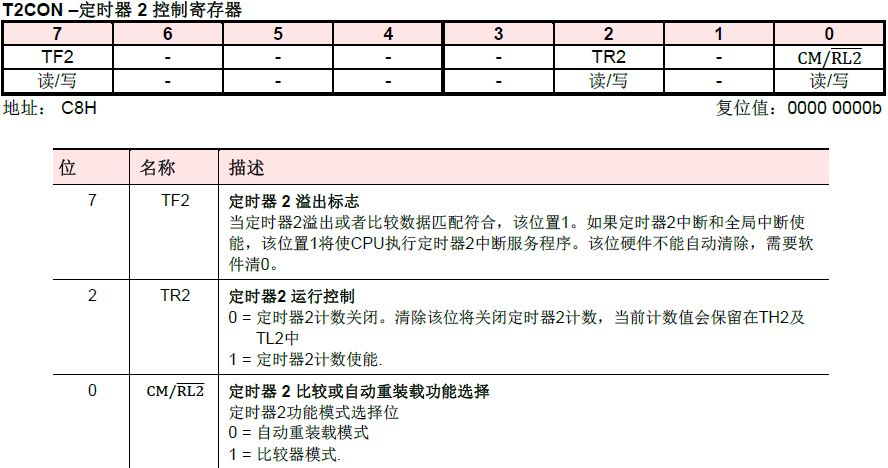

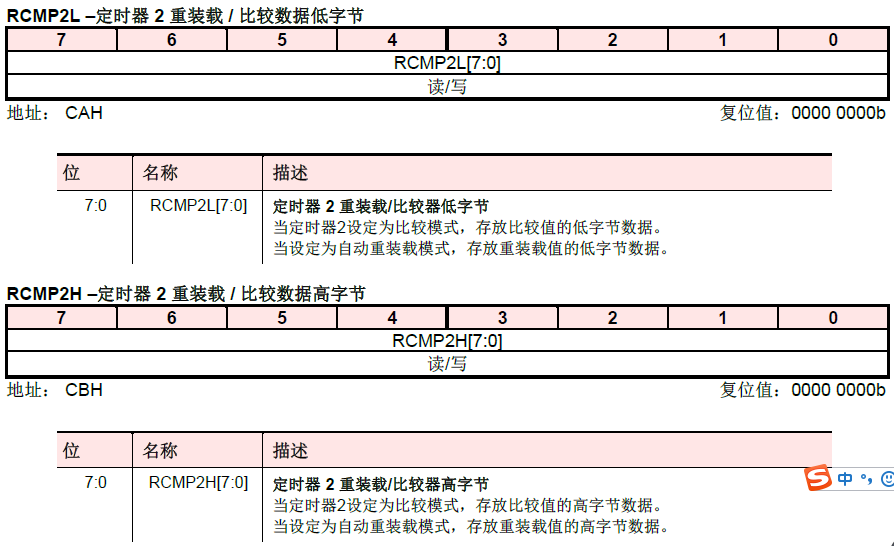

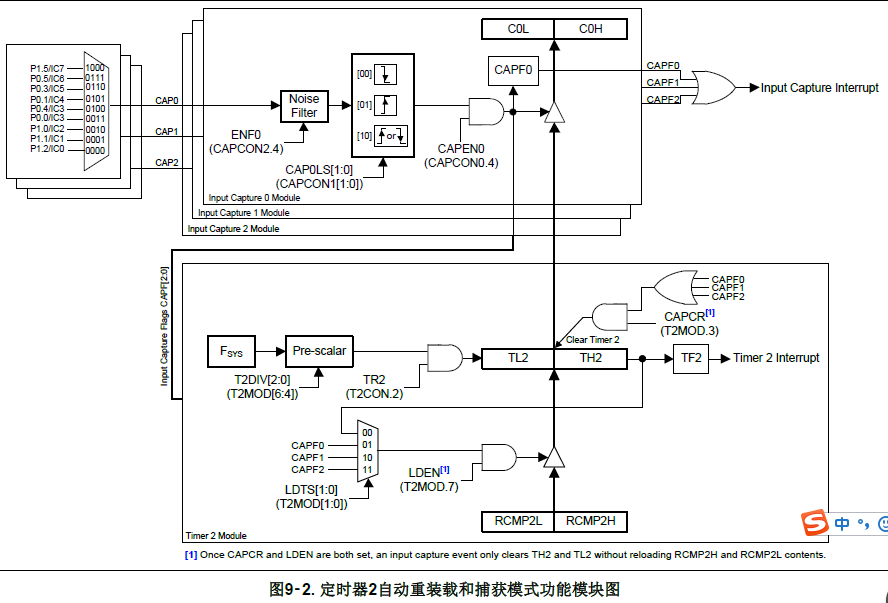

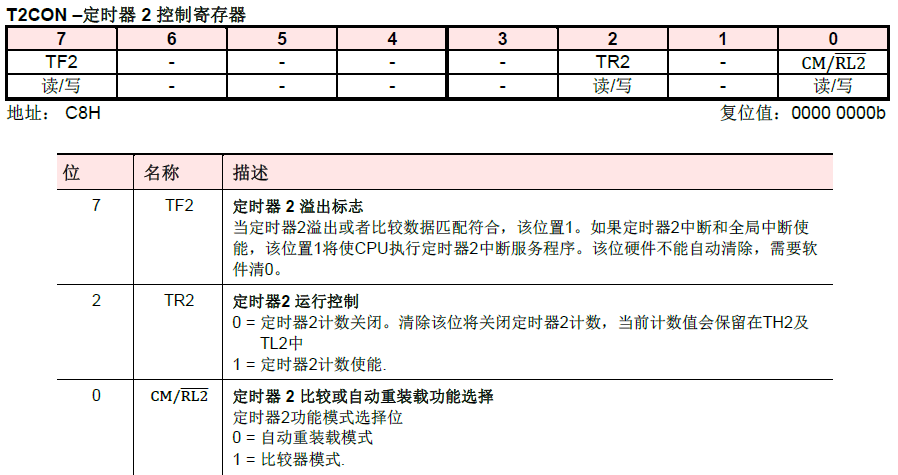

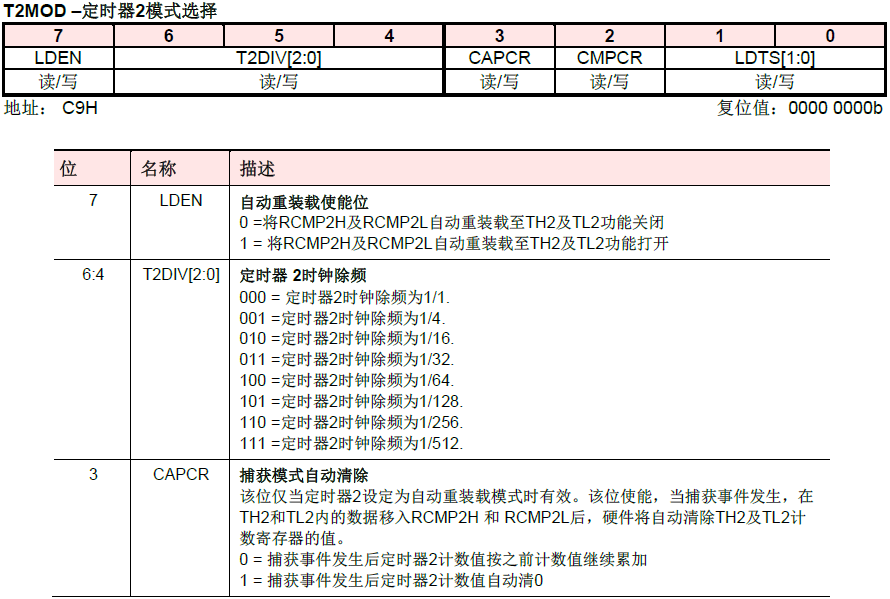

Č©ĢrŲ„2╩Ūę╗éĆ16╬╗Ą─Ž“╔Žėŗ(j©¼)öĄ(sh©┤)Ų„Ż¼ė╔Ė▀8╬╗╝─┤µŲ„(TH2)║═Ą═8╬╗╝─┤µŲ„(TL2)ĮM│╔ĪŻ═©▀^┼õų├╝─┤µŲ„RCMP2H║═RCMP2LŻ¼įO(sh©©)ų├  (T2CON.0)║¾Ż¼Č©ĢrŲ„2─▄╣żū„į┌▒╚▌^─Ż╩Į║═ūįäėųž▌d─Ż╩ĮŽ┬ĪŻ

(T2CON.0)║¾Ż¼Č©ĢrŲ„2─▄╣żū„į┌▒╚▌^─Ż╩Į║═ūįäėųž▌d─Ż╩ĮŽ┬ĪŻ

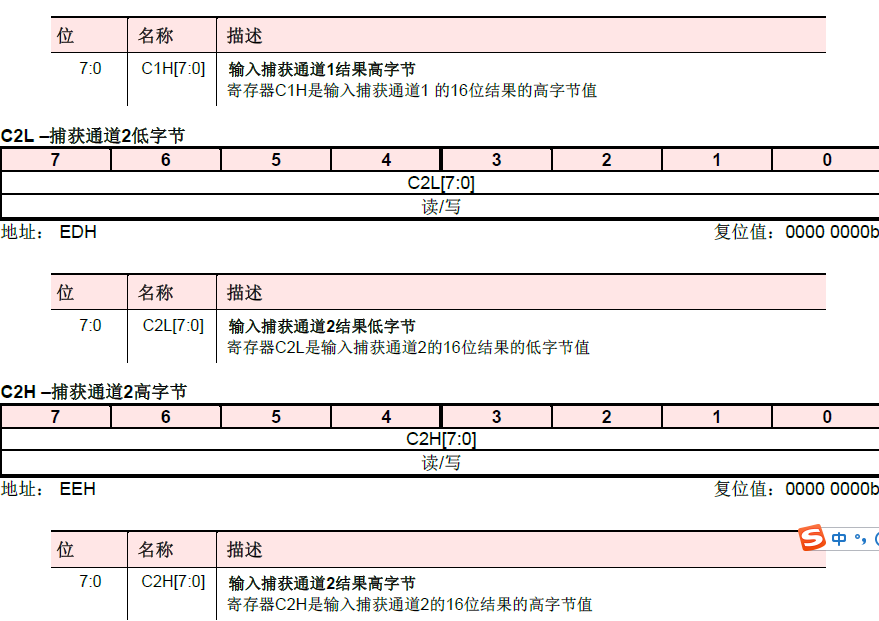

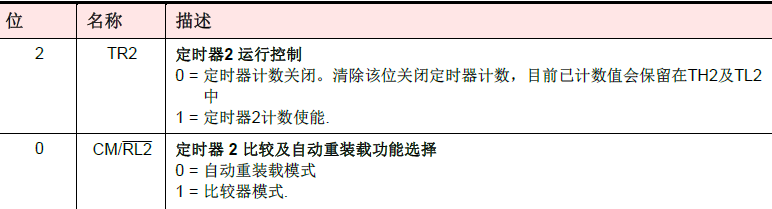

Č©ĢrŲ„2Š▀ėą3═©Ą└▌ö╚ļ▓Č½@─ŻēKŻ¼┐╔ė├ė┌£y┴┐▌ö╚ļ├}ø_īÆČ╚╗“ų▄Ų┌ĪŻ3═©Ą└▓Č½@ĮY(ji©”)╣¹Ęųäe┤µĘ┼į┌╝─┤µŲ„C0H ╝░ C0L, C1H ╝░ C1L, C2H╝░ C2LųąĪŻČ©ĢrŲ„2Ą─ĢrńŖüĒūįŽĄĮy(t©»ng)ĢrńŖĄ─ĘųŅlŻ¼┐é╣▓Š▀ėą8╝ēĘųŅlŻ¼┐╔▀mė├ė┌Ė³ČÓæ¬(y©®ng)ė├ąĶŪ¾ĪŻ«ö(d©Īng)TR2(T2CON.2) ų├ 1Ż¼Č©ĢrŲ„╩╣─▄Ż╗TR2ų├0ĢrŻ¼Č©ĢrŲ„ĻP(gu©Īn)ķ]ĪŻŽ┬┴ą╝─┤µŲ„ė├ė┌┐žųŲČ©ĢrŲ„2╣”─▄ĪŻ

ūįäėųžčb▌d╣”─▄─Ż╩Į

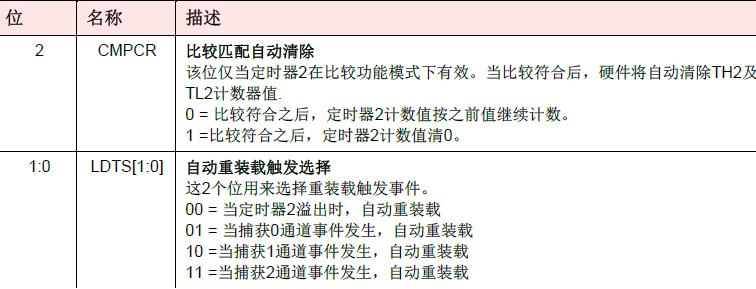

«ö(d©Īng)  ŪÕ0Ż¼Č©ĢrŲ„2┼õų├×ķūįäėųžčb▌d─Ż╩ĮĪŻį┌įō─Ż╩ĮŽ┬Ż¼RCMP2H ╝░ RCMP2L▒Ż┤µųžčb▌dĄ─öĄ(sh©┤)ųĄĪŻ«ö(d©Īng)LDENų├╬╗║¾Ż¼ę╗Ą®ėąė|░l(f©Ī)╩┬╝■░l(f©Ī)╔·Ż¼ė▓╝■īóūįäė░č RCMP2H ╝░ RCMP2L ╝─┤µŲ„ā╚(n©©i)Ą─ųĄīæ╚ļTH2 ╝░ TL2 ųąĪŻė|░l(f©Ī)╩┬╝■┐╔ęį╩ŪČ©ĢrŲ„2ęń│÷╗“╩Ūę╗éĆ╦∙┼õų├Ą─▓Č½@ą┼Ą└ėąė|░l(f©Ī)╩┬╝■░l(f©Ī)╔·Ż©Ė∙ō■(j©┤)LDTS[1:0] (T2MOD[1:0])┼õų├Ż®ĪŻūóęŌŻ¼ę╗Ą®CAPCR (T2MOD.3) ų├1Ż¼╚ńėąę╗éĆ▓Č½@╩┬╝■░l(f©Ī)╔·Ż¼āHŪÕ│²TH2╝░ TL2 ā╚(n©©i)Ą─ųĄŻ¼▓╗Ģ■īó RCMP2H ╝░ RCMP2LĄ─ųĄ▌d╚ļĪŻ

ŪÕ0Ż¼Č©ĢrŲ„2┼õų├×ķūįäėųžčb▌d─Ż╩ĮĪŻį┌įō─Ż╩ĮŽ┬Ż¼RCMP2H ╝░ RCMP2L▒Ż┤µųžčb▌dĄ─öĄ(sh©┤)ųĄĪŻ«ö(d©Īng)LDENų├╬╗║¾Ż¼ę╗Ą®ėąė|░l(f©Ī)╩┬╝■░l(f©Ī)╔·Ż¼ė▓╝■īóūįäė░č RCMP2H ╝░ RCMP2L ╝─┤µŲ„ā╚(n©©i)Ą─ųĄīæ╚ļTH2 ╝░ TL2 ųąĪŻė|░l(f©Ī)╩┬╝■┐╔ęį╩ŪČ©ĢrŲ„2ęń│÷╗“╩Ūę╗éĆ╦∙┼õų├Ą─▓Č½@ą┼Ą└ėąė|░l(f©Ī)╩┬╝■░l(f©Ī)╔·Ż©Ė∙ō■(j©┤)LDTS[1:0] (T2MOD[1:0])┼õų├Ż®ĪŻūóęŌŻ¼ę╗Ą®CAPCR (T2MOD.3) ų├1Ż¼╚ńėąę╗éĆ▓Č½@╩┬╝■░l(f©Ī)╔·Ż¼āHŪÕ│²TH2╝░ TL2 ā╚(n©©i)Ą─ųĄŻ¼▓╗Ģ■īó RCMP2H ╝░ RCMP2LĄ─ųĄ▌d╚ļĪŻ

▒╚▌^╣”─▄─Ż╩Į

«ö(d©Īng)  ų├1Ż¼Č©ĢrŲ„2┼õų├×ķ▒╚▌^Ų„─Ż╩ĮĪŻį┌įō─Ż╩ĮŽ┬Ż¼RCMP2H ╝░ RCMP2L ŅA(y©┤)┤µ┤²▒╚▌^öĄ(sh©┤)ō■(j©┤)ĪŻė╔ė┌Č©ĢrŲ„2Ž“╔Žėŗ(j©¼)öĄ(sh©┤)Ż¼ę╗Ą®TH2 ║═ TL2 Ųź┼õRCMP2H ║═ RCMP2LĄ─įO(sh©©)Č©ųĄŻ¼TF2 (T2CON.7) īóĢ■ė╔ė▓╝■ų├1Ż¼ė├ęįś╦(bi©Īo)╩Š░l(f©Ī)╔·┴╦▒╚▌^Ųź┼õ╩┬╝■ĪŻ

ų├1Ż¼Č©ĢrŲ„2┼õų├×ķ▒╚▌^Ų„─Ż╩ĮĪŻį┌įō─Ż╩ĮŽ┬Ż¼RCMP2H ╝░ RCMP2L ŅA(y©┤)┤µ┤²▒╚▌^öĄ(sh©┤)ō■(j©┤)ĪŻė╔ė┌Č©ĢrŲ„2Ž“╔Žėŗ(j©¼)öĄ(sh©┤)Ż¼ę╗Ą®TH2 ║═ TL2 Ųź┼õRCMP2H ║═ RCMP2LĄ─įO(sh©©)Č©ųĄŻ¼TF2 (T2CON.7) īóĢ■ė╔ė▓╝■ų├1Ż¼ė├ęįś╦(bi©Īo)╩Š░l(f©Ī)╔·┴╦▒╚▌^Ųź┼õ╩┬╝■ĪŻ

╚ń╣¹ CMPCR (T2MOD.2) ų├1Ż¼«ö(d©Īng)░l(f©Ī)╔·▒╚▌^Ųź┼õ╩┬╝■║¾Ż¼Č©ĢrŲ„2 ėŗ(j©¼)öĄ(sh©┤)Ų„īóė▓╝■ūįäėŪÕ0ĪŻ

▌ö╚ļ▓Č½@╣”─▄─ŻēK

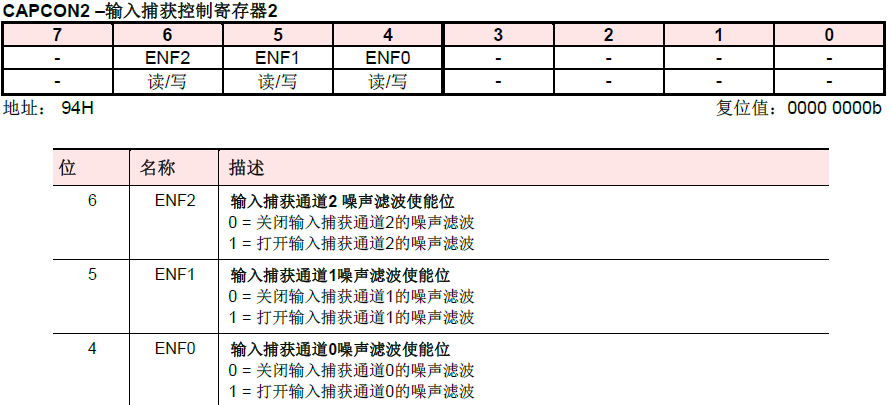

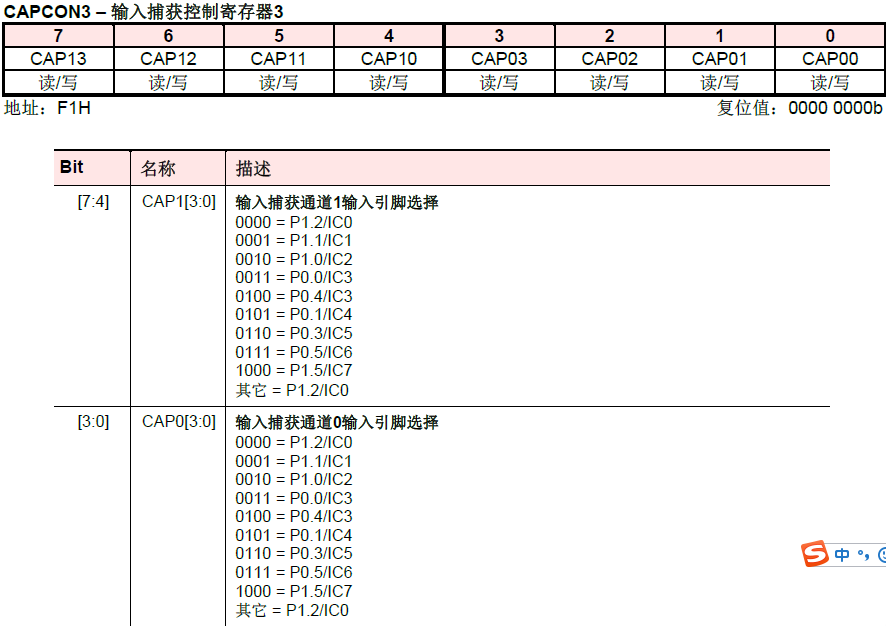

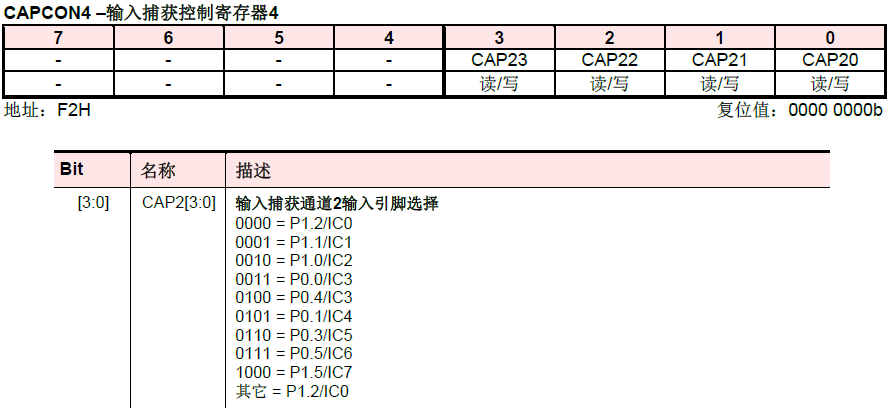

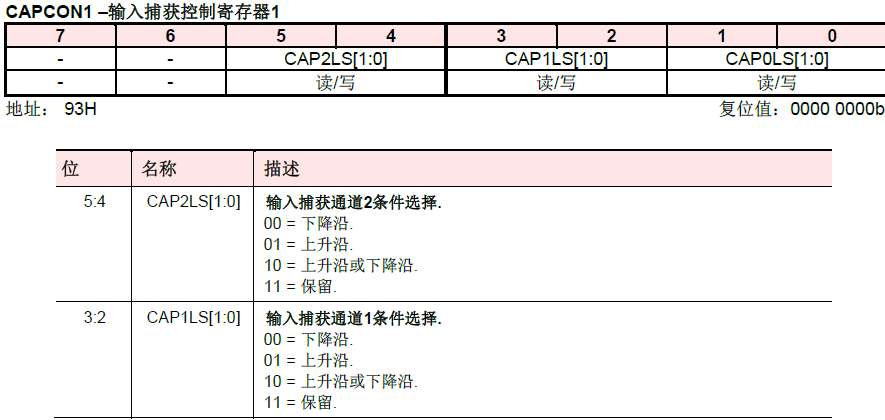

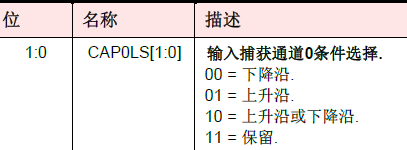

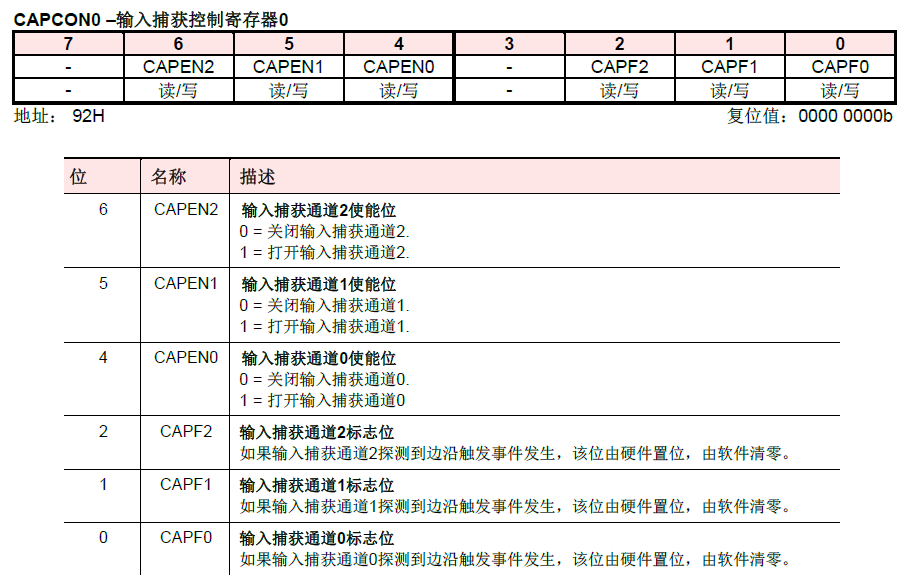

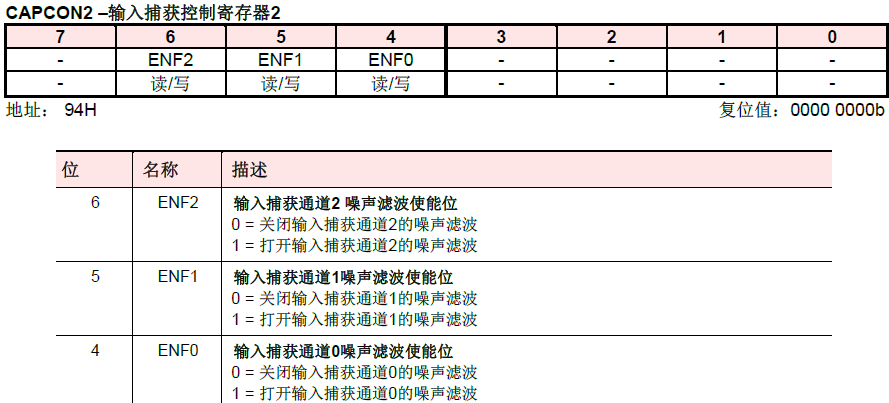

▌ö╚ļ▓Č½@─ŻēKę└┐┐Č©ĢrŲ„2īŹ(sh©¬)¼F(xi©żn)▌ö╚ļ▓Č½@╣”─▄ĪŻ▌ö╚ļ▓Č½@─ŻēK═©▀^╝─┤µŲ„CAPCON0~2┼õų├üĒų¦│ų3ĮMą┼Ą└▌ö╚ļ(CAP0Ż¼CAP1║═CAP2)Ż¼┐╔▀xō±┼õų├9éĆę²─_Ż©P1.5Ż¼P1[2Ż║0]Ż¼P0.0Ż¼P0.1║═P0[5Ż║3]Ż®ĪŻę²─_Å═(f©┤)║Ž╣”─▄▀xō±═©▀^CAPCON3║═CAPCON4┼õų├ĪŻ├┐éĆ▌ö╚ļ═©Ą└Ą─įļ┬Ģ×V▓©Ų„┐╔═©▀^įO(sh©©)ų├ENF0~2 (CAPCON2[6:4])╩╣─▄Ż¼┐╔×V│²ąĪė┌4éĆŽĄĮy(t©»ng)ĢrńŖĄ─▌ö╚ļ├½┤╠ĪŻ├┐ĮM▌ö╚ļ▓Č½@═©Ą└╣▓ŽĒČ©ĢrŲ„2ėŗ(j©¼)öĄ(sh©┤)Ż¼Ą½ėąūį╝║¬Ü(d©▓)┴óĄ─▀ģčžÖz£yĪŻ├┐éĆė|░l(f©Ī)▀ģčžÖz£y┐╔ė╔╝─┤µŲ„CAPCON1Ą─ŽÓĻP(gu©Īn)╬╗¬Ü(d©▓)┴ó┼õų├Ż¼ų¦│ųš²▀ģčž▓Č½@Ż¼žō(f©┤)▀ģčž▓Č½@Ż¼╗“ļp▀ģčž▓Č½@ĪŻį┌╩╣ė├Ū░Ż¼▒žĒÜįO(sh©©)ų├═©Ą└╩╣─▄╬╗CAPEN0~2 (CAPCON0[6:4])ĪŻ

«ö(d©Īng)▌ö╚ļ▓Č½@═©Ą└╩╣─▄Ūę╦∙▀xō±Ą─▀ģčžė|░l(f©Ī)░l(f©Ī)╔·ĢrŻ¼Č©ĢrŲ„2Ą─ėŗ(j©¼)öĄ(sh©┤)ųĄTH2║═TL2īó▒╗▓Č½@Īóé„▌ö▓ó┤µā”ĄĮ▓Č½@╝─┤µŲ„CnH ║═ CnLĪŻ▀ģčžė|░l(f©Ī)ę▓┐╔ė▓╝■ų├╬╗CAPFn (CAPCON0.n)Ż¼╚ń╣¹ECAP (EIE.2)║═EAČ╝┤“ķ_Ż¼īó«a(ch©Żn)╔·ųąöÓĪŻ╚²ĮM▌ö╚ļ▓Č½@╣▓ŽĒę╗éĆųąöÓŽ“┴┐, ė├æ¶┐╔═©▀^Öz▓ķCAPFnüĒ┤_Č©Š▀¾w──éĆ═©Ą└ėą▌ö╚ļ▓Č½@ĪŻ▀@ą®ś╦(bi©Īo)ųŠ▒žĒÜė╔▄ø╝■ŪÕ┴ŃĪŻ

CAPCR (CAPCON2.3)ė├ė┌ų▄Ų┌ėŗ(j©¼)╦ŃĪŻ«ö(d©Īng)įO(sh©©)ų├CAPCR×ķ1Ż¼ę╗éĆ▓Č½@▀ģčž╩┬╝■░l(f©Ī)╔·║¾Ż¼TH2║═TL2Ą─ųĄīó▒╗▒Ż┤µŻ¼╚╗║¾ė▓╝■īóūįäėŪÕ│²Č©ĢrŲ„2Ą─ųĄ×ķ0000HĪŻ▀@śė┐╔ęį▒▄├Ō│ŻęÄ(gu©®)▄ø╝■īæ16╬╗ėŗ(j©¼)öĄ(sh©┤)╗“š▀╦ŃĘ©ķ_õNĪŻ

#include "N76E003.h" #include "Common.h" #include "Delay.h" #include "SFR_Macro.h" #include "Function_define.h" //***************** The Following is in define in Fucntion_define.h *************************** //****** Always include Function_define.h call the define you want, detail see main(void) ******* //*********************************************************************************************** #if 0 ////-------------------- Timer2 Capture define -------------------- ////--- Falling Edge ----- //#define IC0_P12_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC1_P11_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x01;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC2_P10_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x02;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC3_P00_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x03;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC3_P04_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x04;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC4_P01_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x05;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC5_P03_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x06;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC6_P05_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x07;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC7_P15_CAP0_FallingEdge_Capture CAPCON1&=0xFC;CAPCON3&=0xF0;CAPCON3|=0x08;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC0_P12_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC1_P11_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x10;CAPCON0|=SET_BIT5;CAPCON0|=SET_BIT5 //#define IC2_P10_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x20;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC3_P00_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x30;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC3_P04_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x40;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC4_P01_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x50;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC5_P03_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x60;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC6_P05_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x70;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC7_P15_CAP1_FallingEdge_Capture CAPCON1&=0xF3;CAPCON3&=0x0F;CAPCON3|=0x80;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC0_P12_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC1_P11_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x10;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC2_P10_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x20;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC3_P00_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x30;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC3_P04_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x40;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC4_P01_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x50;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC5_P03_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x60;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC6_P05_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x70;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 //#define IC7_P15_CAP2_FallingEdge_Capture CAPCON1&=0x0F;CAPCON4&=0xF0;CAPCON4|=0x80;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6 ////----- Rising edge ---- //#define IC0_P12_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC1_P11_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x01;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC2_P10_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x02;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC3_P00_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x03;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC3_P04_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x04;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC4_P01_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x05;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC5_P03_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x06;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC6_P05_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x07;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC7_P15_CAP0_RisingEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x01;CAPCON3&=0xF0;CAPCON3|=0x08;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4; //#define IC0_P12_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0FCAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC1_P11_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x10;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC2_P10_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x20;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC3_P00_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x30;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC3_P04_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x40;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC4_P01_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x50;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC5_P03_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x60;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC6_P05_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x70;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC7_P15_CAP1_RisingEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x04;CAPCON3&=0x0F;CAPCON3|=0x80;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC0_P12_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC1_P11_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x01;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC2_P10_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x02;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC3_P00_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x03;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC3_P04_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x04;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC4_P01_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x05;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC5_P03_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x06;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC6_P05_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x07;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC7_P15_CAP3_RisingEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x10;CAPCON4&=0xF0;CAPCON4|=0x08;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; ////-----BOTH edge ---- //#define IC0_P12_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC1_P11_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x01;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC2_P10_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x02;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC3_P00_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x03;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC3_P04_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x04;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC4_P01_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x05;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC5_P03_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x06;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC6_P05_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x07;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC7_P15_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x08;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 //#define IC0_P12_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5 //#define IC1_P11_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x10;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC2_P10_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x20;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC3_P00_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x30;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC3_P04_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x40;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC4_P01_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x50;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC5_P03_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x60;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC6_P05_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x70;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC7_P15_CAP1_BothEdge_Capture CAPCON1&=0xF3;CAPCON1|=0x08;CAPCON3&=0x0F;CAPCON3|=0x80;CAPCON0|=SET_BIT5;CAPCON2|=SET_BIT5; //#define IC0_P12_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC1_P11_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x01;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC2_P10_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x02;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC3_P00_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x03;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC3_P04_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x04;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC4_P01_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x05;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC5_P03_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x06;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC6_P05_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x07;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define IC7_P15_CAP3_BothEdge_Capture CAPCON1&=0x0F;CAPCON1|=0x20;CAPCON4&=0xF0;CAPCON4|=0x08;CAPCON0|=SET_BIT6;CAPCON2|=SET_BIT6; //#define TIMER2_IC2_DISABLE CAPCON0&=~SET_BIT6 //#define TIMER2_IC1_DISABLE CAPCON0&=~SET_BIT5 //#define TIMER2_IC0_DISABLE CAPCON0&=~SET_BIT4 ///*---------------------------------------------------------------------------------------------------------- //* Timer2 mode define //------------------------------------------------------------------------------------------------------------*/ //#define TIMER2_CAP0_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x89 //#define TIMER2_CAP1_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x8A //#define TIMER2_CAP2_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x8B ///*---------------------------------------------------------------------------------------------------------- //* Timer devider define //----------------------------------------------------------------------------------------------------------*/ //#define TIMER2_DIV_4 T2MOD|=0x10;T2MOD&=0x9F //#define TIMER2_DIV_16 T2MOD|=0x20;T2MOD&=0xAF //#define TIMER2_DIV_32 T2MOD|=0x30;T2MOD&=0xBF //#define TIMER2_DIV_64 T2MOD|=0x40;T2MOD&=0xCF //#define TIMER2_DIV_128 T2MOD|=0x50;T2MOD&=0xDF //#define TIMER2_DIV_256 T2MOD|=0x60;T2MOD&=0xEF //#define TIMER2_DIV_512 T2MOD|=0x70 #endif /************************************************************************************************************ * Timer2 Capture interrupt subroutine ************************************************************************************************************/ void Capture_ISR (void) interrupt 12 { clr_CAPF0; // clear capture0 interrupt flag P1 = C0L; // For capture mode CxL/CxH with data capture from I/O pin P2 = C0H; P12 = ~P12; //toggle GPIO1 to show int printf("\n TM2 CAP 0x%bX",C0H); clr_TF2; } /************************************************************************************************************ * Main function ************************************************************************************************************/ void main (void) { Set_All_GPIO_Quasi_Mode; InitialUART0_Timer3(115200); P00_Input_Mode; P00 = 1; TIMER2_CAP0_Capture_Mode; IC3_P00_CAP0_BothEdge_Capture; set_ECAP; //Enable Capture interrupt set_TR2; //Triger Timer2 set_EA; while(1); }

#define TIMER2_CAP0_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x89

#define TIMER2_CAP1_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x8A

#define TIMER2_CAP2_Capture_Mode T2CON&=~SET_BIT0;T2MOD=0x8B

#define IC0_P12_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC1_P11_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x01;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC2_P10_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x02;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC3_P00_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x03;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC3_P04_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x04;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC4_P01_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x05;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC5_P03_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x06;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC6_P05_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x07;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4 #define IC7_P15_CAP0_BothEdge_Capture CAPCON1&=0xFC;CAPCON1|=0x02;CAPCON3&=0xF0;CAPCON3|=0x08;CAPCON0|=SET_BIT4;CAPCON2|=SET_BIT4

Žļė├Č©ĢrŲ„2Ą─▓Č½@╣”─▄Ż¼Š═╩Ū╬ę▓Č½@Ą─ą┼╠¢┐╔─▄ę¬│¼▀^Č©ĢrŲ„ūŅĖ▀ųĄ65536ĪŻšłĮ╠Ė„╬╗Ė▀╩ų«ö(d©Īng)│¼│÷┴╦Ģ■▓╗Ģ■ę²ŲČ©ĢrŲ„2ųąöÓ

▓Č½@ę▓╩Ūę╗ĘNČ©ĢrŲ„ųąöÓŻ¼Č©ĢrŲ„ėŗ(j©¼)öĄ(sh©┤)ĄĮŅ^ę▓╩Ūę╗ĘNŻ¼ā╔ĘN▓╗═¼Ż¼ę“?y©żn)ķ┐╔─▄śŪų„šfĄ─Ūķør░l(f©Ī)╔·Ż¼«ö(d©Īng)╚╗Ģ■╠ß╣®ę╗éĆųąöÓŻ¼▀@śė─Ń┐╔ęįų¬Ą└─Ńėŗ(j©¼)ĢrķLČ╚░ĪŻ¼ę¬▓╗╚╗▓╗£╩(zh©│n)┴╦ĪŻ

set_ECAP

#define set_ECAP EIE |= SET_BIT2

set_TR2

void Capture_ISR (void) interrupt 12 { clr_CAPF0; // clear capture0 interrupt flag P1 = C0L; // For capture mode CxL/CxH with data capture from I/O pin P2 = C0H; P12 = ~P12; //toggle GPIO1 to show int printf("\n TM2 CAP 0x%bX",C0H); clr_TF2; }

╔Žę╗Ų¬Ż║ĮŌøQQt│╠ą“į┌LinuxŽ┬¤oĘ©▌ö╚ļųą╬─Ą─▐kĘ©

Ž┬ę╗Ų¬Ż║ŪČ╚ļ╩ĮLinuxŽ┬QtĄ─ųą╬─’@╩Š

Æ▀┤aĻP(gu©Īn)ūó╬ęéā

Ó]ŽõŻ║ivy@yingtexin.net

ĄžųĘŻ║╔Ņ█┌╩ą²ł╚Aģ^(q©▒)├±ų╬ĮųĄ└├±ų╬┤¾Ą└973╚f▒ŖØÖžSäō(chu©żng)śI(y©©)ł@AŚØ2śŪA09