���ã��gӭ�M(j��n)�������зf���¿Ƽ�����˾�ٷ��W(w��ng)վ��

���ã��gӭ�M(j��n)�������зf���¿Ƽ�����˾�ٷ��W(w��ng)վ��

SPI����Ӣ�ZSerial Peripheral Interface �Ŀs�������˼�x���Ǵ�������O(sh��)��ӿڡ�

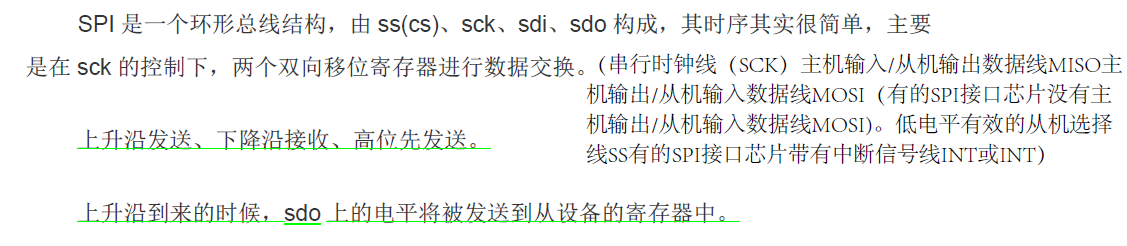

SPI����һ�N���ٵģ�ȫ�p����ͬ����ͨ�ſ�����������оƬ�Ĺ��_��ֻռ���ĸ�������(ji��)�s��оƬ�Ĺ��_��ͬ�r��PCB �IJ����Ϲ�(ji��)ʡ���g���ṩ���㣬���dz����@�N�������õ����ԣ��F(xi��n)��Խ��Խ���оƬ�������@�Nͨ�Ņf(xi��)�h��SPI ��һ���h(hu��n)�ο����Y(ji��)��(g��u)����ss(cs)��sck��sdi��sdo ��(g��u)�ɣ���r���䌍�ܺ��Σ���Ҫ����sck �Ŀ����£��ɂ��p����λ�Ĵ����M(j��n)�Д�(sh��)��(j��)���Q�������ذl(f��)�͡��½��ؽ��ա���λ�Ȱl(f��)�͡������ص����ĕr��sdo �ϵ��ƽ�����l(f��)�͵����O(sh��)��ļĴ����С��½��ص����ĕr��sdi �ϵ��ƽ�������յ����O(sh��)��ļĴ������O(sh��)���C(j��)��

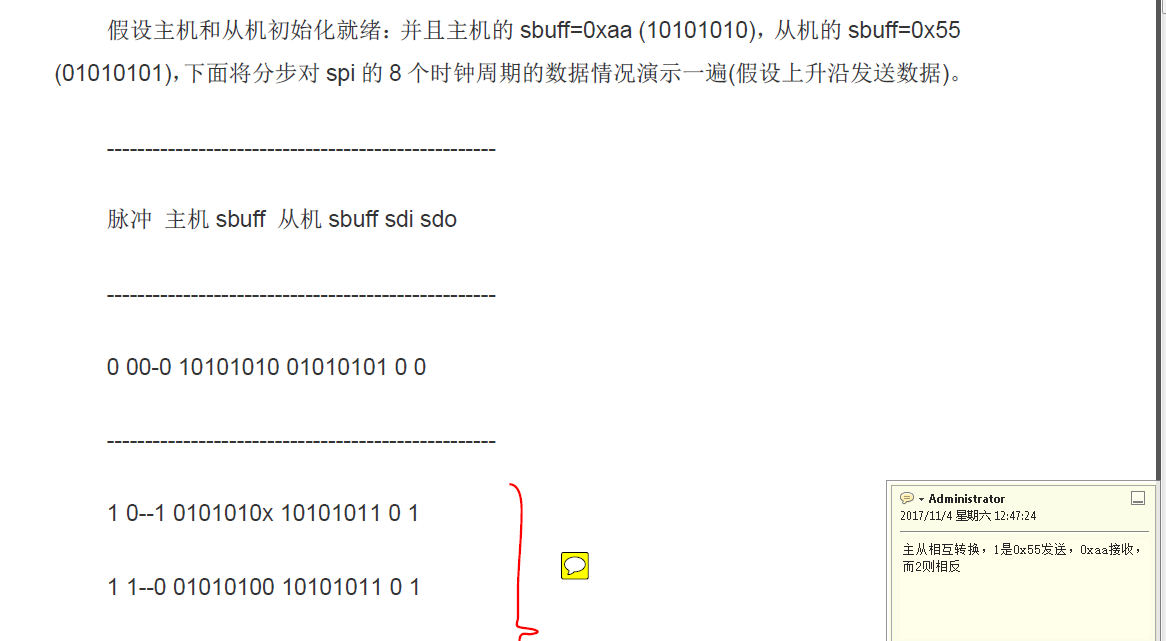

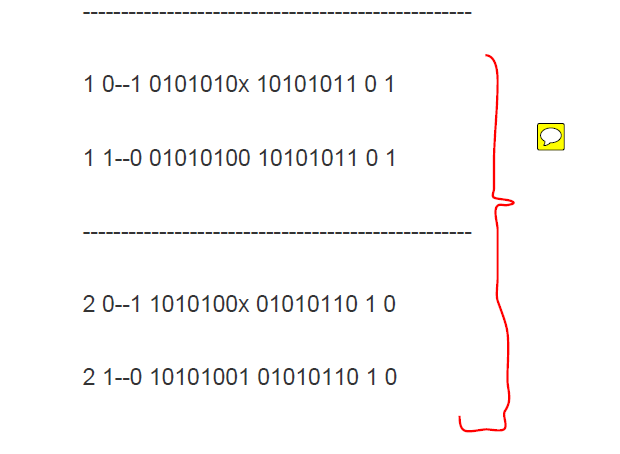

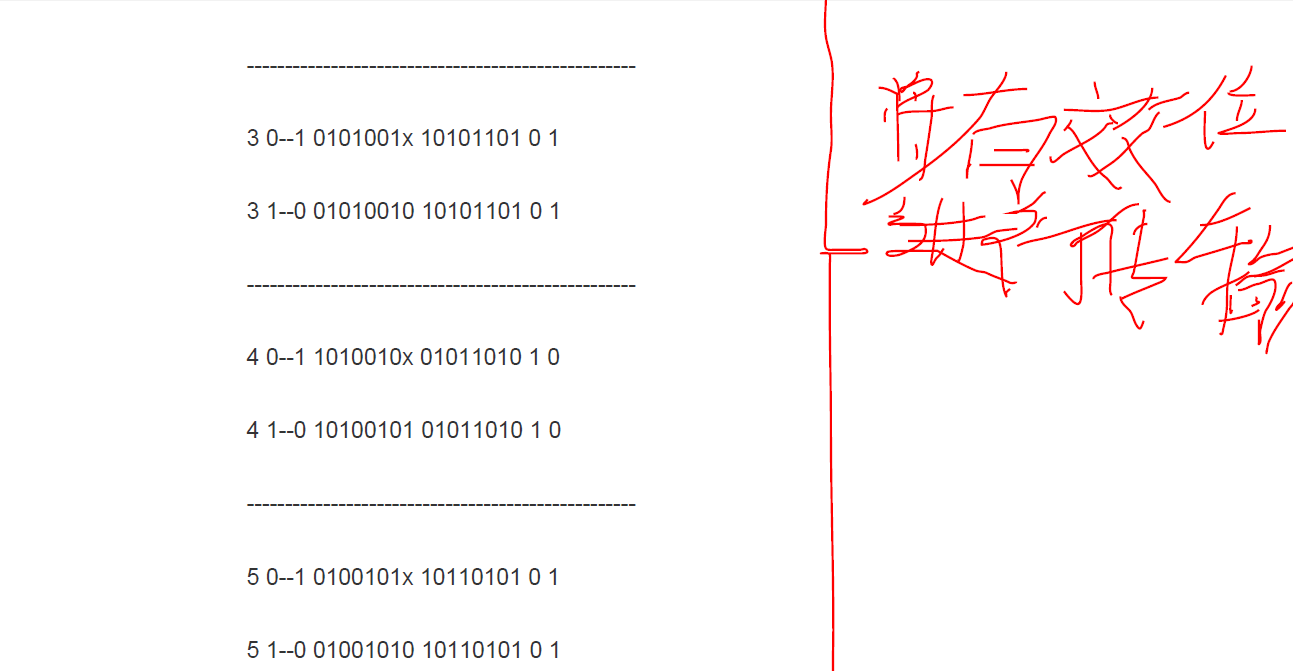

�ęC(j��)��ʼ���;w���������C(j��)��sbuff=0xaa (10101010)���ęC(j��)��sbuff=0x55(01010101)��

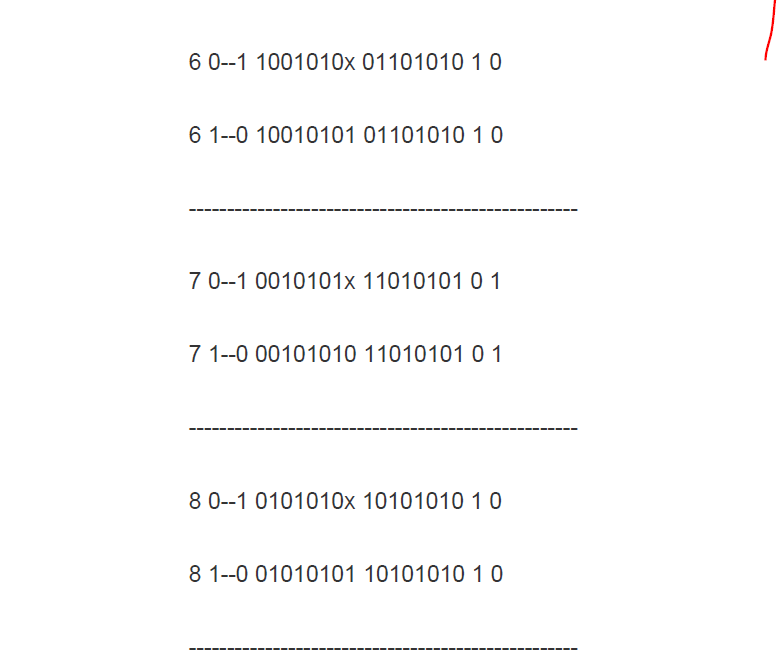

��ô��һ���������ĕr�� ��(sh��)��(j��)������sdo=1���Ĵ���=0101010x���½��ص����ĕr��sdi�ϵ��ƽ�����浽�Ĵ�����ȥ����ô�@�r�Ĵ���=0101010sdi���@���� 8���r��}�_�Ժɂ��Ĵ����ă�(n��i)�ݻ��ཻ�Qһ�Ρ��@�Ӿ������һ��spi�r��

���挢�ֲ���spi ��8 ���r����ڵĔ�(sh��)��(j��)��r��ʾһ��(���O(sh��)�����ذl(f��)�͔�(sh��)��(j��))��

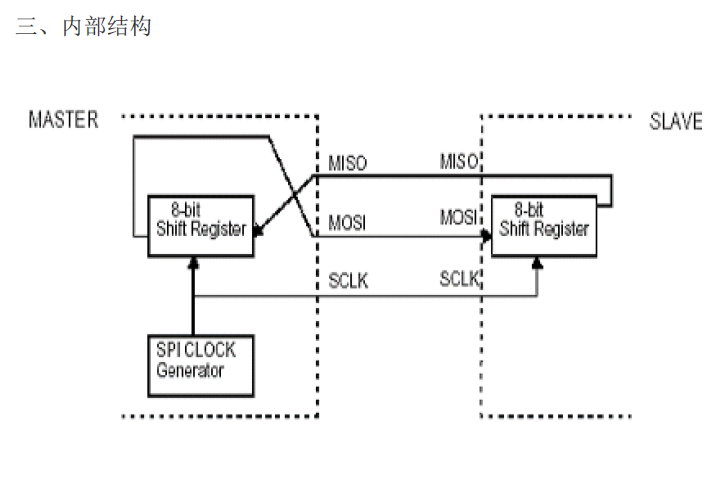

�@�Ӿ�����˃ɂ��Ĵ���8λ�Ľ��Q��������ϱ�ʾ�����ء��±�ʾ�½��أ�sdi��sdo���������C(j��)���Եġ�����ss���_�������C(j��)�ĕr�ęC(j��)���������ױ����x��ęC(j��)������ęC(j��)���Ǖr��������Ƭ�x�_�á�����(j��)���Ϸ�����һ�������Ă���������16λ�����ɂ��ֹ�(ji��)����飬�������C(j��)Ҫ�l(f��)�������^ȥ��Ȼ��ęC(j��)����(j��)���C(j��)�������(zh��n)�䔵(sh��)��(j��)�����C(j��)����һ��8λ�r����ڲŰє�(sh��)��(j��)�x���� SPI ������Motorola��˾�Ƴ�������ͬ���ӿڣ�ͬ������3����ʽ�M(j��n)��ͨ��:һ�l�r犾�SCK��һ�l��(sh��)��(j��)ݔ�뾀MOSI��һ�l��(sh��)��(j��)ݔ����MISO;����CPU�c���N��������M(j��n)��ȫ�p����ͬ������ͨӍ��SPI��Ҫ���c��:����ͬ�r�l(f��)���ͽ��մ��Д�(sh��)��(j��);���Ԯ�(d��ng)�����C(j��)��ęC(j��)����;�ṩ�l�ʿɾ��̕r�;�l(f��)�ͽY(ji��)�� �Д���(bi��o)־;���_ͻ���o(h��);�����������o(h��)�ȡ��Dʾ��SPI�����������ķN��ʽ������ʹ�õ����V������SPI0��SPI3��ʽ (������ʾ):

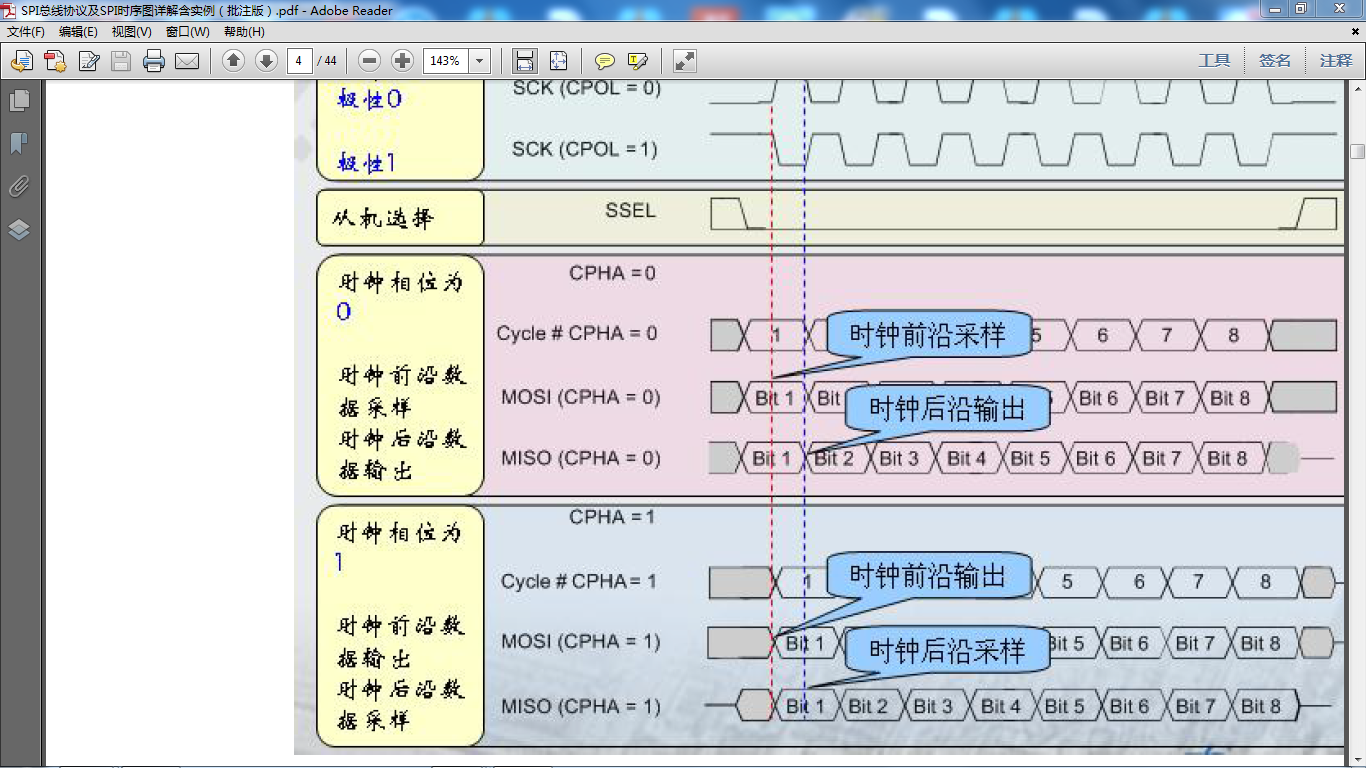

SPI�����ķN������ʽ SPI ģ�K���˺����O(sh��)�M(j��n)�Д�(sh��)��(j��)���Q������(j��)���O(sh��)����Ҫ����ݔ������ͬ���r犘O�Ժ���λ�����M(j��n)�����ã��r犘O�ԣ�CPOL������ݔ�f(xi��)�h�]���ش��Ӱ푡���� CPOL=0������ͬ���r犵Ŀ��e��B(t��i)����ƽ�����CPOL=1������ͬ���r犵Ŀ��e��B(t��i)����ƽ���r���λ��CPHA���܉����������x��ɷN��ͬ�Ă�ݔ�f(xi��)�h֮һ�M(j��n)�Д�(sh��)��(j��)��ݔ�����CPHA=0���ڴ���ͬ���r犵ĵ�һ����׃�أ��������½�����(sh��)��(j��)���ɘӣ����CPHA=1���ڴ���ͬ���r犵ĵڶ�����׃�أ��������½�����(sh��)��(j��)���ɘӡ�SPI��ģ�K���c֮ͨ�ŵ����O(sh��)��r���λ�͘O�ԑ�(y��ng)ԓһ�¡�

SPI��������1������ͬ���r���̖���Լ�2����(sh��)��(j��)����

SPIģ�K���˺����O(sh��)�M(j��n)�Д�(sh��)��(j��)���Q������(j��)���O(sh��)����Ҫ����ݔ������ͬ���r犘O�Ժ���λ�����M(j��n)�����ã��r犘O�ԣ�CPOL������ݔ�f(xi��)�h�]���ش��Ӱ푡����CPOL=0������ͬ���r犵Ŀ��e��B(t��i)����ƽ�����CPOL=1������ͬ���r犵Ŀ��e��B(t��i)����ƽ���r���λ��CPHA���܉����������x��ɷN��ͬ�Ă�ݔ�f(xi��)�h֮һ�M(j��n)�Д�(sh��)��(j��)��ݔ�����CPHA=0���ڴ���ͬ���r犵ĵ�һ����׃�أ��������½�����(sh��)��(j��)���ɘӣ����CPHA=1���ڴ���ͬ���r犵ĵڶ�����׃�أ��������½�����(sh��)��(j��)���ɘӡ�SPI��ģ�K���c֮ͨ�ŵ����O(sh��)���r���λ�͘O�ԑ�(y��ng)ԓһ�¡�SPI�ӿڕr����D3���D4��ʾ��

�@�Ӿ�����˃ɂ��Ĵ���8 λ�Ľ��Q�������0--1 ��ʾ�����ء�1--0 ��ʾ�½��أ�sdi��sdo ���������C(j��)���Եġ�����(j��)���Ϸ�����һ�������Ă���������16 λ�����ɂ��ֹ�(ji��)����飬�������C(j��)Ҫ�l(f��)�������^ȥ��Ȼ��ęC(j��)����(j��)���C(j��)������(zh��n)�䔵(sh��)��(j��)�����C(j��)����һ��8 λ�r����ڲŰє�(sh��)��(j��)�x����SPI ������Motorola ��˾�Ƴ�������ͬ���ӿڣ�ͬ������3 ����ʽ�M(j��n)��ͨ��:һ�l�r犾�SCK��һ�l��(sh��)��(j��)ݔ�뾀MOSI��һ�l��(sh��)��(j��)ݔ����MISO;���� CPU �c���N��������M(j��n)��ȫ�p����ͬ������ͨӍ��SPI ��Ҫ���c��:����ͬ�r�l(f��)���ͽ��մ��Д�(sh��)��(j��);���Ԯ�(d��ng)�����C(j��)��ęC(j��)����;�ṩ�l�ʿɾ��̕r�;�l(f��)�ͽY(ji��)���Д���(bi��o)־;���_ͻ���o(h��);�����������o(h��)�ȡ�

SPI �������ķN������ʽ(SP0, SP1, SP2, SP3)������ʹ�õ����V������SPI0 ��SPI3 ��ʽ��SPI ģ�K���˺����O(sh��)�M(j��n)�Д�(sh��)��(j��)���Q������(j��)���O(sh��)����Ҫ����ݔ������ͬ���r犘O�Ժ���λ�����M(j��n)�����ã��r犘O��(CPOL)����ݔ�f(xi��)�h�]���ش��Ӱ푡����CPOL=0������ͬ���r犵Ŀ��e��B(t��i)����ƽ�����CPOL=1������ͬ���r犵Ŀ��e��B(t��i)����ƽ���r���λ(CPHA)�܉����������x��ɷN��ͬ�Ă�ݔ�f(xi��)�h֮һ�M(j��n)�Д�(sh��)��(j��)��ݔ����� CPHA=0���ڴ���ͬ���r犵ĵ�һ����׃��(�������½�)��(sh��)��(j��)���ɘӣ����CPHA=1���ڴ���ͬ���r犵ĵڶ�����׃��(�������½�)��(sh��)��(j��)���ɘӡ� SPI ��ģ�K���c֮ͨ�ŵ����O(sh��)���r���λ�͘O�ԑ�(y��ng)ԓһ�¡�SPI �r��DԔ��-SPI �ӿ���ģʽ0 ��ݔ����һλ��(sh��)��(j��)�ĕr��

SPI �ӿ���ģʽ0 ��ݔ����һλ��(sh��)��(j��)�ĕr��

SPI �ӿ����ķN��ͬ�Ĕ�(sh��)��(j��)��ݔ�r��ȡ�Q��CPOL ��CPHL �@��λ�ĽM�ϡ��D1 ��

���F(xi��n)���@�ķN�r��

�r���c CPOL��CPHL ���P(gu��n)ϵҲ���ԏĈD�п�����

�D1

�D1

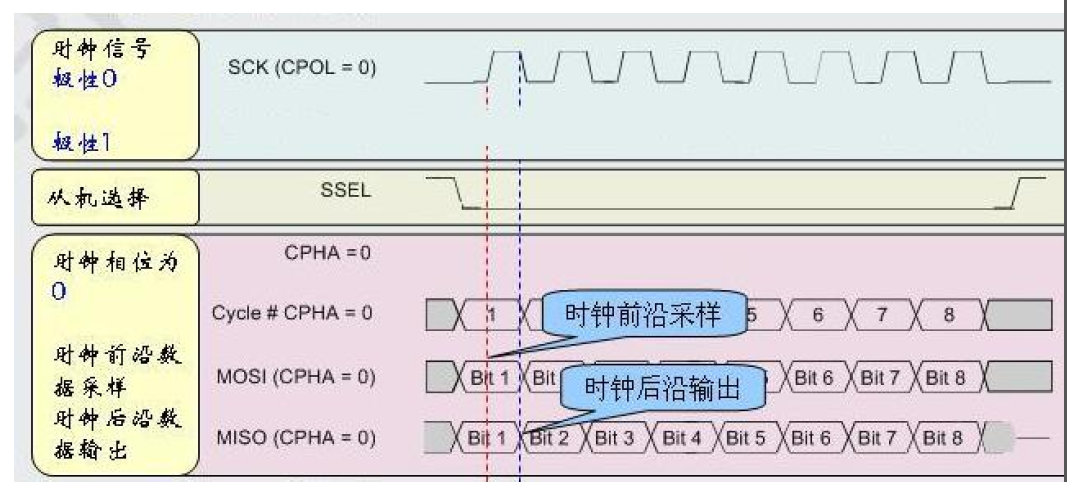

CPOL ���Á�Q��SCK �r���̖���e�r���ƽ��CPOL��0�����e�ƽ����ƽ��CPOL��1 �r�����e�ƽ����ƽ��CPHA ���Á�Q���ɘӕr�̵ģ�CPHA=0����ÿ�����ڵĵ�һ���r��زɘӣ�CPHA��1����ÿ�����ڵĵڶ����r��زɘӡ��҂����f�fģʽ 0 �@�N�r��CPOL��0��CPHA��0�������D1 ������D2

�D2

�҂����P(gu��n)עSCK �ĵ�һ���r����ڣ��ڕr犵�ǰ�زɘӔ�(sh��)��(j��)�������أ���һ���r��أ����ڕr犵ĺ���ݔ����(sh��)��(j��)���½��أ��ڶ����r��أ���

���ȁ�������������������ݔ���ڣ�MOSI��ݔ���Ĕ�(sh��)��(j��)bit1�����ڕr犵�ǰ�ر��������ɘӣ������������ںΕr��ݔ�� bit1 ���أ�bit1 ��ݔ���r�̌��H����SCK ��̖��Ч��ǰ���� SCK ��������߀Ҫ��낀�r����ڡ�bit1 ��ݔ���r���cSSEL ��̖�]���P(gu��n)ϵ���ف�������������������ݔ��� MISO ͬ�����ڕr犵�ǰ�زɘӏ�����ݔ����bit1 �ģ��Ǐ����������ںΕr��ݔ��bit1 ���ء����������� SSEL ��̖��Ч������ݔ��bit1���M�ܴ˕rSCK ��̖߀�]����Ч���P(gu��n)��������������͏�����ݔ�� bit1 λ�ĕr�̣����ԏĈD3��4 �еõ���C��

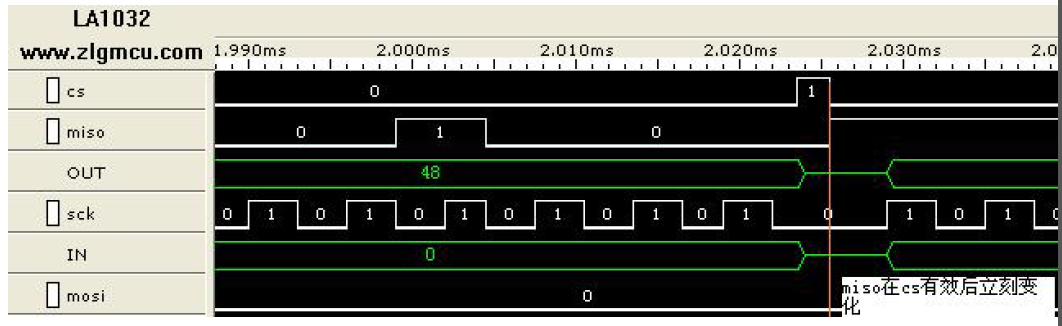

ע��D3 �У�CS ��̖��Ч���ƽ��Ч��ע��CS �½��غ�l(f��)������r�����������ӕr�����ӕr��һ�Εr�g��֮������(sh��)��(j��)�Ĵ���������Ҫ�l(f��)�͵Ĕ�(sh��)��(j��)�����^��������ݔ�� bit1����r��MOSI�������Կ�����bit1��ֵ��1������SCK ��̖��Ч֮ǰ�İ낀�r����ڵĕr���_ʼݔ���ģ��cCS ��̖�o�P(gu��n)�������� SCK �ĵ�һ���r����ڵ����������ñ��������ɘӡ�

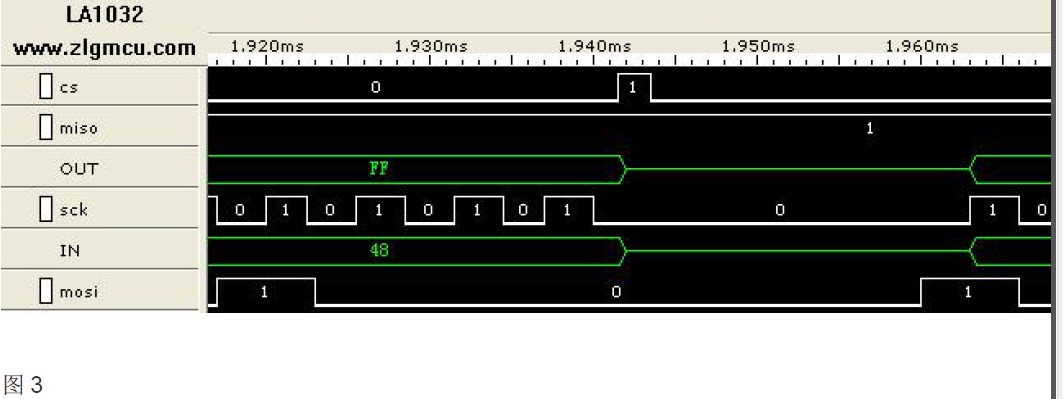

�D4

�D4 �У�ע�⿴CS ��MISO ��̖���҂����Կ�����CS ��̖��Ч����������ݔ����bit1��ֵ��1����ͨ���҂��M(j��n)�е� spi ��������16 λ�ġ�

�D5 ӛ��˵�һ���ֹ�(ji��)�͵ڶ����ֹ�(ji��)�g���㕽ӵ��^�̡�

��һ���ֹ�(ji��)�����һλ��SCK �������ر��ɘӣ��S���SCK �½��أ���������ݔ���˵ڶ����ֹ�(ji��)�ĵ�һλ��

һ�����g(sh��)����

һ�����g(sh��)����

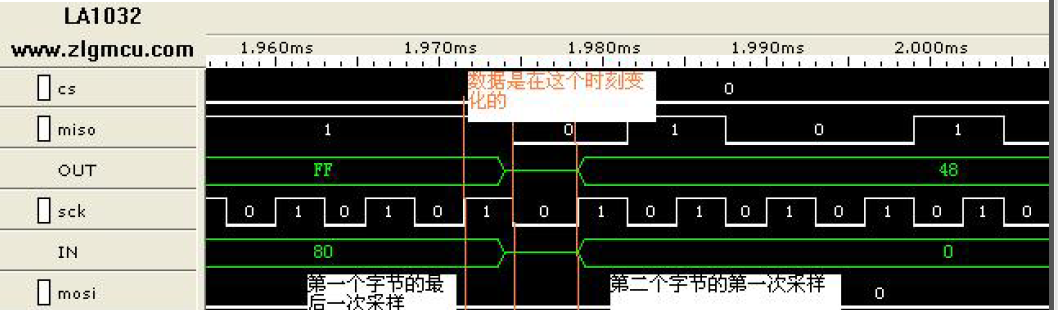

SPI �ӿ���Motorola ���������ȫ�p������ͬ����������ӿڣ���������ģʽ��Master Slave���ܘ�(g��u)��֧�ֶ�slave ģʽ��(y��ng)�ã�һ��H֧�ֆ�Master���r��� Master ���ƣ��ڕr���λ�}�_�£���(sh��)��(j��)��λ��ݔ����λ��ǰ����λ�ں�MSBfirst����SPI �ӿ���2 ������(sh��)��(j��)������ȫ�p��ͨ�ţ�Ŀǰ��(y��ng)���еĔ�(sh��)��(j��)���ʿ��_(d��)��Mbps��ˮƽ��

�����ӿڶ��x

SPI �ӿڹ���4 ����̖�����քe�ǣ��O(sh��)���x���r犾�������ݔ����(sh��)��(j��)��������ݔ�딵(sh��)��(j��)����

��1��MOSI����������(sh��)��(j��)ݔ������������(sh��)��(j��)ݔ��

��2��MISO����������(sh��)��(j��)ݔ�룬��������(sh��)��(j��)ݔ��

��3��SCLK ���r���̖�����������a(ch��n)��

��4��/SS��������ʹ����̖��������������

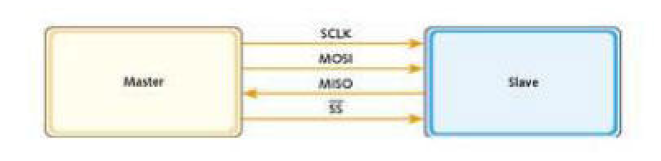

�ġ���ݔ�r��

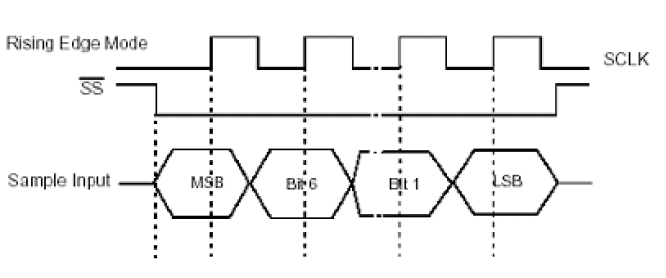

SPI �ӿ��ڃ�(n��i)��Ӳ�����H���ǃɂ����ε���λ�Ĵ���,��ݔ?sh��)Ĕ?sh��)��(j��)��8 λ�����������a(ch��n)���ď�����ʹ����̖����λ�}�_�£���λ��ݔ����λ��ǰ����λ�ں����D��ʾ����SCLK

���½����ϔ�(sh��)��(j��)��׃��������һλ��(sh��)��(j��)��������λ�Ĵ�����

SPI �ӿڛ]��ָ���������ƣ��]�Б�(y��ng)��C(j��)�ƴ_�J(r��n)�Ƿ���յ���(sh��)��(j��)��

SPI �ӿڕr����ã������O(sh��)���@߅���� SPI �ӿڕr犵ĕr��һ��ҪŪ������O(sh��)��ĕr�Ҫ��������O(sh��)���@߅�ĕr犘O�Ժ���λ�����ԏ��O(sh��)������(zh��n)�ġ�����ڕr犘O�Ե�������һ��Ҫ��������O(sh��)�����ڕr犵�������߀���½��ؽ��Ք�(sh��)��(j��)�����ڕr犵��½���߀��������ݔ����(sh��)��(j��)����Ҫע����ǣ��������O(sh��)���SDO �B�ӏ��O(sh��)���SDI�����O(sh��)���SDO �B�����O(sh��)���SDI�����O(sh��)��SDI ���յĔ�(sh��)��(j��)�����O(sh��)���SDO �l(f��)���^���ģ�MOSI�������O(sh��)��SDI ���յĔ�(sh��)��(j��)�Ǐ��O(sh��)��SDO �l(f��)���^����(MISO)���������O(sh��)���@߅SPI �r犘O�Ե����ã���SDO �����ã������O(sh��)���SDI ���Ք�(sh��)��(j��)�ĘO�����෴�ģ������O(sh��)��SDO �l(f��)�͔�(sh��)��(j��)�ĘO������ͬ�ġ�

�����@��Ԓ��SychipWlan8100 Module Spec ���f�ģ�����f���˕r犘O����������õģ�

The 81xx module will always input data bits at the rising edge of the clock, and the

host will always output data bits on the falling edge of the clock.

��˼�ǣ����O(sh��)���ڕr犵��½��ذl(f��)�͔�(sh��)��(j��)�����O(sh��)���ڕr犵������ؽ��Ք�(sh��)��(j��)��������O(sh��)

���@߅SPI �r犘O�ԑ�(y��ng)ԓ���Þ��½�����Ч��

���磬�����@��Ԓ��ժ�� LCD Driver IC SSD1289��

SDI is shifted into 8-bit shift register on every rising edge of SCK in the order of

data bit 7, data bit 6 …… data bit 0.

��˼�ǣ����O(sh��)��SSD1289 �ڕr犵������ؽ��Ք�(sh��)��(j��)�������ǰ��Տĸ�λ����λ

�������Ք�(sh��)��(j��)�ġ�������O(sh��)���SPI �r犘O��ͬ�ӑ�(y��ng)ԓ���Þ��½�����Ч��

ͨ�^ SPI_CR1 �Ĵ����е� CPOL �� CPHA λ��������ܛ���x���ķN���ܵĕr���P(gu��n)ϵ��CPOL���r犘O�ԣ�λ���Ʋ����κΔ�(sh��)��(j��)�r�ĕr��ƽ��B(t��i)����λ���������͏� ���������� �á������(f��)λ CPOL��SCK ���_�ڿ��e��B(t��i)̎�ڵ��ƽ������� CPOL �� 1��SCK ���_�� ���e��B(t��i)̎�ڸ��ƽ��

����� CPHA���r���λ��λ�� 1���t SCK ���_�ϵĵڶ���߅�أ������(f��)λ CPOL λ���t ���½��أ������ CPOL λ�� 1���t�������أ��� MSBit �ɘӡ������ڵڶ����r�߅���i�� ��(sh��)��(j��)�������(f��)λ CPHA λ���t SCK ���_�ϵĵ�һ��߅�أ������ CPOL λ�� 1���t���½� �أ������(f��)λ CPOL λ���t�������أ��� MSBit �ɘӡ������ڵ�һ���r�߅���i�攵(sh��)��(j��)��

CPOL���r犘O�ԣ��� CPHA���r���λ��λ�ĽM�������x��(sh��)��(j��)���@�r�߅�ء�

ͨӍ��ͨ�^��(sh��)��(j��)���Q��ɵģ��@����Ҫ֪��SPI�Ǵ���ͨӍ�f(xi��)�h��Ҳ�����f��(sh��)��(j��)��һλһλ�Ă�ݔ?sh��)ġ��@����SCK�r犾����ڵ�ԭ����SCK�ṩ�r��}�_��SDI��SDO�t���ڴ��}�_��ɔ�(sh��)��(j��)��ݔ����(sh��)��(j��)ݔ��ͨ�^ SDO������(sh��)��(j��)�ڕr������ػ��½��ؕr��׃���ھo�������½��ػ������ر��xȡ�����һλ��(sh��)��(j��)��ݔ��ݔ��Ҳʹ��ͬ��ԭ�����@�ӣ�������8�Εr���̖�ĸ�׃�����غ����؞�һ�Σ����Ϳ������8λ��(sh��)��(j��)�Ă�ݔ��

Ҫע����ǣ�SCK��̖��ֻ�����O(sh��)����ƣ����O(sh��)�䲻�ܿ�����̖����ͬ�ӣ���һ������SPI���O(sh��)���У�������һ�������O(sh��)�䡣�@�ӂ�ݔ?sh��)����c���@�ӵĂ�ݔ��ʽ��һ����(y��u)�c���c��ͨ�Ĵ���ͨӍ��ͬ����ͨ�Ĵ���ͨӍһ���B�m(x��)��������8λ��(sh��)��(j��)����SPI���S��(sh��)��(j��)һλһλ�Ă��ͣ��������S��ͣ�����SCK�r犾��������O(sh��)����ƣ���(d��ng)�]�Еr���׃�r�����O(sh��)�䲻�ɼ�����͔�(sh��)��(j��)��Ҳ�����f�����O(sh��)��ͨ�^��SCK�r犾��Ŀ��ƿ�����Ɍ�ͨӍ�Ŀ��ơ�SPI߀��һ����(sh��)��(j��)���Q�f(xi��)�h�����SPI�Ĕ�(sh��)��(j��)ݔ���ݔ�����������������Sͬ�r��ɔ�(sh��)��(j��)��ݔ���ݔ������ͬ��SPI�O(sh��)��Č��F(xi��n)��ʽ���M��ͬ����Ҫ�ǔ�(sh��)��(j��)��׃�Ͳɼ��ĕr�g��ͬ���ڕr���̖���ػ����زɼ��в�ͬ���x�����wՈ�������P(gu��n)�������ęn��

���c���c��ͨ���У�SPI�ӿڲ���Ҫ�M(j��n)�Ќ�ַ�������Ҟ�ȫ�p��ͨ�ţ��@�ú��θ�Ч���ڶ������O(sh��)���ϵ�y(t��ng)�У�ÿ�����O(sh��)����Ҫ������ʹ����̖��Ӳ���ϱ�I2Cϵ�y(t��ng)Ҫ����(f��)�sһЩ��

���SPI�ӿڵ�һ��ȱ�c���]��ָ���������ƣ��]�Б�(y��ng)��C(j��)�ƴ_�J(r��n)�Ƿ���յ���(sh��)��(j��)��

�a�䣺

��������һ��Ԓ��SPI��ģ�K���c֮ͨ�ŵ����O(sh��)��r���λ�͘O�ԑ�(y��ng)ԓһ�¡����������@��Ԓ��2����˼����һ�����O(sh��)��SPI�r犺͘O�Ե����Ñ�(y��ng)ԓ�����O(sh��)��Q������������ߵ����Ñ�(y��ng)ԓ����һ�£������O(sh��)���SDOͬ���O(sh��)���SDO����һ�£����O(sh��)���SDIͬ���O(sh��)���SDI����һ�¡���������O(sh��)������SCLK�Ŀ����£�ͬ�r�l(f��)�ͺͽ��Ք�(sh��)��(j��)����ͨ�^2���p����λ�Ĵ��������Q��(sh��)��(j��)������ԭ����ʾ���D��

���������C(j��)SDO�l(f��)�͔�(sh��)��(j��)1��ͬ�r���O(sh��)��SDO�l(f��)�͔�(sh��)��(j��)0���o������SCLK���½��صĕr����O(sh��)���SDI���յ������C(j��)�l(f��)���^���Ĕ�(sh��)��(j��)1��ͬ�r���C(j��)Ҳ���յ��ˏ��O(sh��)��l(f��)���^���Ĕ�(sh��)��(j��)0.

SPI�f(xi��)�h�ĵ�

SPI�ӿڕr������ĵã�

�����O(sh��)���@߅����SPI�ӿڕr犵ĕr��һ��ҪŪ������O(sh��)��ĕr�Ҫ��������O(sh��)���@߅�ĕr犘O�Ժ���λ�����ԏ��O(sh��)������(zh��n)�ġ�����ڕr犘O�Ե�������һ��Ҫ��������O(sh��)�����ڕr犵�������߀���½��ؽ��Ք�(sh��)��(j��)�����ڕr犵��½���߀��������ݔ����(sh��)��(j��)����Ҫע����ǣ��������O(sh��)���SDO�B�ӏ��O(sh��)���SDI�����O(sh��)���SDO�B�����O(sh��)���SDI�����O(sh��)��SDI���յĔ�(sh��)��(j��)�����O(sh��)���SDO�l(f��)���^���ģ����O(sh��)��SDI���յĔ�(sh��)��(j��)�Ǐ��O(sh��)��SDO�l(f��)���^���ģ��������O(sh��)���@߅SPI�r犘O�Ե����ã���SDO�����ã������O(sh��)���SDI���Ք�(sh��)��(j��)�ĘO�����෴�ģ������O(sh��)��SDO�l(f��)�͔�(sh��)��(j��)�ĘO������ͬ�ġ������@��Ԓ��Sychip Wlan8100 Module Spec���f�ģ�����f���˕r犘O����������õģ�

The 81xx module will always input data bits at the rising edge of the clock, and the host will always output data bits on the falling edge of the clock.

��˼�ǣ����O(sh��)���ڕr犵��½��ذl(f��)�͔�(sh��)��(j��)�����O(sh��)���ڕr犵������ؽ��Ք�(sh��)��(j��)��������O(sh��)���@߅SPI�r犘O�ԑ�(y��ng)ԓ���Þ��½�����Ч��

���磬�����@��Ԓ��ժ��LCD Driver IC SSD1289��

SDI is shifted into 8-bit shift register on every rising edge of SCK in the order of data bit 7, data bit 6 …… data bit 0.

��˼�ǣ����O(sh��)��SSD1289�ڕr犵������ؽ��Ք�(sh��)��(j��)�������ǰ��Տĸ�λ����λ�������Ք�(sh��)��(j��)�ġ�������O(sh��)���SPI�r犘O��ͬ�ӑ�(y��ng)ԓ���Þ��½�����Ч��

�r犘O�Ժ���λ�������_��(sh��)��(j��)���܉�(zh��n)�_�İl(f��)�ͺͽ��ա���ˑ�(y��ng)ԓ���Տ��O(sh��)���SPI�ӿڕr�����Spec�ęn�f�������_�������O(sh��)��ĕr犡�

������ͬ�r�l(f��)�ͣ�ͬ�r���գ���ǰ�ذl(f��)�͵ĕr�ęC(j��)Ҳ�l(f��)�ͣ��ں��ؽ��յĕr�ęC(j��)Ҳ���ա�

�����҂�������M451�ij���

SPI����һ�N���ٵģ�ȫ�p����ͬ����ͨ�ſ������乤��ģʽ�ЃɷN����ģʽ�͏�ģʽ���o

Փ�ǷNģʽ����֧��

3Mbit/s �����ʣ�����߀���Ђ�ݔ��ɘ�(bi��o)־�͌��_ͻ���o(h��)��(bi��o)־����Ŀǰ��ֹ����ʹ���^�ľ�

��SPI ���������������Ǵ惦оƬ Eprom��at25128����ʹ���^���У��l(f��)�F(xi��n)�Ĵ_�����@�N

�����ă�(y��u)�c��������P89LPC900 ��Ƭ�C(j��)��SPI ���������SPI ������ͨ��ʹ��Ҏ(gu��)�t��

SPICLK��MOSI��MISO��/SS������SPICLK

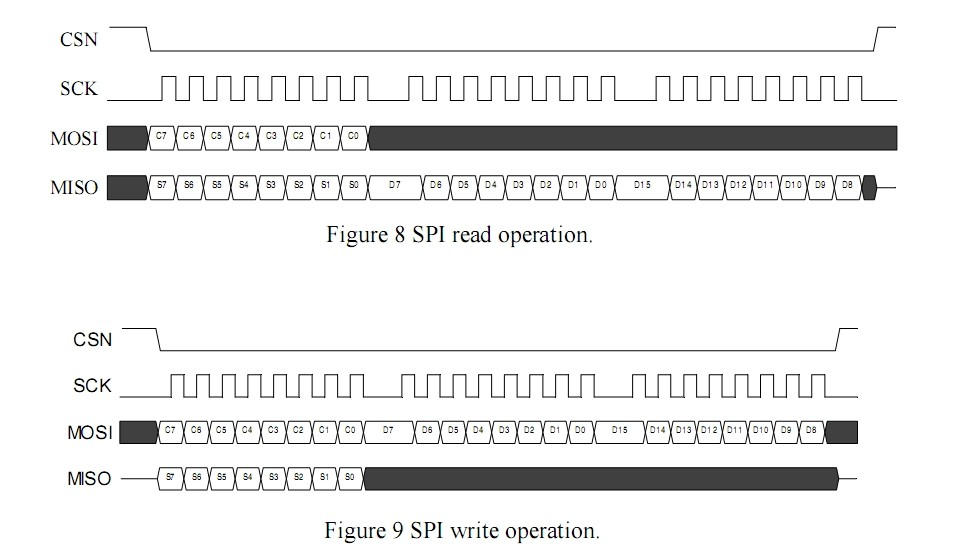

������SPI �����Ĺ��Õr犣�MOSI��MISO �������C(j��)���ęC(j��)��ݔ��ݔ���Ę�(bi��o)־��MOSI ��

���C(j��)��ݔ�����ęC(j��)��ݔ�룬MISO �����C(j��)��ݔ�룬�ęC(j��)��ݔ����/SS �ǏęC(j��)�Ę�(bi��o)־���_����

����ͨ�ŵăɂ�SPI ������������/SS ���_���ƽ�͵��ǏęC(j��)���෴/SS ���_���ƽ�ߵ���

���C(j��)����һ��SPI ͨ��ϵ�y(t��ng)�У���������C(j��)��

SPI �����������óɆ����Ώģ��������ģ��������ġ�

�ߴa�P(gu��n)ע�҂�

�]�䣺ivy@yingtexin.net

��ַ�����������A�^(q��)���νֵ����δ��973�f�����S��(chu��ng)�I(y��)�@A��2��A09