你不會以為EDA軟件開發(fā)就只需要軟件工程師吧?

在剛剛過去的12月28日,EDA廠商概倫電子正式登陸科創(chuàng)板。作為國內(nèi)EDA板塊第一股,概倫電子一上市就受到狂熱追捧,開盤第一天股價漲幅53.57%,市盈率達(dá)到驚人的575.28倍。

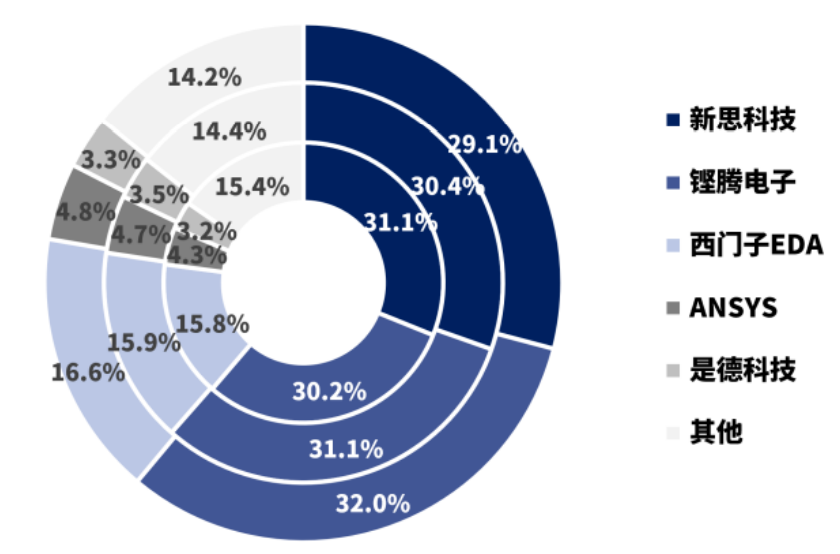

EDA第一股在金融市場上的成功卻掩飾不了這個行業(yè)嚴(yán)峻的現(xiàn)實。根據(jù)概倫電子招股說明書中披露的行業(yè)數(shù)據(jù)顯示,三大EDA巨頭——新思科技Synopsys、鏗騰電子Cadence、西門子EDA(原明導(dǎo)Mentor Graphics)——全球市占率超過77%,如果加上第四是德科技Keysight、第五ANSYS,那么前五大國外EDA 公司累計占有了約 85%的份額,留下國產(chǎn)廠商在夾縫中生存。

圖:全球EDA市場份額,內(nèi)圈至外圈分別為 2018-2020 年數(shù)據(jù)(資料來源:概倫電子招股說明書)

IC產(chǎn)業(yè)卡脖子的危機讓我們認(rèn)識到了EDA軟件的重要性和落后的現(xiàn)實,但從軟件工程的角度來看,我國并不是一個軟件開發(fā)的弱國。每年從各大院校畢業(yè)的軟件工程師不計其數(shù),程序員如今依然是一個高收入的金領(lǐng)工種。比如在OA信創(chuàng)領(lǐng)域,在國家的推動下,計算機操作系統(tǒng)、辦公自動化軟件、數(shù)據(jù)庫軟件、云計算軟件等等基礎(chǔ)軟件都在陸續(xù)實現(xiàn)國產(chǎn)替代。

那我們不禁要問,同樣是基礎(chǔ)軟件,為什么國產(chǎn)EDA目前的形勢依然不容樂觀?換句話來問,EDA軟件到底難在哪兒,以至于我國這么龐大的軟件人才儲備竟然還搞不定?

EDA:先有物理,后有軟件

EDA的作用一句話就可以說明白:用軟件模擬的方式達(dá)到預(yù)設(shè)的各種電路性能指標(biāo),然后再去foundry廠流片。如果IC設(shè)計時各種參數(shù)都達(dá)標(biāo),但片子流回來一測,數(shù)據(jù)飄到天上去,這就是徹底的失敗。那么如何保證EDA里的電路設(shè)計跟真實芯片之間性能一致呢?

答案是:精準(zhǔn)的器件模型。

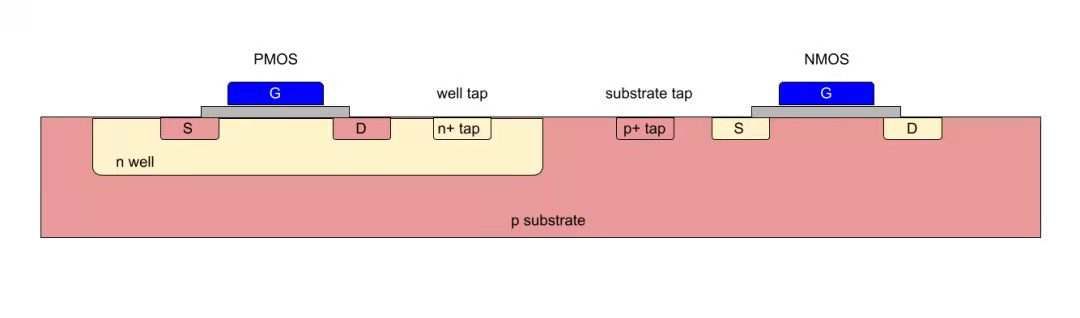

IC電路的基本單元是晶體管,稱為CMOS管。在EDA里需要一套數(shù)學(xué)公式來描述晶體管的基本物理參數(shù)關(guān)系,比如最基本的柵極G、源極S、漏極D的電壓—電流關(guān)系,類似于電阻的電壓和電流公式I=U/R。晶體管的U-I公式當(dāng)然會更復(fù)雜,但基本思路和原理是一致的。這套數(shù)學(xué)公式稱為晶體管的器件模型。

圖:N型晶體管和P型晶體管截面圖

用數(shù)學(xué)公式表征的器件模型就是EDA軟件和實際工藝制程之間的橋梁,器件模型越準(zhǔn)確,EDA仿真的電路就越接近于真實芯片。那這個器件模型很難嗎?

答案是:難,特別難。

由于芯片的種類和應(yīng)用場景多種多樣,器件模型要能反映晶體管在各種工作條件下的實際情況,那么模型的類型至少要包括:直流、交流、靜態(tài)、瞬態(tài)、噪聲、壓力、射頻、可靠性……

更大的難度在于,如今晶體管的尺寸已經(jīng)縮小至納米尺度,在這個尺度下,晶體管會產(chǎn)生很多量子效應(yīng),比如短溝道效應(yīng)、彈道輸運效應(yīng)……工藝制程每前進(jìn)一個世代,晶體管尺寸每縮小一次,就會出現(xiàn)更多物理效應(yīng)。對晶體管建模先要從量子力學(xué)、半導(dǎo)體物理等理論層面理解一個新效應(yīng)背后的物理機理是什么,然后再用數(shù)學(xué)公式去描述新產(chǎn)生的物理效應(yīng)對電流、電壓、電阻等基本物理量的影響。

這還沒完。

芯片大致可以分為數(shù)字芯片和模擬芯片,數(shù)字芯片里晶體管的的工作模式只有高電壓和低電壓,即“1”和“0”。實際上,數(shù)字芯片會允許有一個可接受的工作電壓區(qū)間,比如說電壓在0.1—0.3V被視為“0”,電壓在0.3—06V被視為“1” 。那模型的精度就可以有一定的容錯率。

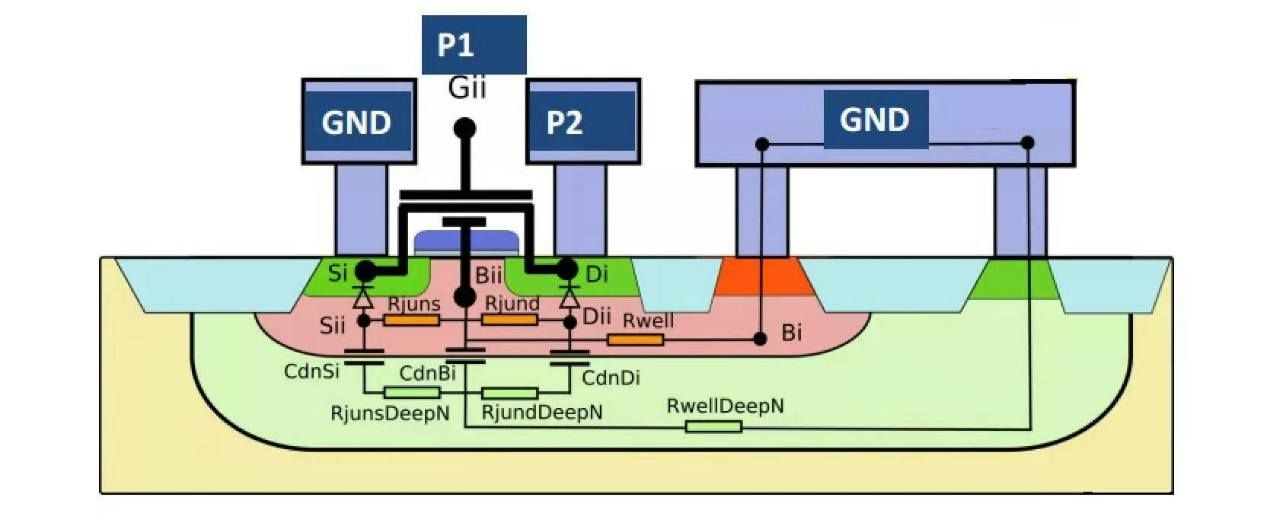

但模擬芯片里,各種參數(shù)是連續(xù)變化的,不存在“0”到“1”之間的跳變,模型就要精準(zhǔn)的描述所有變化,對精度要求會更高。尤其是射頻芯片,工作頻率高達(dá)GHz,在如此高頻的振蕩電路里,芯片襯底會產(chǎn)生很多寄生效應(yīng),各種寄生電阻、寄生電容、寄生電感都會出現(xiàn),模型要包含所有寄生效應(yīng),對半導(dǎo)體基礎(chǔ)物理理論的理解要求更高,另一方面對foundry廠工藝的一致性要求也更高。

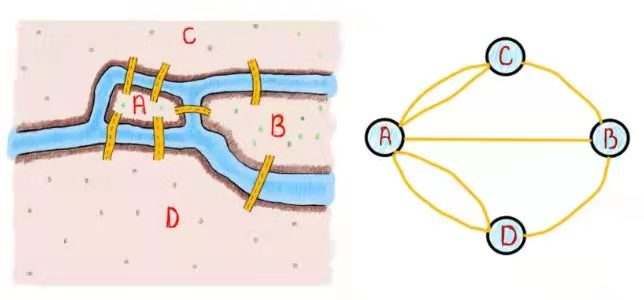

圖:射頻電路里晶體管襯底各種寄生效應(yīng)的等效電路

這也是為什么我們能有一批還不錯的數(shù)字芯片設(shè)計公司,比如海思、展銳、瑞芯微、全志……但在模擬芯片和射頻芯片領(lǐng)域,國產(chǎn)廠家與國外的差距更大,更不容易追趕。

因此,對于EDA軟件,先有量子力學(xué)、半導(dǎo)體物理、固體物理的物理知識,然后才是對物理知識的軟件化。我們在EDA上的劣勢反映的其實是在半導(dǎo)體基礎(chǔ)科學(xué)上的弱勢。

芯片設(shè)計EDA的終極考驗是——數(shù)學(xué)

器件模型的建立一般是foundry廠來完成,foundry對工藝線上制造出來的每一個器件都會建立一套數(shù)學(xué)模型,然后打包成PDK(process design kits,工藝設(shè)計工具包)發(fā)給IC設(shè)計公司使用。

IC設(shè)計公司將各種模塊的IP綜合在一起,然后EDA軟件調(diào)用PDK里的數(shù)學(xué)公式計算整個電路的綜合參數(shù)。于是,考驗芯片設(shè)計類EDA軟件的時候到了。

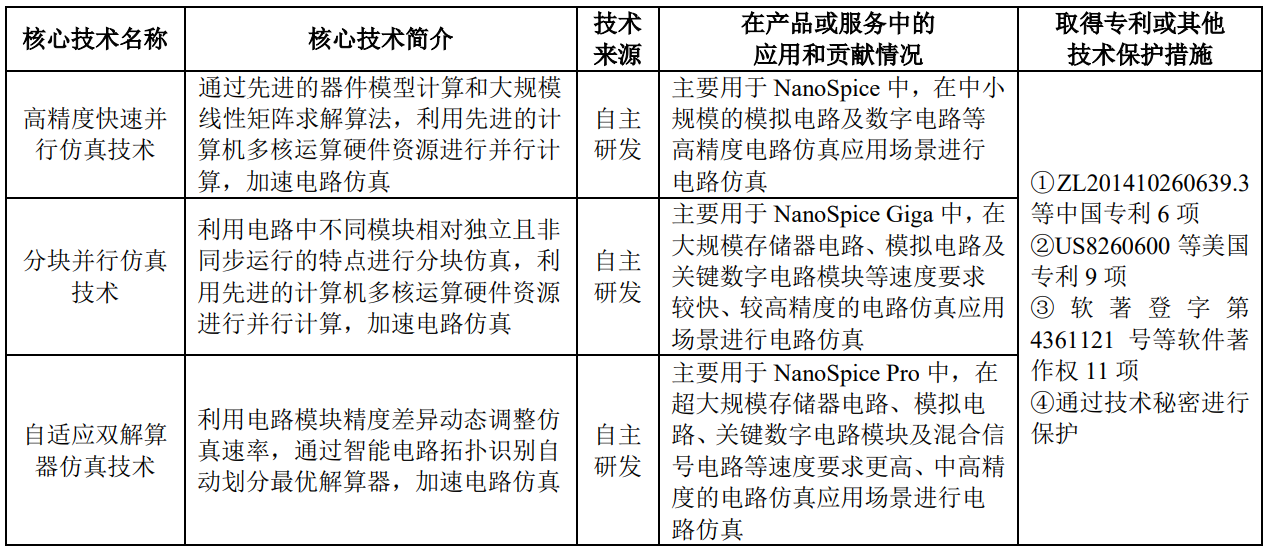

以海思麒麟9000為例,這塊5nm制程的芯片包含了153億個晶體管,一個晶體管對應(yīng)一套數(shù)學(xué)公式,要算出這么多晶體管組合在一起的整體計算結(jié)果,考驗的是EDA軟件的算法有效性和快捷性。而且EDA還要理解晶體管與晶體管之間的拓?fù)浣Y(jié)構(gòu),按照一定的區(qū)域劃分出不同的電路單元分塊計算。從下圖就能十分清晰的看出,設(shè)計類EDA軟件的核心競爭力在于數(shù)學(xué)和高效算法。

圖:芯片設(shè)計類EDA技術(shù)概覽(資料來源:概倫電子招股說明書)

再以芯片中的金屬布線為例,麒麟9000中的153億個晶體管都要用金屬導(dǎo)線連接起來,靠人去布線是不可能的,只能靠EDA軟件里的算法來實現(xiàn),還要盡可能減少金屬導(dǎo)線的總長度。畢竟金屬導(dǎo)線越長,芯片的制作成本越高。

在數(shù)學(xué)里,這個問題可以抽象成找到遍歷153億個節(jié)點的最短路徑問題,這是圖論里的一個經(jīng)典問題。其最初最簡單版本是七橋問題,即找到走完一個城市內(nèi)7座橋的最短路線。

圖:數(shù)學(xué)圖論中的七橋問題和抽象圖表示

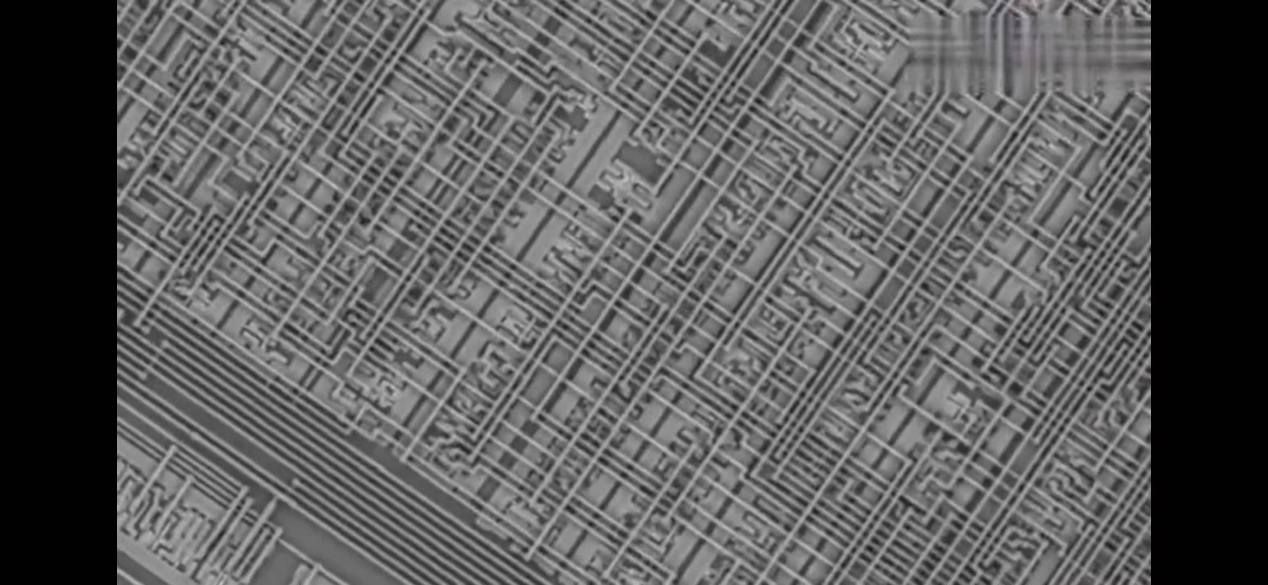

從7個節(jié)點到153億個節(jié)點,對芯片金屬布線算法的要求可見一斑。如此復(fù)雜的金屬布線靠人去檢驗也是不可能的,同樣也只能靠算法自己檢驗。IC設(shè)計師們常說的跑電路仿真,實際上軟件內(nèi)部真正運行的是各種極其復(fù)雜的數(shù)學(xué)算法。

圖:芯片內(nèi)部金屬導(dǎo)線顯微鏡放大圖

因此,與其說設(shè)計類EDA是電子工程軟件,不如說它是數(shù)學(xué)軟件。先有數(shù)學(xué)上的突破,才有EDA的易用性。否則,如果算法太慢,一塊芯片仿真的時間以天、甚至以月來計,計算結(jié)果還不一定正確,那這樣的EDA軟件哪個設(shè)計公司會用呢?

國產(chǎn)EDA軟件的成色到底如何

聊完EDA的技術(shù)難點,再來看看國產(chǎn)EDA公司的產(chǎn)品到底有多少技術(shù)含量,競爭力如何。還是以已經(jīng)上市的概倫電子為樣本。

從其招股說明書中可以知道,概倫電子的EDA產(chǎn)品主要有兩類客戶,制造類EDA工具的客戶是以臺積電、中芯國際、聯(lián)電為代表的foundry廠,用于中低頻工藝平臺、基帶芯片、存儲器芯片的器件建模,在較高工作頻率、射頻芯片的模型上還不能使用;設(shè)計類EDA工具的客戶是以三星電子、SK海力士、鎂光、長鑫存儲為代表的存儲器芯片公司。

由于存儲器芯片內(nèi)晶體管的工作模式較為簡單,只工作在0和1的狀態(tài),不涉及復(fù)雜的電路性能計算。因此,其設(shè)計類EDA軟件在一般的IC設(shè)計公司里使用較少。最更大的差距在于,EDA巨頭們將芯片IP也集成在設(shè)計軟件里,更加降低IC設(shè)計公司的設(shè)計門檻。從下圖就可以看到,新思科技Synopsys和鏗騰電子Cadence還是全球第二、第三大IP授權(quán)公司。將IP和EDA綁定,IC設(shè)計公司的使用粘性會更強,國產(chǎn)EDA要在IC設(shè)計領(lǐng)域打破國外壟斷會更難。

圖:全球10大芯片IP公司(資料來源:IPnest 2021.4)

在EDA軟件里最核心的半導(dǎo)體器件模型上,概倫電子使用的依然是BSIM、HiSIM、PSP這些外國的器件模型。其中BSIM和PSP是美國的,HiSIM是日本的。從這個角度也可以看出,EDA三大巨頭全部都創(chuàng)始于美國不是沒有原因。沒有國產(chǎn)半導(dǎo)體器件模型,對應(yīng)于芯片設(shè)計領(lǐng)域里,就是沒有一套自主開發(fā)的指令集。

綜合產(chǎn)品的各個維度,可以看到國產(chǎn)EDA軟件的差距依然巨大。概倫電子在從其招股說明書中是這么說的:“新思科技、鏗騰電子、西門子 EDA 等國際競爭對手相比,公司在產(chǎn)品種類豐富度上存在較為明顯的差距。前述國際競爭對手豐富多樣的產(chǎn)品種類可以滿足下游客戶的多方面需求,為其提供一站式采購選擇。公司產(chǎn)品種類相對國際競爭對手較少,導(dǎo)致公司在產(chǎn)品銷售協(xié)同效應(yīng)上處于劣勢,同時在公司經(jīng)營中產(chǎn)品失敗的風(fēng)險難以分散。”

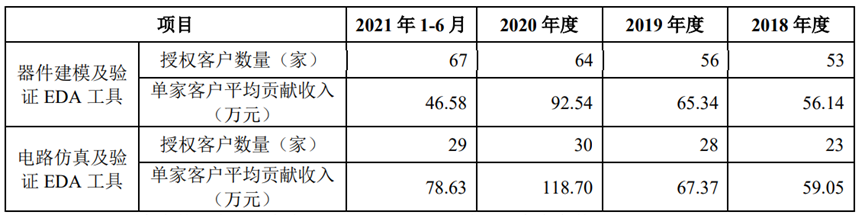

從披露出的信息來看,概倫電子對每家客戶的EDA授權(quán)使用費大致在100萬元/年。而從網(wǎng)上收集到的信息顯示,Cadence一個license費用大致在一百萬美元,價格差距6—7倍。

圖:概倫電子EDA 工具主要業(yè)務(wù)指標(biāo)(資料來源:概倫電子招股說明書)

寫在最后

華為最困難的那兩年里,任正非在很多媒體采訪中都會說這么一句話:搞芯片光砸錢不行,得砸數(shù)學(xué)家、物理學(xué)家、化學(xué)家。

明白了EDA軟件的核心技術(shù)難點就會明白,任正非的這句話絕不是心血來潮。半導(dǎo)體產(chǎn)業(yè)的物理基礎(chǔ)是量子力學(xué)、固體物理、納米材料,沒有在基礎(chǔ)理論上以十年計的長期積累,要想取得實質(zhì)性的突破是不可能的。而基礎(chǔ)理論研究更適合于高校、研究院來搞。

好消息是,國內(nèi)一批頂級大學(xué)都陸續(xù)成立了集成電路學(xué)院,如清華大學(xué)、北京大學(xué)、華中科技大學(xué)、北京理工大學(xué)、天津理工大學(xué)、中山大學(xué)……,尤其是北京大學(xué)在集成電路學(xué)院成立的新聞通稿里這樣寫道:

北京大學(xué)集成電路學(xué)院將加強與北京大學(xué)計算機、數(shù)學(xué)、物理、化學(xué)、材料等多個優(yōu)勢學(xué)科的交叉融合,著力集成微納電子、電子設(shè)計自動化、集成電路設(shè)計、集成電路制造、集成微納系統(tǒng)五個重點方向。其中隱然已經(jīng)有劍指EDA軟件的意思。

更好的消息也來了,2021年11月4日,華中科技大學(xué)的一支團隊在ICCAD2021(計算機輔助設(shè)計國際會議)芯片布局布線算法競賽中獲得第一名。

路還很遙遠(yuǎn),但至少曙光初現(xiàn)了。

編輯:ZQY 最后修改時間:2022-07-14