90%Ą─╣ż│╠ĤČ╝ø]ęŌūR(sh©¬)ĄĮĄ─Ė▀╦┘ļŖ┬ĘįO(sh©©)ėŗ(j©¼)å¢Ņ}Ż║Ą╚ķL(zh©Żng)└@ŠĆĄ─ė░Ēæ

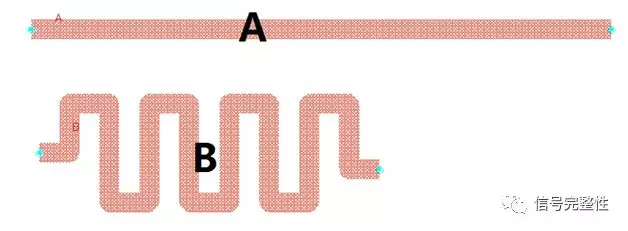

į┌╬─š┬Ą─ķ_Ņ^Ż¼Įo┤¾╝ę╠ßę╗éĆ(g©©)å¢Ņ}Ż║ ŽÓ═¼╬’└ĒķL(zh©Żng)Č╚Ą─ā╔Č╬é„▌öŠĆ╚ńŽ┬łD╦∙╩ŠŻ¼ę╗Č╬ų▒ŠĆAŻ¼ę╗Č╬└@ŠĆBŻ¼A║═B──ę╗Č╬Ą─čėĢr(sh©¬)Ģ■(hu©¼)Ė³┤¾Ż┐

ļSų°Ė▀╦┘ļŖ┬ĘĄ─░l(f©Ī)š╣Ż¼ļŖ┬ĘĄ─įO(sh©©)ėŗ(j©¼)į┌│»ų°Ė▀╦┘Ė▀├▄Č╚Ą─ĘĮŽ“░l(f©Ī)š╣ĪŻ╦┘Č╚║═├▄Č╚Ė▀┴╦Ą─įÆŻ¼Ė„ĘNą┼╠¢(h©żo)═Ļš¹ąįĪóEMIĄ─å¢Ņ}Š═│÷üĒĪŻ▀@ę▓Š═│÷¼F(xi©żn)┴╦Ė„ĘNĖ„śėĄ─įO(sh©©)ėŗ(j©¼)ę¬Ū¾ęÄ(gu©®)ätŻ¼▒╚╚ńūĶ┐╣ĘĆ(w©¦n)Č©ąįĪó═¼ĮM═¼īėĪóĄ╚ķL(zh©Żng)įO(sh©©)ėŗ(j©¼)Ą╚Ą╚ĪŻĮ±╠ņį█éāŠ═üĒėæšōę╗éĆ(g©©)ė╔Ą╚ķL(zh©Żng)Č°ę²░l(f©Ī)Ą─ę╗éĆ(g©©)įO(sh©©)ėŗ(j©¼)å¢Ņ}Ż¼╝┤└@ŠĆįO(sh©©)ėŗ(j©¼)Ż¼╚ńŽ┬łD╦∙╩ŠŻ║

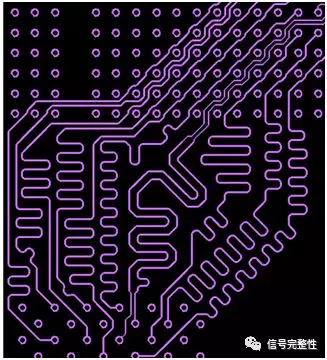

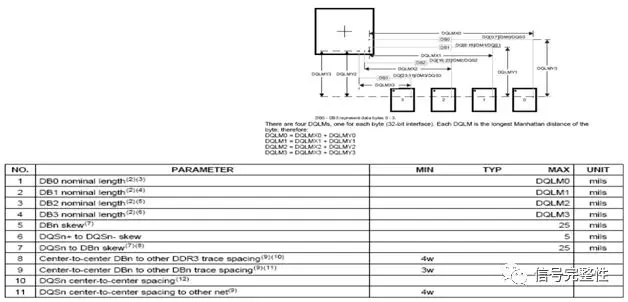

į┌įO(sh©©)ėŗ(j©¼)ųąŻ¼╠žäe╩ŪDDR3/4/5▀@ŅÉĄ─įO(sh©©)ėŗ(j©¼)Ż¼┐éĢ■(hu©¼)ėą║▄ČÓĄ─ą┼╠¢(h©żo)ŠĆ┤µį┌Ż¼├┐ę╗ĮMĄ─öĄ(sh©┤)ō■(j©┤)╗“š▀ĄžųĘ┐žųŲ├³┴Ņą┼╠¢(h©żo)ŠĆČ╝ėąę╗Č©Ą─Ą╚ķL(zh©Żng)ę¬Ū¾Ż¼╚ńŽ┬╦∙╩Š×ķ─│ąŠŲ¼╩ųāį(c©©)Ą─ę¬Ū¾Ż║

į┌įO(sh©©)ėŗ(j©¼)Ģr(sh©¬)Ż¼«ö(d©Īng)▀_(d©ó)▓╗ĄĮę¬Ū¾Ģr(sh©¬)Ż¼╣ż│╠Ĥ╩ūŽ╚ŽļĄĮĄ─Č╝╩Ū└@ŠĆŻ¼╚╗║¾▀Ć│÷¼F(xi©żn)┴╦ĘŪ│ŻČÓĄ─└@ŠĆĘĮ╩ĮĪŻ╚ńŽ┬łD╦∙╩ŠŻ©┤╦łDüĒūįIntel PDGŻ®Ż║

<img alt="└@ŠĆĘĮ╩Į"" src="http://murata.eetrend.com/sites/default/files/inline-images/%E5%9B%BE4_12.png" />▒Š╬─Š═║═┤¾╝ę┴─ę╗┴─ŲĮĢr(sh©¬)į█éā└@ŠĆĄ─ĘĮ╩ĮĄĮĄū┤µį┌ę╗ą®╩▓├┤å¢Ņ}Ż┐×ķ┴╦═Ļ│╔▀@éĆ(g©©)å¢Ņ}Ą─蹊┐Ż¼╠žęŌū÷┴╦ę╗éĆ(g©©)£y(c©©)įć░ÕŻ¼įO(sh©©)ėŗ(j©¼)┴╦蹊┐ī”(du©¼)Ž¾×ķ10inchĄ─é„▌öŠĆŻ¼ę╗Č╬ū÷ģó┐╝×ķų▒ŠĆŻ©╔ŽŻ®Ż¼ę╗Č╬×ķ└@ŠĆŻ©Ž┬Ż®Ż¼╚ńŽ┬łD╦∙╩ŠŻ║

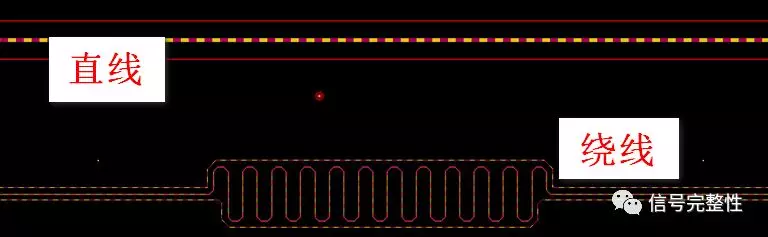

ę╗░ŃŻ¼┤¾╝ę═©│ŻČ╝Ģ■(hu©¼)šJ(r©©n)×ķŻ¼▀@śėęčĮø(j©®ng)╦ŃĄ╚ķL(zh©Żng)┴╦Ż¼Č°Ūę╩Ū═Ļ╚½Ą╚ķL(zh©Żng)ĪŻĄ½╩ŪŻ¼═©▀^£y(c©©)┴┐Ųõé„▌ö╠žąįŻ¼£y(c©©)┴┐Ą─ĮY(ji©”)╣¹╚ńŽ┬łD╦∙╩ŠŻ¼╬ęéā┐╔ęį┐┤ĄĮŻ¼Ųõ▓Ņ«É▀Ć╩Ū▓╗ąĪŻ¼ŽÓ▓Ņ┴╦12.73psŻ©╝t╔½łA╚”Ż®Ż¼Č°Ūę└@ŠĆ▒╚ų▒ŠĆé„▌ö?sh©┤)─Ė³┐ņĪ?/p>

▀@12.7psōQ╦Ń│╔╬’└ĒķL(zh©Żng)Č╚Ż¼╝s×ķ80milĪŻ80milĄ─ķL(zh©Żng)Č╚æ¬(y©®ng)įō╩ŪūīėąĮø(j©®ng)“×(y©żn)Ą─╣ż│╠Ĥćśę╗╠°Ż¼«ģŠ╣ŲĮĢr(sh©¬)ė▓╝■╣ż│╠ĤšfŻ║Įo╬ęū÷║├Ą╚ķL(zh©Żng)Ż¼š`▓Ņį┌2milĄ─Ģr(sh©¬)║“Č╝Ģ■(hu©¼)╠°Ų─_üĒ┤¾┴RĪŻ«ö(d©Īng)╚╗Ż¼╬ęéā▀@└’ū÷īŹ(sh©¬)“×(y©żn)įO(sh©©)ėŗ(j©¼)Ą─×ķ10inchŻ¼═©│Ż║▄ČÓ▓╝ŠĆČ╝ø]▀@├┤ķL(zh©Żng)Ż¼Ą½╩Ūę▓ėąę╗ą®▓╝ŠĆ┤_īŹ(sh©¬)ĘŪ│ŻķL(zh©Żng)Ą─ĪŻĄ½╩ŪŻ¼▓╗╣▄į§├┤śėŻ¼▀@éĆ(g©©)īŹ(sh©¬)“×(y©żn)Č╝ĖµįV┴╦╬ęéāŻ¼╬’└ĒĄ╚ķL(zh©Żng)Ż¼▓╗Ą╚ė┌īŹ(sh©¬)ļHįO(sh©©)ėŗ(j©¼)Š═Ą╚ķL(zh©Żng)┴╦ĪŻ▀@ę▓╩Ū×ķ╩▓├┤Ż¼Į³─ĻüĒŻ¼śI(y©©)Įńę╗ą®ÅS╔╠Č╝╠ß│½Ģr(sh©¬)ą“Ą╚ķL(zh©Żng)Ą─įŁę“ĪŻ

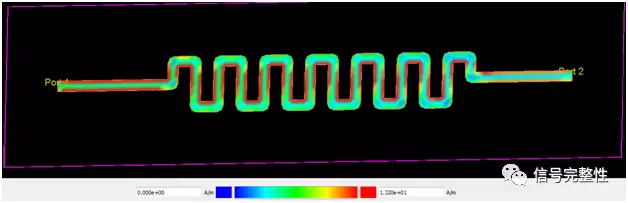

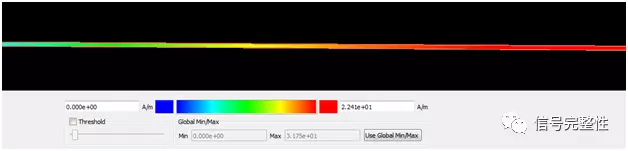

▀@╩Ū×ķ╩▓├┤─žŻ┐įŁę“Š═į┌ė┌└@ŠĆų«║¾Ż¼ė╔ė┌┌ģ─wą¦æ¬(y©®ng)║═ļŖ┤┼ł÷(ch©Żng)ą¦æ¬(y©®ng)Ż¼ą┼╠¢(h©żo)Č╝╩Ūį┌▒Ē├µ?zh©©n)„▀fĪŻ×ķ┴╦ĮŌßī┤╦¼F(xi©żn)Ž¾Ż¼į┌ADSųąįO(sh©©)ėŗ(j©¼)┴╦ę╗Č╬└@ŠĆŻ¼▀M(j©¼n)ąą┴╦ļŖ┤┼Ż©EMŻ®Ę┬šµŻ¼ĮY(ji©”)╣¹╚ńŽ┬łD╦∙╩ŠŻ║

Å─╔ŽłDųąŻ¼╬ęéā┐╔ęį┐┤ĄĮŻ¼į┌└@ŠĆĄ─ĄžĘĮŻ¼Č╝╩Ūį┌ŽÓī”(du©¼)▒╚▌^Šo±Ņ║Ž╠Äł÷(ch©Żng)ļŖ┴„├▄Č╚▒╚▌^┤¾Ż¼│╩╝t╔½Ż¼į┌╔ŽĘĮŻ©┼cé„▌öŠĆŲĮąąŻ®ęį╝░é„▌öŠĆĄ─ųąą─╠ÄŻ¼ļŖ┴„├▄Č╚▒╚▌^ąĪŻ¼│╩£\╔½Ż¼▀@Š═šf├„ą┼╠¢(h©żo)┐┐Į³▀ģčž╠Äé„▀fŻ¼▀@śėŠ═ī¦(d©Żo)ų┬┴╦ą┼╠¢(h©żo)é„▀fĄ─Ī░Ė³╝ė┐ņ╦┘Ī▒Ż¼╦∙ė├Ą─Ģr(sh©¬)ķgĖ³╔┘Ż©▒ŠüĒ┐╔ęįĮo┤¾╝ęĘ┼ę╗Åłäė(d©░ng)æB(t©żi)łDĄ─Ż¼Ą½╩Ūø]─▄ū÷║├Ż¼ėąÖC(j©®)Ģ■(hu©¼)Ą─Ģr(sh©¬)║“Ż¼į┘Įo┤¾╝ęshowę╗Ž┬Ż®ĪŻ

Č°ų▒ŠĆĄ─Ę┬šµĮY(ji©”)╣¹╚ńŽ┬łD╦∙╩ŠŻ©ķL(zh©Żng)Č╚╠½ķL(zh©Żng)Ż¼╦∙ęįų╗Įž╚Īę╗▓┐ĘųŻ®Ż║

═©▀^ęį╔ŽĄ─Ęų╬÷╝┤┐╔šf├„Ż¼ŽÓ═¼Ą─╬’└ĒķL(zh©Żng)Č╚Ż¼└@ŠĆĄ─ę╗Č╬čėĢr(sh©¬)Ė³ąĪŻ¼▀@śėŻ¼╬ęéāŠ═─▄╗ž┤Ū░├µ╠ß│÷üĒĄ─å¢Ņ}┴╦Ż¼’@╚╗╩ŪAĄ─čėĢr(sh©¬)Ė³┤¾Ż©į┌╔Ž╬─ųąę▓šf┴╦└@ŠĆĖ³┐ņŻ®ĪŻ

─Ū├┤å¢Ņ}ėųüĒ┴╦Ż¼╣ż│╠Ĥį┌įO(sh©©)ėŗ(j©¼)Ģr(sh©¬)ė÷ĄĮ▓╗Ī░Ą╚ķL(zh©Żng)Ī▒Ą─Ģr(sh©¬)║“Ż¼╚ń║╬ū÷║├įO(sh©©)ėŗ(j©¼)─žŻ┐

Ą┌ę╗Ż¼░č╬’└ĒĄ╚ķL(zh©Żng)Ą─ė^─ŅĖ─×ķĄ╚Ģr(sh©¬)Ż¼╝░▓╗╣▄└@ŠĆ▀Ć╩Ūų▒ŠĆŻ¼ąĶꬥ─╩Ūé„▌öčėĢr(sh©¬)╩Ūę╗śėĄ─ĪŻėąĄ─PCBįO(sh©©)ėŗ(j©¼)╣żŠ▀╩Ū┐╔ęį╩╣ė├Ģr(sh©¬)ķgüĒ▒Ē╩Š╬’└ĒķL(zh©Żng)Č╚Ą─Ż╗

Ą┌Č■Ż¼ėąĢr(sh©¬)ą“ĻP(gu©Īn)ŽĄĄ─ą┼╠¢(h©żo)ŠĆŻ¼į┌įO(sh©©)ėŗ(j©¼)Ģr(sh©¬)ū÷ĄĮ═¼▀M(j©¼n)═¼│÷═¼įO(sh©©)ėŗ(j©¼)Ż¼▒M┴┐£p╔┘└@ŠĆŻ╗

Ą┌╚²Ż¼╚ń╣¹─│ę╗Č╬é„▌öŠĆ┤_īŹ(sh©¬)ę¬└@ŠĆŻ¼└@ŠĆĄ─ą╬ĀŅ┤¾ę╗³c(di©Żn)Ż¼▓©┼c▓©Ą─ŠÓļx┤¾ę╗³c(di©Żn)Ż¼╗“š▀└@Ą─▒╚ų▒ŠĆĖ³ķL(zh©Żng)ę╗³c(di©Żn)Ż¼ų┴ė┌└@ČÓķL(zh©Żng)Ż¼╬ęę▓▓╗ų¬Ą└Ż¼▀Ć╩Ūšł(q©½ng)╣ż│╠Ĥ▀M(j©¼n)ąąŽ┬Ę┬šµ░╔Ż©▀@Š═╩Ū×ķ╩▓├┤ę¬▀M(j©¼n)ąą║¾Ę┬šµ┴╦Ż®ĪŻ

«ö(d©Īng)╚╗Ż¼║├Ą─ĪóĘĮ▒ŃĄ─įO(sh©©)ėŗ(j©¼)ĘĮĘ©ĘŪ│ŻČÓŻ¼┤╦×ķÆü┤uę²ė±Ż¼ŽŻ═¹┤¾╝ę░č║├Ą─ĘĮĘ©ę▓ĘųŽĒ│÷üĒŻ¼ėą┼d╚żĄ─ę▓┐╔ęį▀M(j©¼n)ę╗▓ĮĄ─┼c╬ęĮ╗┴„╠ĮėæĪŻ

ŠÄš▀ūóŻ║▀@ĘN└@ŠĆĄ─蹊┐Ż¼▓ó▓╗╩Ūšf├┐ę╗ĘN┐éŠĆįO(sh©©)ėŗ(j©¼)Č╝ąĶę¬▀@śėū÷Ż¼ī”(du©¼)ė┌ę╗ą®Ą═╦┘ą┼╠¢(h©żo)Īóī”(du©¼)Ģr(sh©¬)ą“ø]ėą╠žäeę¬Ū¾Ą─ą┼╠¢(h©żo)╗“š▀ī”(du©¼)EMIø]ėą╠ž╩Ōę¬Ū¾Ą─ĒŚ(xi©żng)─┐Ż¼╣ż│╠Ĥ┐╔ęį▓╗ė├┐╝æ]ĪŻęį╔Žā╚(n©©i)╚▌āH╣®ģó┐╝ĪŻ

ŠÄ▌ŗŻ║admin ūŅ║¾ą▐Ė─Ģr(sh©¬)ķgŻ║2018-12-24