KEILŁh(hu©ón)Š│Ž┬╚ń║╬ūī┤·┤aį┌ RAMųą▀\ąą

Ū░čį

Įø(j©®ng)│Żė÷ĄĮėą╚╦╩╣ė├KEILĢrąĶę¬īó▓┐Ęų╗“š▀╚½▓┐│╠ą“┤·┤aĘ┼ĄĮRAMųą▀\ąąĄ─å¢Ņ}Ż¼¼F(xi©żn)īóŲõ┐éĮYį┌▒Š╬─ųąĪŻ═©▀^STM32F411NucleoĄ─ę╗éĆ└²ūėüĒĮķĮBÄūĘNūī│╠ą“į┌RAMųą▀\ąąĄ─ĘĮĘ©ĪŻ

╬ęéāŽ╚Å─ToggleLED║»öĄ(sh©┤)į┌Flashųął╠(zh©¬)ąą┴┴£ńķ_╩╝ĪŻŽ┬├µ╩ŪToggleLED║»öĄ(sh©┤)║═╦³Ą─š{(di©żo)ė├ŪķørĪŻį┌main║»öĄ(sh©┤)Ą─whileŻ©1Ż®└’š{(di©żo)ė├ToggleLEDĪŻ

void ToggleLED(void)

{ HAL_GPIO_TogglePin(GPIOA, GPIO_PIN_5); /* Insert a 100ms delay */

HAL_Delay(100);

}int main(void)

{ …… /*##-3- Toggle PA05 IO in an infinite loop ######*/

while (1) { ToggleLED(); }

}

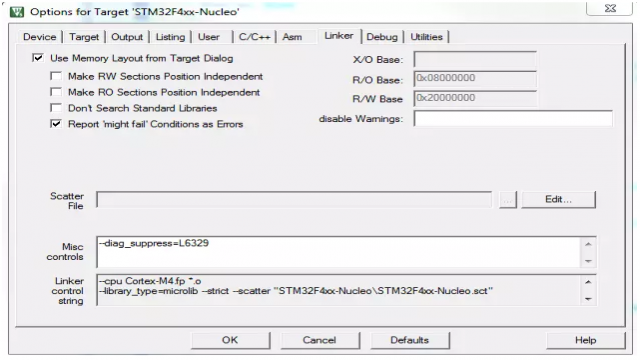

ŠÄūgŁh(hu©ón)Š│Ą─LinkerĄ─┼õų├ęŖŽ┬łDŻ║

FlashŲ╩╝ĄžųĘŻ║0x08000000

RAMŲ╩╝ĄžųĘŻ║0x20000000

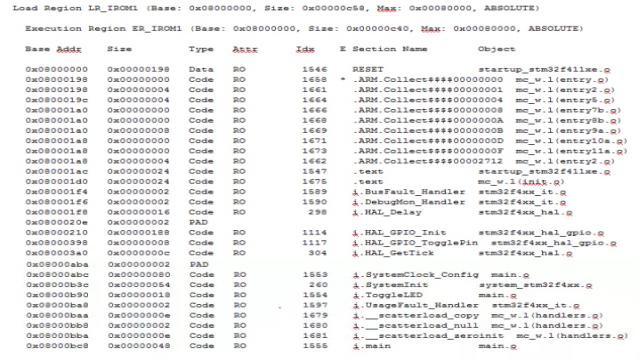

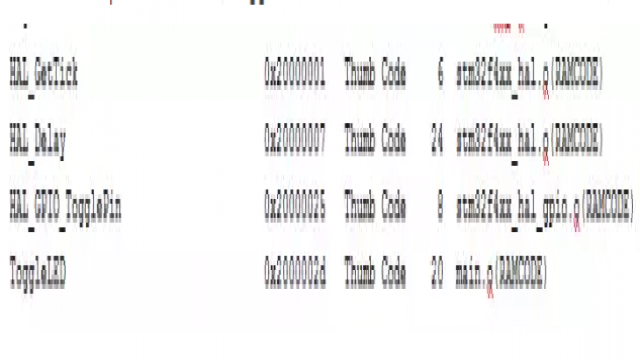

ŠÄūg║¾Å─map╬─╝■┐╔ęį┐┤ĄĮŻ¼ToggleLEDęį╝░Ųõųąš{(di©żo)ė├ĄĮĄ─HAL_GPIO_TogglePin║═HAL_Delay║»öĄ(sh©┤)Ą─ĄžųĘČ╝į┌FLASHųąĪŻ

īóĘŁ▐D(zhu©Żn)LEDĄ─│╠ą“Ę┼ĄĮSRAMųął╠(zh©¬)ąą

ĘĮĘ©ę╗Ż║═©▀^#pragma arm section code = “RAMCODE ”║═#pragma arm sectionĪŻģó┐╝Example1┤·┤aĪŻ

▀@ĘNĘĮ╩ĮŻ¼┐╔ęį═¼ĢrīóČÓéĆ║»öĄ(sh©┤)Ę┼ĄĮųĖČ©Ą─sectionĪŻŠ▀¾wĘĮĘ©╚ńŽ┬Ż║

1. ą▐Ė─.sct╬─╝■Ż¼ūįČ©┴xę╗éĆĮąū÷RAMCODEĄ─sectionŻ¼Ę┼į┌RW_IRAM1ł╠(zh©¬)ąąģ^(q©▒)ė“Ż¼ĄžųĘĘČć·0x20000000~0x20020000ĪŻ

LR_IROM1 0x08000000 0x00080000 { ; load region size_region

ER_IROM1 0x08000000 0x00080000 { ; load address = execution address

*.o (RESET, +First)

*(InRoot$$Sections)

.ANY (+RO)

} RW_IRAM1 0x20000000 0x00020000 { ; RW data

*.o(RAMCODE)

.ANY (+RW +ZI)

}

}

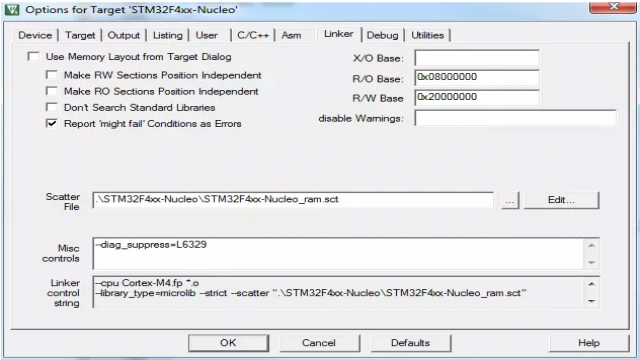

2. į┌╣ż│╠ųą╩╣ė├Ū░├µą▐Ė─Ą─.sct╬─╝■

3.ęį#pragma arm section code = “RAMCODE” ķ_Ņ^Ż¼ęį#pragma arm sectionĮY╬▓ĪŻīó╦∙ėąąĶę¬Ę┼ĄĮRAMCODE sectionĄ─║»öĄ(sh©┤)░³└©▀MüĒĪŻŠÄūgĢrŻ¼ŠÄūgŲ„Ģ■ūįäėīó▀@ą®║»öĄ(sh©┤)Ę┼ĄĮRAMCODE╦∙į┌0x20000000ķ_╩╝Ą─ģ^(q©▒)ė“ĪŻ

#pragma arm section code = "RAMCODE"

void ToggleLED(void)

{ HAL_GPIO_TogglePin(GPIOA, GPIO_PIN_5); /* Insert a 100ms delay */

HAL_Delay(100);

}void HAL_GPIO_TogglePin(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin)

{ /* Check the parameters */

assert_param(IS_GPIO_PIN(GPIO_Pin));

GPIOx->ODR ^= GPIO_Pin;

}uint32_t HAL_GetTick(void)

{ return tick;

}void HAL_Delay(__IO uint32_t Delay)

{ uint32_t tickstart = 0;

tickstart = HAL_GetTick();

while((HAL_GetTick() - tickstart) < Delay)

{

}

}

#pragma arm section

4.Å─map╬─╝■└’Ż¼┐╔ęį┐┤ĄĮ▀@╦─éĆ║»öĄ(sh©┤)Č╝ęčĮø(j©®ng)▒╗Ę┼ĄĮ┴╦SRAMųąĪŻ

ĘĮĘ©Č■Ż║═©▀^__attribute__((section(“name ”)))

į┌KEILųą┐╔ęį═©▀^__attribute__((at(address)))Ą─ĘĮ╩Įīóūā┴┐Ę┼ĄĮųĖČ©Ą─╬╗ų├ĪŻ

═©▀^__attribute__((section(“name ”)))Ą─ĘĮ╩Įīóūā┴┐╗“š▀║»öĄ(sh©┤)Ę┼ĄĮųĖČ©Ą─╬╗ų├ĪŻ

Ž┬├µ╬ęéāüĒ┐┤┐┤╚ń║╬═©▀^▀@ĘNĘĮ╩Įīó│╠ą“Ę┼ĄĮSRAMųął╠(zh©¬)ąąĪŻ

1.═¼śėŻ¼╬ęéāąĶꬹ▐Ė─.sct╬─╝■Ż¼ūįČ©┴xę╗éĆĮąū÷RAMCODEĄ─sectionŻ¼▓óį┌╣ż│╠▀xĒŚĄ─linkerĒō├µųąŻ¼▀xō±Č©┴x║├Ą─.sct╬─╝■ĪŻŻ©ęŖĘĮĘ©ę╗ųąĄ─Ą┌1Ż¼2▓ĮŻ®

LR_IROM1 0x08000000 0x00080000 { ; load region size_region ER_IROM1 0x08000000 0x00080000 { ; load address = execution address

*.o (RESET, +First)

*(InRoot$$Sections)

.ANY (+RO)

}

RW_IRAM1 0x20000000 0x00020000 { ; RW data

*.o(RAMCODE)

.ANY (+RW +ZI)

}

}

2.į┌ąĶę¬Ę┼ĄĮRAMųąĄ─║»öĄ(sh©┤)Ū░Ż¼ė├__attribute__((section("RAMCODE")))┬Ģ├„įō║»öĄ(sh©┤)Ę┼į┌RAMCODE sectionųąĪŻūóęŌŻ¼įō║»öĄ(sh©┤)ųąš{(di©żo)ė├ĄĮĄ─╦∙ėą║»öĄ(sh©┤)ę▓ę¬Ę┼ĄĮRAMCODE sectionųąĪŻ

__attribute__((section("RAMCODE")))

void ToggleLED(void)

{ HAL_GPIO_TogglePin(GPIOA, GPIO_PIN_5); /* Insert a 100ms delay */

HAL_Delay(100);

}__attribute__((section("RAMCODE")))

void HAL_GPIO_TogglePin(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin)

{ /* Check the parameters */

assert_param(IS_GPIO_PIN(GPIO_Pin));

GPIOx->ODR ^= GPIO_Pin;

}__attribute__((section("RAMCODE")))

__weak uint32_t HAL_GetTick(void)

{ return uwTick; }__attribute__((section("RAMCODE")))

__weak void HAL_Delay(__IO uint32_t Delay)

{ uint32_t tickstart = 0;

tickstart = HAL_GetTick();

while((HAL_GetTick() - tickstart) < Delay)

{ }

}

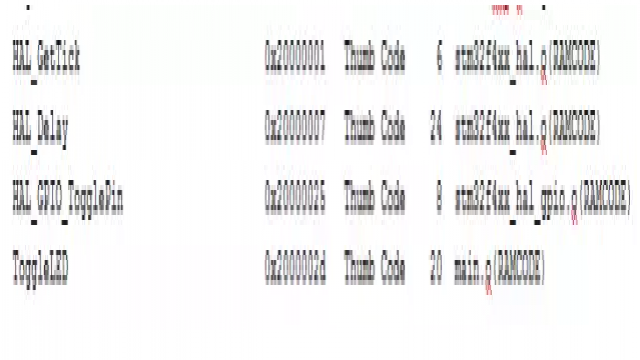

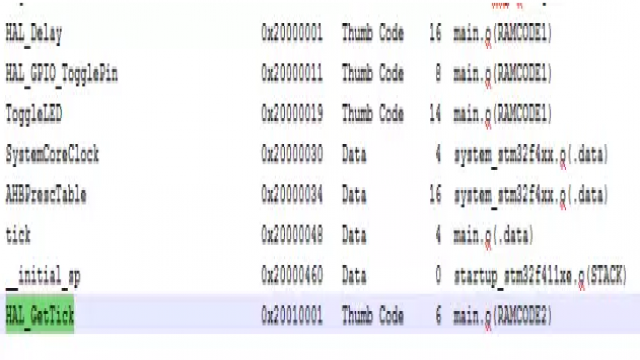

3.Å─ŠÄūg║¾Ą─map╬─╝■┐╔ęį┐┤│÷Ż¼ToggleLEDęį╝░╦³š{(di©żo)ė├ĄĮĄ─╦∙ėą║»öĄ(sh©┤)Č╝▒╗ĄĮ┴╦RAMųąĪŻ

ĘĮĘ©Č■┐╔ęįĖ▓╔wĘĮĘ©ę╗Ż¼ę▓Š═╩Ūšf╚ń╣¹─Ń═¼Ģrė├ĘĮĘ©ę╗║═ĘĮĘ©Č■ī”═¼ę╗éĆ║»öĄ(sh©┤)Ą─ł╠(zh©¬)ąąģ^(q©▒)ė“ū÷┴╦šf├„ĪŻūŅĮKŲū„ė├Ą─╩ŪĘĮĘ©Č■ĪŻ▀Ć╩Ū═©▀^╔Ž├µ╠ߥĮĄ─┤·┤aüĒšf├„ĪŻ

ą▐Ė─.sct╬─╝■ĪŻīóSRAMĘų×ķā╔éĆł╠(zh©¬)ąąģ^(q©▒)RW_IRAM1║═RW_IRAM2ĪŻSection RAMCODE1Ż¼RAMCODE2Ęųäe╬╗ė┌0x20000000ķ_╩╝Ż¼║═0x20010000ķ_╩╝Ą─ā╔éĆ64KBĄ─ģ^(q©▒)ė“ĪŻ

LR_IROM1 0x08000000 0x00080000 { ; load region size_region ER_IROM1 0x08000000 0x00080000 { ; load address = execution address

*.o (RESET, +First)

*(InRoot$$Sections)

.ANY (+RO)

}RW_IRAM1 0x20000000 0x00010000 { ; RW data

*.o(RAMCODE1)

.ANY (+RW +ZI)

}RW_IRAM2 0x20010000 0x00010000 {

*.o(RAMCODE2) }

}

2.į┌┤·┤aųą, HAL_GetTick▒╗Ę┼į┌┴╦#pragmaĄ─ū„ė├ė“ā╚(n©©i)▒╗┬Ģ├„Ę┼į┌RAMCODE1 sectionŻ¼═¼Ģrėųė├__attribute__( ( section ( "RAMCODE2" ) ) ) īóŲõĘ┼į┌RAMCODE2Ą─sectionā╚(n©©i)ĪŻ

#pragma arm section code = "RAMCODE1"

void ToggleLED(void)

{ HAL_GPIO_TogglePin(GPIOA, GPIO_PIN_5);

/* Insert a 100ms delay */

HAL_Delay(100); }void HAL_GPIO_TogglePin(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin)

{ /* Check the parameters */

assert_param(IS_GPIO_PIN(GPIO_Pin));

GPIOx->ODR ^= GPIO_Pin;

}__attribute__( ( section ( "RAMCODE2" ) ) )

uint32_t HAL_GetTick(void)

{ return tick; }void HAL_Delay(__IO uint32_t Delay)

{ uint32_t tickstart = 0;

tickstart = HAL_GetTick();

while((HAL_GetTick() - tickstart) < Delay) { }

}

#pragma arm section

3.ŠÄūg═Ļ│╔║¾Ż¼╬ęéā┐┤┐┤map╬─╝■ųąHAL_GetTick▒╗Ę┼ĄĮ┴╦──éĆsectionĪŻ

Å─map└’┐╔ęį┐┤ĄĮŻ¼ūŅĮKHAL_GetTick▒╗Ę┼į┌┴╦RAMCODE2 sectionųąĪŻ

**╚ń║╬īóš¹éĆ│╠ą“Ę┼ĄĮSRAMųął╠(zh©¬)ąą

Ū░├µĮķĮB┴╦īóę╗éĆ╗“ČÓéĆ│╠ą“Ę┼ĄĮųĖČ©ĄžųĘł╠(zh©¬)ąąĄ─ĘĮĘ©ĪŻ╚ń╣¹ąĶę¬Ę┼ĄĮųĖČ©ĄžųĘĄ─│╠ą“▒╚▌^ČÓŻ¼╬ęéā▀Ć┐╔ęįīó▀@ą®ąĶę¬Ę┼ĄĮųĖČ©ĄžųĘĄ─│╠ą“╝»ųąĘ┼ĄĮę╗éĆ╗“ÄūéĆC╬─╝■ųąŻ¼╚╗║¾į┌.sct╬─╝■ųąīó▀@ą®C╬─╝■╔·│╔Ą──┐ś╦╬─╝■Ę┼ĄĮųĖČ©ĄžųĘĪŻ

į┌▀@└’Ż¼╬ęéāīóćLįćīóš¹éĆ│╠ą“Ę┼ĄĮSRAMųął╠(zh©¬)ąąĪŻÅ═╬╗║¾│╠ą“Å─FLASHåóäėŻ¼ų«║¾īóÅ─SRAMł╠(zh©¬)ąą╦∙ėąĄ─│╠ą“ĪŻŽ┬├µ╩ŪŠ▀¾wĄ─▓Į¾EĪŻ

1.īóųąöÓŽ“┴┐▒Ē║═ųąöÓ╠Ä└Ē│╠ą“Ę┼ĄĮSRAMųą

ą┬Į©ę╗éĆstartup_stm32f411xe_ram.s╬─╝■Ż¼Ę┼ĄĮ0x20000000ķ_╩╝Ą─╬╗ų├Ż©į┌.sct╬─╝■ųąą▐Ė─Ż®ĪŻūóęŌ▀@└’╩Ūą┬Į©Ż¼Č°▓╗╩Ūų▒ĮėīóįŁüĒĄ─╬─╝■Ę┼ĄĮSRAMųąŻ¼×ķ╩▓├┤─žŻ┐┤¾╝ę┐╔ęį╦╝┐╝ę╗Ž┬ĪŻį┌startup_stm32f411xe_ram.s└’Č©┴xą┬Ą─SECTIONŻ¼Įąū÷RESET_ramŻ©▀ĆėąŲõ╦¹Ą─ą▐Ė─Ż¼šłī”ššģó┐╝┤·┤aŻ®ĪŻį┌║¾├µĄ─.sctųąīó░čRESET_ram▀@éĆsectionĘ┼ĄĮSRAMķ_╩╝Ą─╬╗ų├╔ŽŻ©ęŖĄ┌3▓ĮŻ®ĪŻ

Vector Table Mapped to Address 0 at Reset

AREA RESET_ram, DATA, READONLY

EXPORT __Vectors_ram

EXPORT __Vectors_End_ram

EXPORT __Vectors_Size_ram

__Vectors_ram DCD 0 ; Top of Stack

DCD 0 ; Reset Handler

DCD NMI_Handler ; NMI Handler

……

2.į┌SystemInitųąīóųąöÓŽ“┴┐▒ĒĄ─Ų½ęŲĄžųĘįOų├×ķ0x20000000ĪŻ╩╣─▄VECT_TAB_SRAMĪŻ

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM */

#else SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH */

#endif

3.ą▐Ė─.sct╬─╝■Ż¼īó▀\ąąĢrąĶꬥ─╦∙ėą─┐ś╦╬─╝■Č╝Ę┼ĄĮSRAMł╠(zh©¬)ąąģ^(q©▒)ųąĪŻ▀@└’ųąöÓŽ“┴┐▒Ēėą═¼śėĄ─ā╔Ę▌Ż¼ę╗Ę▌į┌0x08000000ķ_╩╝Ą─╬╗ų├Ż¼ę╗Ę▌į┌0x20000000ķ_╩╝Ą─╬╗ų├ĪŻ

LR_IROM1 0x08000000 0x00080000 { ; load region size_region

ER_IROM1 0x08000000 0x00080000 { ; load address = execution address

*.o (RESET, +First)

*(InRoot$$Sections)

.ANY (+RO)

}

RW_IRAM1 0x20000000 0x00020000 { ; RW data

*.o (RESET_ram, +First)

startup_stm32f411xe_ram.o(+RO)

main.o(+RO +RW)

stm32f4xx_it.o(+RO +RW)

stm32f4xx_hal.o(+RO +RW)

stm32f4xx_hal_gpio.o(+RO +RW)

stm32f4xx_hal_rcc.o(+RO +RW)

stm32f4xx_hal_cortex.o(+RO +RW)

.ANY (+RW +ZI)

}

}

4. ŠÄūg═Ļ│╔║¾Ż¼Å─map╬─╝■╗“š▀Ė·█Öš{(di©żo)įćĄ─ĮY╣¹Č╝┐╔ęį┐┤ĄĮĪŻŽĄĮy(t©»ng)Å═╬╗ęį║¾Ż¼Å─main║»öĄ(sh©┤)ķ_╩╝Ż¼╦∙ėąĄ─│╠ą“Č╝į┌RAMųą▀\ąą┴╦ĪŻ

┴Ē═ŌŻ¼╚ń╣¹─ŃĄ─│╠ą“ųąėąė├ĄĮARMĄūīėĄ─ÄņŻ¼┐╔ęįį┌.sct╬─╝■ųą╝ė╚ļ*armlib*(+RO)üĒīó╦∙ėąė├ĄĮĄ─Äņ╬─╝■Ę┼ĄĮSRAMųąĪŻ

ŠÄ▌ŗŻ║admin ūŅ║¾ą▐Ė─ĢrķgŻ║2019-01-03