STM32F7�Єe��������ͬ��(n��i)��MCU�Ďׂ�(g��)��ɫ

��(du��)��̎�����һ�w����ARM®Cortex®-M7��(n��i)�˵ĸ�����������STM32F7ϵ�У����źܶ��ˌ�(du��)������İ���ˡ�����STM32F7ϵ������������90nm��ˇ�������l�ʸ��_(d��)216MHz������6��(j��)����(bi��o)����ˮ�����c(di��n)��Ԫ���y(c��)ԇ��?j��n)?sh��)���_(d��)1000 CoreMarks������������ͬ�r(sh��)���ָ���Ч���cSTM32F4ϵ�й��_�߶ȼ��ݵȵȡ�

һ����v������ARM®Cortex®-M7��(n��i)�˵����������������Ƶ�̎���������x�(xi��ng)��ͨ��������

-һ��(g��)64λAXIϵ�y(t��ng)�����ӿ�

-һ��(g��)ָ��͔�(sh��)��(j��)���پ���

-64λָ��o��ϴ惦(ch��)����ITCM��

-�p32λ��(sh��)��(j��)�o��ϴ惦(ch��)����DTCM��

���^������ֻ�Ǐđ�(y��ng)���_�l(f��)�Č����BSTM32F7ϵ���Єe������ʹ��Cortex-M7��(n��i)�˵�MCU�Ďׂ�(g��)��ɫ��

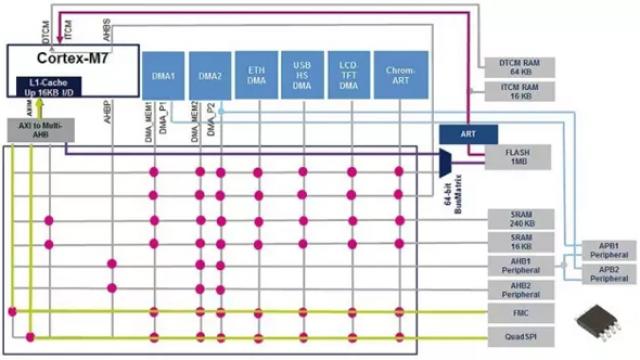

���ȣ���һ��(g��)��Ҫ��ɫ����STM32F7����ͬ�r(sh��)����ITCM�ӿں�AXI�ӿ��B�ӵ�Ƭ��(n��i)�W�棬��D1��ʾ��

�D1������ARMCortex-M7��(n��i)�˵�ϵ�y(t��ng)��(j��)оƬ�Ŀ�D

ITCM��AXI�p�ӿڵĴ���ʹ�È�(zh��)�д��a�r(sh��)�߂������`���ԡ����⣬STM32F7߀��һ��(g��)�Q�����m��(y��ng)��(sh��)�r(sh��)��������ARTAccelerator™���ă�(n��i)���W����������Ķ���(sh��)�F(xi��n)�W����ȴ���(zh��)�С�ʹ��TCM�ӿں�ART���������܌�(sh��)�F(xi��n)�c������AXI�ӿ����Ƶ����ܡ�ͬ�r(sh��)�Ñ����aҲ����(hu��)�и��پ���ʧЧ����پ���S�o(h��)�������韩��

����ART Accelerator����������_(d��)16kB��L1���棬STM32F7MCU�Ɍ�(sh��)�F(xi��n)ARM Cortex-M7��������ܡ������Ǐ�Ƭ��(n��i)�W��߀���ⲿ�惦(ch��)����(zh��)�д��a����216MHz�¾����_(d��)��1082 CoreMark/462 DMIPS��

�ڶ���(g��)�ش���ɫ���ڃ�(n��i)��SRAM�ֲ��ڲ�ͬ��ģ�K�У��Խ��̈́�(d��ng)�B(t��i)���ģ������S�ĸ���(g��)�������C(j��)ͬ�r(sh��)�L����ͬ��SRAMģ�K���ԃ�(y��u)�����������t��

�˼ܘ�(g��u)��һ��(g��)���͑�(y��ng)�Ì�(sh��)�������˙C(j��)���棬���˙C(j��)�����У����l�͈D�Δ�(sh��)��(j��)�cϵ�y(t��ng)RAM֮�g�Ă�ݔ���ͬ�r(sh��)�M(j��n)�С�

������(g��)�������ĸ�(j��)���c(di��n)��Ԫ��STM32F7ϵ����������һ��(g��)�����ܵĆλ��p���ȸ��c(di��n)��Ԫ��FPU����֧������ARM�λ��p��(sh��)��(j��)̎��ָ��͔�(sh��)��(j��)��͡�FPU����Ҫ���c(di��n)��(sh��)�W(xu��)���ȵ��S����(y��ng)�����ṩ�˃�(y��u)��(sh��)�������h(hu��n)·���ơ����l̎�������l��a�͔�(sh��)�֞V���ȡ�

��߀�Ђ�(g��)�~�⃞(y��u)��(sh��)���Ǿ��nj�ijЩ���ܵĈ�(zh��)�л�̎�����ԏ�CPU������FPU��ʹCPU���������΄�(w��)����֧���p���ȣ���˸�����ʹ���p���ȸ��c(di��n)ָ��Ļ���PC�Ĕ�(sh��)�W(xu��)ܛ����

���ģ�STM32F7 MCU�����ɫ���O(sh��)Ӌ(j��)֮һ������������ϵ�y(t��ng)�ܘ�(g��u)����ʹ�Ãɂ�(g��)��ϵ�y(t��ng)����D2��ʾ��

�D2��STM32F7�������Ŀ������

AXI-to-multi-AHB��?q��)�AXI4�f(xi��)�h�D(zhu��n)�Q��AHB-Lite�f(xi��)�h

multi-AHB������ꇹ������C(j��)֮�g���L���ٲ�

ԓ�ٲ�ʹ��ѭ�h(hu��n)�{(di��o)���㷨�������C(j��)��(du��)�ęC(j��)���L������ʹ����(g��)�������O(sh��)ͬ�r(sh��)������Ҳ�܌�(sh��)�F(xi��n)ͬ�r(sh��)�L������Ч�\(y��n)�С�

����ò�������L1���پ��档STM32F7Ƕ����ָ��͔�(sh��)��(j��)���پ��棬��(d��ng)��Ƭ�ϻ�Ƭ��惦(ch��)���xȡ���a�͔�(sh��)��(j��)�r(sh��)�ɏ��a(b��)����ȴ���B(t��i)���Ķ�������ܡ���(d��ng)Ȼ��������F(xi��n)���پ���ʧЧ���پ�������䣬�˕r(sh��)�鿴���پ��挢�o�����C��(sh��)��(j��)�Ĵ_���ԡ�

�@���Ǟ�ʲôҪ��(qi��ng)�����]ʹ��TCM�惦(ch��)�����(zh��)���P(gu��n)�I���a���惦(ch��)�P(gu��n)�I��(sh��)��(j��)��ԭ���@�ڱ�횱��C��ȫ�����đ�(y��ng)���У����늺�늙C(j��)��ͨ���������á�

���ڸ��پ��治�H������CPU�L����Ҳ����ͨ�^�������C(j��)�M(j��n)���L��������ֱ�Ӵ惦(ch��)���L����DMA�����������������Ҫܛ���S�o(h��)�������L�������惦(ch��)���r(sh��)���@Щ���C(j��)���ܕ�(hu��)�x���^�ڵĔ�(sh��)��(j��)�������µĔ�(sh��)��(j��)��CPU���پ������ѿ��á�

���˱����@��(g��)���}���_�l(f��)�߾����Ñ����a�r(sh��)��(y��ng)ԓ��ȡ���´�ʩ��

A.��(d��ng)��CPU��������C(j��)����(zh��)�Ќ�(du��)���پ�����L��֮ǰ�����]�M(j��n)�и��پ������㡣�@�Ǟ��˴_��CPU�����µĸ���(sh��)��(j��)�����ص������惦(ch��)����

B.��(d��ng)��CPU��������C(j��)��(du��)���پ��攵(sh��)��(j��)�M(j��n)���˸��º��ڌ�(du��)���پ����M(j��n)���x����֮ǰ��CPU��(y��ng)ԓʹ���پ���ʧЧ���@�Ǟ��˴_���������惦(ch��)����ֱ���xȡ��

C.�Еr(sh��)Ҳ�迼�]�o���پ����������(d��ng)���پ��_���l�����������C(j��)�L���r(sh��)������ͨ�^CPU���ò��ɾ�����Է�ֹ��(sh��)��(j��)�IJ�һ���ԡ�

������(n��i)��Ո(q��ng)�Ʋ���

STM32��Ƭ�C(j��)���ĹپW(w��ng)

�ⷨ�댧(d��o)�w/ST/STM

����admin ����ĕr(sh��)�g��2019-01-03