���ã��gӭ�M(j��n)�������зf���¿Ƽ�����˾�ٷ��W(w��ng)վ��

���ã��gӭ�M(j��n)�������зf���¿Ƽ�����˾�ٷ��W(w��ng)վ��

/**************************************************************************//** * @file main.c * @version V3.00 * $Revision: 2 $ * $Date: 15/09/02 10:03a $ * @brief Demonstrate how to set GPIO pin mode and use pin data input/output control. * @note * Copyright (C) 2013~2015 Nuvoton Technology Corp. All rights reserved. * ******************************************************************************/#include "stdio.h"#include "M451Series.h"#include "NuEdu-Basic01.h"

#define PLL_CLOCK 72000000

void SYS_Init(void){ /*---------------------------------------------------------------------------------------------------------*/ /* Init System Clock */ /*---------------------------------------------------------------------------------------------------------*/

/* Enable HIRC clock (Internal RC 22.1184MHz) */

CLK_EnableXtalRC(CLK_PWRCTL_HIRCEN_Msk);

/* Wait for HIRC clock ready */ CLK_WaitClockReady(CLK_STATUS_HIRCSTB_Msk);

/* Select HCLK clock source as HIRC and and HCLK clock divider as 1 */

CLK_SetHCLK(CLK_CLKSEL0_HCLKSEL_HIRC, CLK_CLKDIV0_HCLK(1));

/* Enable HXT clock (external XTAL 12MHz) */ CLK_EnableXtalRC(CLK_PWRCTL_HXTEN_Msk);

/* Wait for HXT clock ready */

CLK_WaitClockReady(CLK_STATUS_HXTSTB_Msk);

/* Set core clock as PLL_CLOCK from PLL */ CLK_SetCoreClock(PLL_CLOCK);

/* Enable UART module clock */

CLK_EnableModuleClock(UART0_MODULE);

/* Select UART module clock source as HXT and UART module clock divider as 1 */ CLK_SetModuleClock(UART0_MODULE, CLK_CLKSEL1_UARTSEL_HXT, CLK_CLKDIV0_UART(1));

/*---------------------------------------------------------------------------------------------------------*/

/* Init I/O Multi-function */

/*---------------------------------------------------------------------------------------------------------*/

/* Set PD multi-function pins for UART0 RXD(PD.6) and TXD(PD.1) */ SYS->GPD_MFPL &= ~(SYS_GPD_MFPL_PD6MFP_Msk | SYS_GPD_MFPL_PD1MFP_Msk); SYS->GPD_MFPL |= (SYS_GPD_MFPL_PD6MFP_UART0_RXD | SYS_GPD_MFPL_PD1MFP_UART0_TXD);

}

void UART0_Init(){ /*---------------------------------------------------------------------------------------------------------*/ /* Init UART */ /*---------------------------------------------------------------------------------------------------------*/ /* Reset UART module */ SYS_ResetModule(UART0_RST);

/* Configure UART0 and set UART0 baud rate */

UART_Open(UART0, 115200);

}

/*---------------------------------------------------------------------------------------------------------*//* Main Function *//*---------------------------------------------------------------------------------------------------------*/int32_t main(void){ uint32_t temp,temp1 = 0; /* Unlock protected registers */ SYS_UnlockReg();

/* Init System, peripheral clock and multi-function I/O */

SYS_Init();

/* Lock protected registers */ SYS_LockReg();

/* Init UART0 for printf */

UART0_Init();

printf("\nNuEdu-SDK-M451 PWM-DAC\n");

Initial_PWM_LED();

Initial_PWM_DAC();

Initial_LED();

Open_ADC_Knob();

Write_PWMDAC(1,temp1);

while(1)

{

//Get Volume Knob Data

temp = Get_ADC_PWMDAC(); //Volume Range: 0 ~ 4095

Write_LED_Bar((temp * (8 + 1) / 4096));

Write_PWMDAC(1,temp1++);

if(temp1>100)

temp1 = 0;

CLK_SysTickDelay(10000);

}

}

������PWM�����̣�������Ҫ�v�vPWM�İl(f��)��

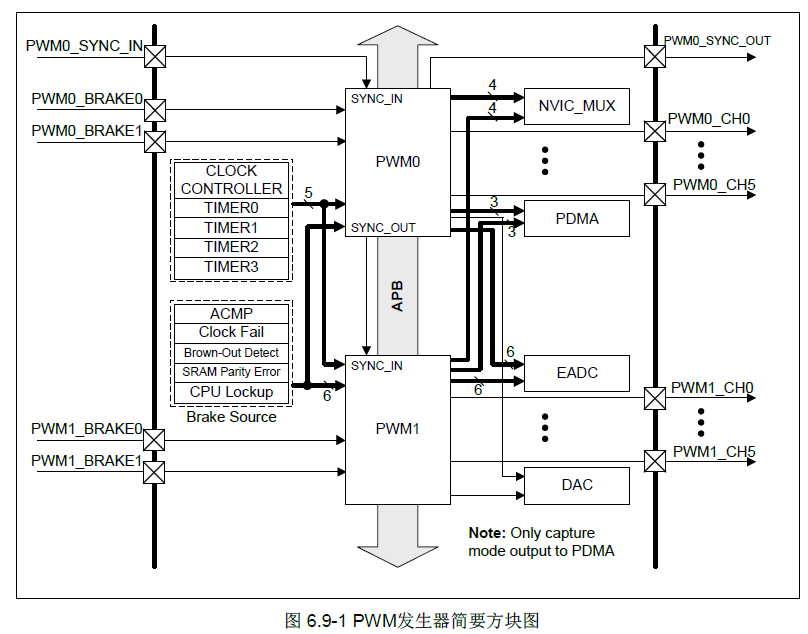

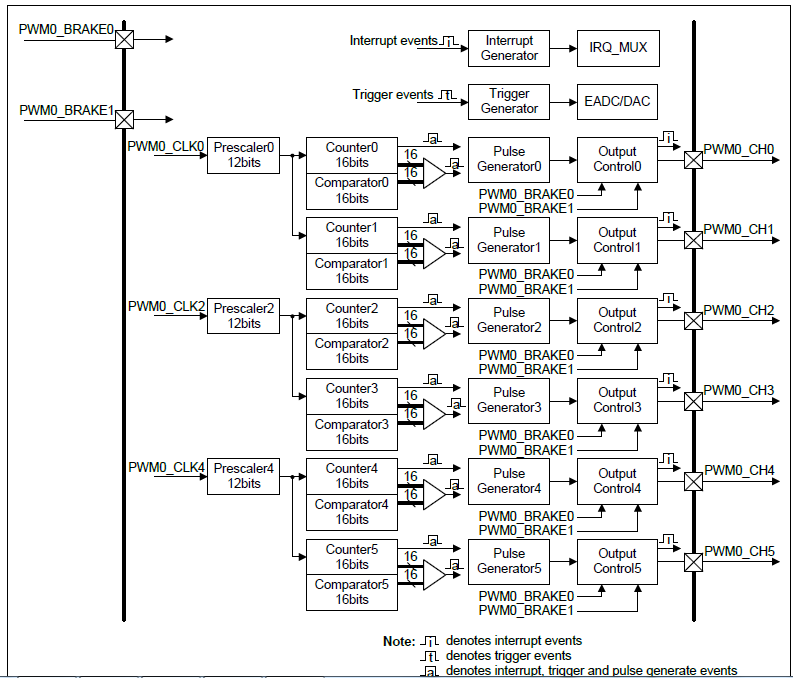

M451�ṩ�˃�·PWM�l(f��)������ÿ·PWM֧��6ͨ��PWMݔ����ݔ�벶����һ��12λ���A(y��)���l���ѕr�Դ���l��ݔ��o16λ��Ӌ��(sh��)��������߀��һ��16λ�ı��^����PWMӋ��(sh��)��֧�����ϣ����£�����Ӌ��(sh��)��ʽ��PWM�ñ��^����Ӌ��(sh��)���ı��^���a(ch��n)���¼����@Щ�¼��Á��a(ch��n)��PWM�}�_���Д࣬EADC/DAC�D(zhu��n)�Q�|�l(f��)��̖��

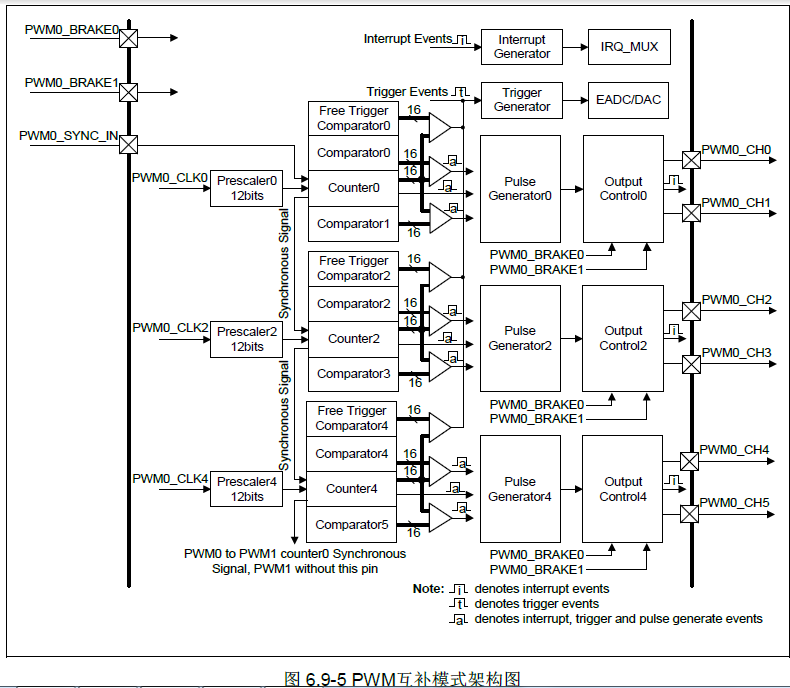

PWM�l(f��)����֧�փɷN��(bi��o)��(zh��n)PWMݔ��ģʽ������ģʽ�ͻ��a(b��)ģʽ�������ļܘ�(g��u)��ͬ����(bi��o)��(zh��n)ݔ��ģʽ���ЃɷNݔ�����ܣ��M���ܺ�ͬ�����ܡ��M���ܿ����ڪ���ģʽ�ͻ��a(b��)ģʽ��ʹ�ܡ�ͬ������ֻ���ڻ��a(b��)ģʽ�²ſ��Ա�ʹ�ܡ����a(b��)ģʽ���Ѓɂ����^���a(ch��n)�����N��12λ���^(q��)�r�g��PWM�}��������߀��һ�������|�l(f��)���^�����a(ch��n)���oEADC���|�l(f��)��̖��PWMݔ�����Ɔ�Ԫ����֧�֘O��ݔ�����������_���κ̈́x܇���ܡ�

PWMҲ֧��ݔ�벶���ܣ���(d��ng)ݔ��ͨ����������׃��������׃�����߃��߶��е���׃�r���i��PWMӋ��(sh��)����ֵ������(y��ng)�ļĴ����С�������Ҳ֧��ͨ�^PDMA�Ѳ����Ĕ�(sh��)��(j��)���Ƶ���(n��i)�档

PWM�������� 6.9.2.1

? ֧�֕r��l������_(d��)144MHz

? ֧�փɂ�PWMģ�K��ÿ��ģ�K�ṩ6��ݔ��ͨ��

? ֧�֪���ģʽ��PWMݔ��/ݔ�벶

? ֧��3�M���a(b��)ͨ���Ļ��a(b��)ģʽ

? 12λ�����ȵ����^(q��)����

? ����Ƶ�ͬ������

? ÿ�����ڃɂ����^ֵ

? ֧��12λ��1��4096���A(y��)���l

? ֧��16λ�����ȵ�PWMӋ��(sh��)��

? ���ϣ����º�����Ӌ��(sh��)�������

? ֧��one-shot���Ԅ��b�dӋ��(sh��)������ģʽ

? ֧�ֽM����

? ֧��ͬ������

? ÿ��PWM���_֧�����ι��ܺ����B(t��i)ʹ��

? ֧�քx܇����

? �x܇Դ���Թ��_��ģ�M���^����ϵ�y(t��ng)��ȫ�¼����r犹��ϡ�SRAM��żУ��e�`��Ƿ���O(ji��n)�y��CPU�iס��

? �x܇Դ���_���V����

? ͨ�^߅���z�y�x܇Դ�����Ƅx܇��B(t��i)ֱ���x܇�Д����

? �x܇�l��������ƽ�z�y�x܇Դ�Ԅӻ֏�(f��)����

? ֧�������¼��Дࣺ

? PWMӋ��(sh��)��ֵ�� 0������ֵ����^ֵ

? �l(f��)���x܇�l��

? ֧�������¼��|�l(f��)EADC/DAC ��

? PWMӋ��(sh��)��ֵ��0������ֵ����^ֵ

? PWM Ӌ��(sh��)��ƥ�������|�l(f��)���^�����^ֵ(�HEADC)

���������� 6.9.2.2

? ֧��12��16λ�����ȵ�ݔ�벶ͨ��

? ֧������/�½��ز��l��

? ֧��ݔ������/�½��� ���Д�

? ֧��Ӌ��(sh��)�����d�x헵�����/�½��� ��

? ֧��PWM ������ͨ��PDMA��(sh��)��(j��)���ƹ���

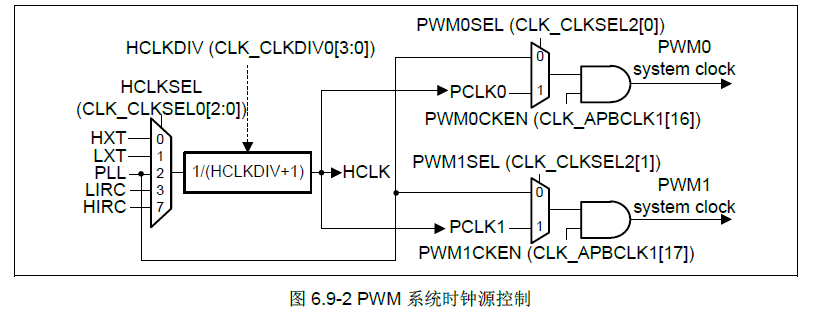

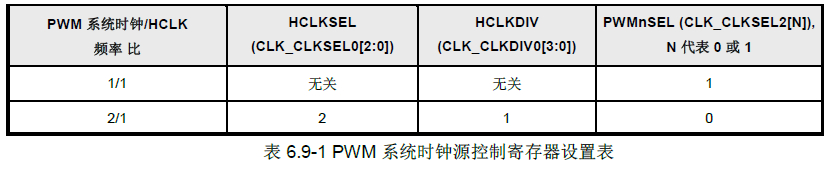

PWMϵ�y(t��ng)�r犿����O(sh��)����ڻ�ɱ���HCLK�l�ʣ� �D 6.9-2, �Ĵ����O(sh��)�ü�(x��)��(ji��)Ո������ 6.9-1.

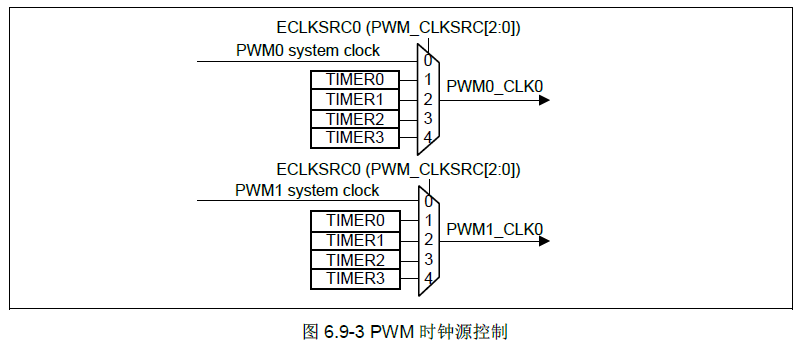

ÿ��PWM�l(f��)����������ݔ��r�Դ��ÿ���r�Դ���ԏ�ϵ�y(t��ng)�r犻���4�M���r���|�l(f��)PWMݔ�����D

6.9-3��PWM_CLK0�O(sh��)��ECLKSRC0 (PWM_CLKSRC[2:0])��PWM_CLK2�O(sh��)��ECLKSRC2

(PWM_CLKSRC[10:8])��PWM_CLK4�O(sh��)��ECLKSRC4 (PWM_CLKSRC[18:16])

�D 6.9-4 �͈D 6.9-5��ʾPWM����ģʽ�ͻ��a(b��)ģʽ�ļܘ�(g��u)�����ܪ���ģʽ߀�DZ��^ģʽ��һ��ͨ��

�M(PWM_CH0 ��PWM_CH1, PWM_CH2 �� PWM_CH3, PWM_CH4 �� PWM_CH5)Ӌ��(sh��)��������

ͬ�ĕr�Դ���A(y��)���l����(d��ng)Ӌ��(sh��)����ֵ����0��PERIOD(PWM_PERIODn[15:0])����^��ֵ�����a(ch��n)��

�¼����@Щ�¼�ͨ�^����(y��ng)�İl(f��)�������a(ch��n)��PWM�}�_���Д���̖��EADC/DAC���D(zhu��n)�Q�|�l(f��)��̖��ݔ

���������Á���׃PWM�}�_ݔ����B(t��i)�ġ�ݔ�����ƵĄx܇����Ҳ�ܮa(ch��n)���Д��¼����ڻ��a(b��)ģʽ��

ͬ��������Ч��ż��(sh��)ͨ�����攵(sh��)ͨ�����^���a(ch��n)���¼��������|�l(f��)���^���¼�ֻ���ڮa(ch��n)���|�l(f��)EADC

��̖��

#include <stdio.h> #include "M451Series.h" #include "NuEdu-Basic01_PWMDAC.h" void Write_PWMDAC(unsigned char Enable, unsigned char ch0_dut) { /* set PWMB channel 0 output configuration */ PWM_ConfigOutputChannel(PWM1, 4, 1000, ch0_dut); // Start PWM COUNT PWM_Start(PWM1, 1 << 4); if(Enable == 0) /* Enable PWM Output path for PWMB channel 0 */ PWM_DisableOutput(PWM1, 1 << 4); else /* Diable PWM Output path for PWMB channel 0 */ PWM_EnableOutput(PWM1, 1 << 4); } void Initial_PWM_DAC(void) { GPIO_SetMode(PC, BIT13, GPIO_MODE_INPUT); //avoid to pwm dac out SYS->GPC_MFPH &= ~SYS_GPC_MFPH_PC13MFP_Msk ; SYS->GPC_MFPH |= SYS_GPC_MFPH_PC13MFP_PWM1_CH4; /* Enable PWM module clock */ CLK_EnableModuleClock(PWM1_MODULE); /* Select PWM module clock source */ CLK_SetModuleClock(PWM1_MODULE, CLK_CLKSEL2_PWM1SEL_PCLK1, 0); /* Reset PWM1 channel 0~5 */ SYS_ResetModule(PWM1_RST); }

/**************************************************************************//** * @file NuEdu-NuEdu-Basic01_RGBLED.c * @version V1.00 * $Revision: 5 $ * $Date: 15/09/02 10:02a $ * @brief NuEdu-Basic01_RGBLED driver source file for NuEdu-SDK-M451 * * @note * Copyright (C) 2014~2015 Nuvoton Technology Corp. All rights reserved. *****************************************************************************/ #include <stdio.h> #include "M451Series.h" #include "NuEdu-Basic01_RGBLED.h" /** @addtogroup M451_Library M451 Library @{ */ /** @addtogroup NuEdu-SDK-M451_Basic01 M451_Basic01 Library @{ */ /** @addtogroup M451_Basic01_FUNCTIONS RGB LED Functions @{ */ /** * @brief Set multi-function pins for PWM1 channel 0,1,2 * @return None */ void Initial_PWM_LED(void) { /* Set PC9~PC11 multi-function pins for PWM1 Channel0~2 */ SYS->GPC_MFPH &= ~(SYS_GPC_MFPH_PC9MFP_Msk | SYS_GPC_MFPH_PC10MFP_Msk | SYS_GPC_MFPH_PC11MFP_Msk); SYS->GPC_MFPH |= SYS_GPC_MFPH_PC9MFP_PWM1_CH0 | SYS_GPC_MFPH_PC10MFP_PWM1_CH1 | SYS_GPC_MFPH_PC11MFP_PWM1_CH2; /* Enable PWM module clock */ CLK_EnableModuleClock(PWM1_MODULE); /* Select PWM module clock source */ CLK_SetModuleClock(PWM1_MODULE, CLK_CLKSEL2_PWM1SEL_PCLK1, 0); /* Reset PWM1 channel 0~5 */ SYS_ResetModule(PWM1_RST); } /** * @brief Set PWM clock enable and HCLK as PWM clock source, * * @param[in] ch Channel numbers that will be enabled. * * @param[in] ch0_fre Channel 0 frequency. * * @param[in] ch0_dut Channel 0 duty. * * @param[in] ch1_fre Channel 1 frequency. * * @param[in] ch1_dut Channel 1 duty. * * @param[in] ch2_fre Channel 2 frequency. * * @param[in] ch2_dut Channel 2 duty. * * @return None */ void PWM_LED(unsigned char ch, unsigned int ch0_fre, unsigned int ch0_dut, unsigned int ch1_fre, unsigned int ch1_dut, unsigned int ch2_fre, unsigned int ch2_dut) { /* set PWMA channel 1 output configuration */ PWM_ConfigOutputChannel(PWM1, 0, ch0_fre, ch0_dut); PWM_ConfigOutputChannel(PWM1, 1, ch1_fre, ch1_dut); PWM_ConfigOutputChannel(PWM1, 2, ch2_fre, ch2_dut); /* Enable PWM Output path for PWMA channel 0 */ PWM_EnableOutput(PWM1, ch); // Start PWM_Start(PWM1, ch); } /*@}*/ /* end of group M451_Basic01_FUNCTIONS */ /*@}*/ /* end of group NuEdu-SDK-M451_Basic01 */ /*@}*/ /* end of group M451_Library */ /*** (C) COPYRIGHT 2013~2015 Nuvoton Technology Corp. **/

uint32_t PWM_ConfigCaptureChannel(PWM_T *pwm, uint32_t u32ChannelNum, uint32_t u32UnitTimeNsec, uint32_t u32CaptureEdge) { uint32_t u32Src; uint32_t u32PWMClockSrc; uint32_t u32NearestUnitTimeNsec; uint16_t u16Prescale = 1, u16CNR = 0xFFFF; if(pwm == PWM0) u32Src = CLK->CLKSEL2 & CLK_CLKSEL2_PWM0SEL_Msk; else//(pwm == PWM1) u32Src = CLK->CLKSEL2 & CLK_CLKSEL2_PWM1SEL_Msk; if(u32Src == 0) { //clock source is from PLL clock u32PWMClockSrc = CLK_GetPLLClockFreq(); } else { //clock source is from PCLK SystemCoreClockUpdate(); u32PWMClockSrc = SystemCoreClock; } u32PWMClockSrc /= 1000; for(u16Prescale = 1; u16Prescale <= 0x1000; u16Prescale++) { u32NearestUnitTimeNsec = (1000000 * u16Prescale) / u32PWMClockSrc; if(u32NearestUnitTimeNsec < u32UnitTimeNsec) { if(u16Prescale == 0x1000) //limit to the maximum unit time(nano second) break; if(!((1000000 * (u16Prescale + 1) > (u32NearestUnitTimeNsec * u32PWMClockSrc)))) break; continue; } break; } // convert to real register value // every two channels share a prescaler PWM_SET_PRESCALER(pwm, u32ChannelNum, --u16Prescale); // set PWM to down count type(edge aligned) (pwm)->CTL1 = ((pwm)->CTL1 & ~(PWM_CTL1_CNTTYPE0_Msk << (2 * u32ChannelNum))) | (1UL << (2 * u32ChannelNum)); // set PWM to auto-reload mode (pwm)->CTL1 &= ~(PWM_CTL1_CNTMODE0_Msk << u32ChannelNum); PWM_SET_CNR(pwm, u32ChannelNum, u16CNR); return (u32NearestUnitTimeNsec); } /** * @brief This function Configure PWM generator and get the nearest frequency in edge aligned auto-reload mode * @param[in] pwm The pointer of the specified PWM module * - PWM0 : PWM Group 0 * - PWM1 : PWM Group 1 * @param[in] u32ChannelNum PWM channel number. Valid values are between 0~5 * @param[in] u32Frequency Target generator frequency * @param[in] u32DutyCycle Target generator duty cycle percentage. Valid range are between 0 ~ 100. 10 means 10%, 20 means 20%... * @return Nearest frequency clock in nano second * @note Since every two channels, (0 & 1), (2 & 3), shares a prescaler. Call this API to configure PWM frequency may affect * existing frequency of other channel. */ uint32_t PWM_ConfigOutputChannel(PWM_T *pwm, uint32_t u32ChannelNum, uint32_t u32Frequency, uint32_t u32DutyCycle) { uint32_t u32Src; uint32_t u32PWMClockSrc; uint32_t i; uint16_t u16Prescale = 1, u16CNR = 0xFFFF; if(pwm == PWM0) u32Src = CLK->CLKSEL2 & CLK_CLKSEL2_PWM0SEL_Msk; else//(pwm == PWM1) u32Src = CLK->CLKSEL2 & CLK_CLKSEL2_PWM1SEL_Msk; if(u32Src == 0) { //clock source is from PLL clock u32PWMClockSrc = CLK_GetPLLClockFreq(); } else { //clock source is from PCLK SystemCoreClockUpdate(); u32PWMClockSrc = SystemCoreClock; } for(u16Prescale = 1; u16Prescale < 0xFFF; u16Prescale++)//prescale could be 0~0xFFF { i = (u32PWMClockSrc / u32Frequency) / u16Prescale; // If target value is larger than CNR, need to use a larger prescaler if(i > (0x10000)) continue; u16CNR = i; break; } // Store return value here 'cos we're gonna change u16Prescale & u16CNR to the real value to fill into register i = u32PWMClockSrc / (u16Prescale * u16CNR); // convert to real register value // every two channels share a prescaler PWM_SET_PRESCALER(pwm, u32ChannelNum, --u16Prescale); // set PWM to down count type(edge aligned) (pwm)->CTL1 = ((pwm)->CTL1 & ~(PWM_CTL1_CNTTYPE0_Msk << (2 * u32ChannelNum))) | (1UL << (2 * u32ChannelNum)); // set PWM to auto-reload mode (pwm)->CTL1 &= ~(PWM_CTL1_CNTMODE0_Msk << u32ChannelNum); PWM_SET_CNR(pwm, u32ChannelNum, --u16CNR); if(u32DutyCycle) { PWM_SET_CMR(pwm, u32ChannelNum, u32DutyCycle * (u16CNR + 1) / 100 - 1); (pwm)->WGCTL0 &= ~((PWM_WGCTL0_PRDPCTL0_Msk | PWM_WGCTL0_ZPCTL0_Msk) << (u32ChannelNum * 2)); (pwm)->WGCTL0 |= (PWM_OUTPUT_LOW << (u32ChannelNum * 2 + PWM_WGCTL0_PRDPCTL0_Pos)); (pwm)->WGCTL1 &= ~((PWM_WGCTL1_CMPDCTL0_Msk | PWM_WGCTL1_CMPUCTL0_Msk) << (u32ChannelNum * 2)); (pwm)->WGCTL1 |= (PWM_OUTPUT_HIGH << (u32ChannelNum * 2 + PWM_WGCTL1_CMPDCTL0_Pos)); } else { PWM_SET_CMR(pwm, u32ChannelNum, 0); (pwm)->WGCTL0 &= ~((PWM_WGCTL0_PRDPCTL0_Msk | PWM_WGCTL0_ZPCTL0_Msk) << (u32ChannelNum * 2)); (pwm)->WGCTL0 |= (PWM_OUTPUT_LOW << (u32ChannelNum * 2 + PWM_WGCTL0_ZPCTL0_Pos)); (pwm)->WGCTL1 &= ~((PWM_WGCTL1_CMPDCTL0_Msk | PWM_WGCTL1_CMPUCTL0_Msk) << (u32ChannelNum * 2)); (pwm)->WGCTL1 |= (PWM_OUTPUT_HIGH << (u32ChannelNum * 2 + PWM_WGCTL1_CMPDCTL0_Pos)); } return(i); } /** * @brief Start PWM module * @param[in] pwm The pointer of the specified PWM module * - PWM0 : PWM Group 0 * - PWM1 : PWM Group 1 * @param[in] u32ChannelMask Combination of enabled channels. Each bit corresponds to a channel. * Bit 0 is channel 0, bit 1 is channel 1... * @return None * @details This function is used to start PWM module. */ void PWM_Start(PWM_T *pwm, uint32_t u32ChannelMask) { (pwm)->CNTEN |= u32ChannelMask; }

PWMԭ��

�����S����Ӽ��g(sh��)�İl(f��)չ�����F(xi��n)�˶�NPWM���g(sh��)�����а�������늉�����PWM���}��PWM�����S�C(j��)PWM��SPWM������늉�����PWM�ȣ�����懚�늳����ܳ�����в��õ��}��PWM�������ǰ�ÿһ�}�_���Ⱦ���ȵ��}�_������PWM���Σ�ͨ�^��׃�}�_�е����ڿ����{(di��o)�l����׃�}�_�Č��Ȼ�ռ�ձȿ����{(di��o)���������m��(d��ng)���Ʒ�������ʹ늉��c�l�ʅf(xi��)�{(di��o)׃��������ͨ�^�{(di��o)��PWM�����ڡ�PWM��ռ�ձȶ��_(d��)�����Ƴ�������Ŀ�ġ� ����

����ģ�M��̖��ֵ�����B�m(x��)׃������r�g�ͷ��ȵķֱ��ʶ��]�����ơ�9V늳ؾ���һ�Nģ�M�������������ݔ��늉��������_�ص���9V�������S�r�g�l(f��)��׃��������ȡ�κΌ���(sh��)ֵ���c����ƣ���늳����յ����Ҳ������һ�M���ܵ�ȡֵ����֮��(n��i)��ģ�M��̖�c��(sh��)����̖�ą^(q��)�e���ں��ߵ�ȡֵͨ��ֻ�܌����A(y��)�ȴ_���Ŀ���ȡֵ����֮��(n��i)��������{0V, 5V}�@һ������ȡֵ�� ����

����ģ�M늉��������ֱ���Á��M(j��n)�п��ƣ��猦��܇�����C(j��)�������M(j��n)�п��ơ��ں��ε�ģ�M�����C(j��)�У��������o���B�ӵ�һ����׃��衣�Q�����o�r�����ֵ׃���׃С������(j��ng)�@���������Ҳ�S֮���ӻ�p�٣��Ķ���׃���(q��)�ӓP(y��ng)�������ֵ��ʹ��������(y��ng)׃���׃С���c�����C(j��)һ�ӣ�ģ�M�·��ݔ���cݔ��ɾ��Ա����� ����

�����M��ģ�M���ƿ���������ֱ�^�����Σ������������Ƿdz���(j��ng)��(j��)����еġ�����һ�c���ǣ�ģ�M�·�����S�r�gƯ�ƣ�����y���{(di��o)��(ji��)���܉��Q�@�����}�ľ���ģ�M�·���ܷdz�������(����ʽ�ļ�ͥ���w�O(sh��)��)�Ͱ��F��ģ�M�·߀�п��܇�(y��n)�ذl(f��)�ᣬ�书�������ڹ���Ԫ���ɶ�늉��c����ij˷e�����ȡ�ģ�M�·߀���܌��������У��κΔ_�ӻ������϶�����׃���ֵ�Ĵ�С�� ����

����ͨ�^�Ԕ�(sh��)�ַ�ʽ����ģ�M�·�����Դ���Ƚ���ϵ�y(t��ng)�ijɱ����ġ����⣬�S����������DSP�ѽ�(j��ng)��оƬ�ϰ�����PWM���������@ʹ��(sh��)�ֿ��ƵČ��F(xi��n)׃�ø��������ˡ�

���a(b��)����˼���Ǯ�(d��ng)pwm1�Ǹ��ƽ�r��pwm2�ǵ��ƽ�����pwm1�ǵ��ƽ�rpwm2�Ǹ��ƽ����֮��pwm1��pwm2����ͬ��׃��׃�ͣ����Dz�һ�ӵġ� һ���@�ӵ�pwmݔ�����ڿ����Ƀɂ��_�P(gu��n)�ܽM�ɵ����Դ�͵�֮�g�Ęɂ�ͬ�r��ͨ��Ԓ����(d��o)��۶�·�Դ�͵�������������a(b��)�IJ��οɱ���ͬ�r��(d��o)ͨ��

�_�P(gu��n)�ܿɲ���˲�g�����_�����P(gu��n)�]�ġ� �e�������·�У��]�����^(q��)��Ԓ���п������ֱͨ��·�� ��ʹ��boost �·�������������ռ�ձȣ�Ҳ���O(sh��)Ӌ�����^(q��)�r�g���� ���w�O(sh��)�ö���Ҫ�������_�P(gu��n)�ܵ��_�����P(gu��n)�]�����t�r�g��

���ε��f����������5V�Դ��Ҫ����һ�_�������ȣ���һ�����y(t��ng)�k�������Ǵ�(li��n)һ�����{(di��o)�������׃��裬�������Ⱦ͕���׃�� ߀��һ���k��������PWM�{(di��o)��(ji��)�����ô�(li��n)��裬���Ǵ�(li��n)һ���_�P(gu��n)�����O(sh��)��1���(n��i)����0.5��ĕr�g�_�P(gu��n)�Ǵ��_�ģ�0.5���P(gu��n)�]����ô������0.5�룬��0.5�롣�@�ӳ��m(x��)��ȥ�����͕��W�q��������l���{(di��o)��һ�c��������1������0.5�����_��0.5�����磬��ô�����W�q�l�ʾͺܸߡ��҂�֪�����W�q�l�ʳ��^һ��ֵ�����۾͕����X���������ԣ��@�r�㿴���������W�q��ֻ������������ֻ��ԭ����һ�롣 ͬ�������1�����(n��i)��0.1�����_��0.9����磬��ô���������Ⱦ�ֻ��ԭ����10��֮һ�� �@����PWM�Ļ���ԭ�������I(y��)���f���ٶ�һ�¾ͺܶ࣬���f��Ҳ�����I(y��)�����ǵ��������@ô���Σ����wPWM߀�֎N�����ā��f�����DZ���һ����늉��������׃������׃һ�����ڃ�(n��i)�Č�(d��o)ͨ���P(gu��n)���r�g���@�ӵ�Ч�ڱ���(d��o)ͨ������׃늉��������С�� �@�ӵ�PWM���Ʒ�ʽ���ڔ�(sh��)�ֿ����·�ϑ�(y��ng)�úܷ��㡣�����Xȥ����һ�����{(di��o)����DZ��^���y�ģ��������{(di��o)���߀��ģ�M�·���еIJ���(w��n)�����}��

�ߴa�P(gu��n)ע�҂�

�]�䣺ivy@yingtexin.net

��ַ�����������A�^(q��)���νֵ����δ��973�f�����S��(chu��ng)�I(y��)�@A��2��A09