���ã��gӭ�M(j��n)�������зf���¿Ƽ�����˾�ٷ��W(w��ng)վ��

���ã��gӭ�M(j��n)�������зf���¿Ƽ�����˾�ٷ��W(w��ng)վ��

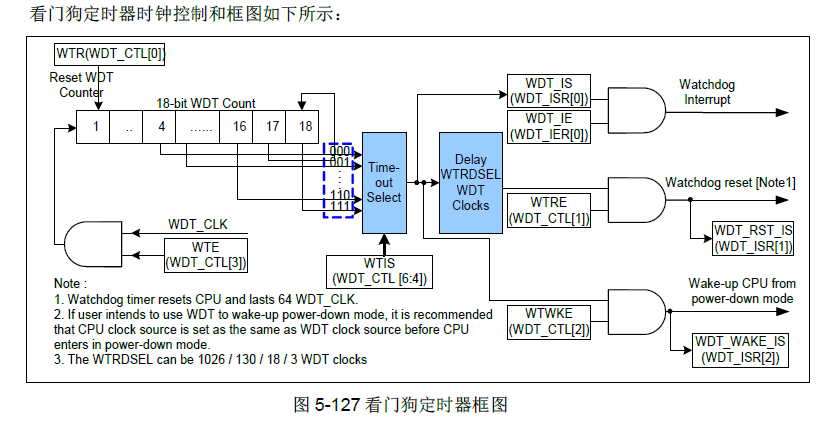

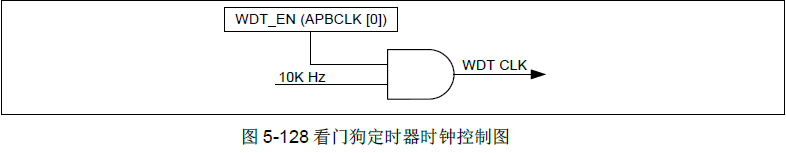

���T�����r������;����ܛ�������}�r��(zh��)��ϵ�y(t��ng)��(f��)λ���ܣ��@���Է�ֹϵ�y(t��ng)�o���ڵؒ��𡣳���֮�⣬���T�����r��߀֧��CPU �ĵ��ģʽ���ѵĹ��ܡ����T�����r������һ��18 λ�������\(y��n)��Ӌ(j��)��(sh��)�������r����g���ɾ��̡�

����

18-λ�����\(y��n)��WDT Ӌ(j��)��(sh��)�����ڿ��T�����r�����r�g����

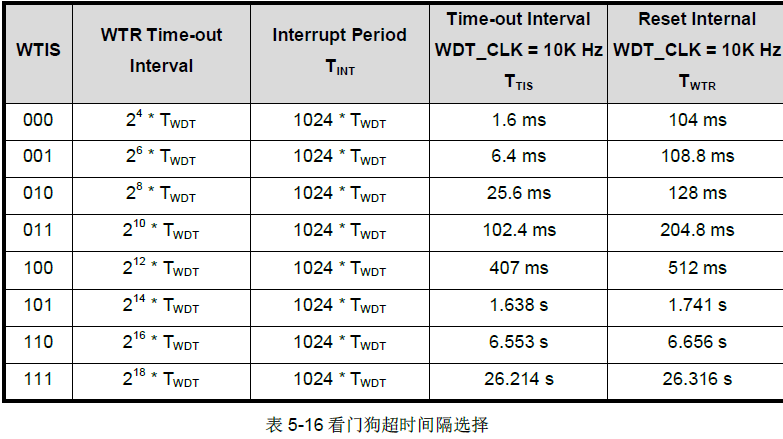

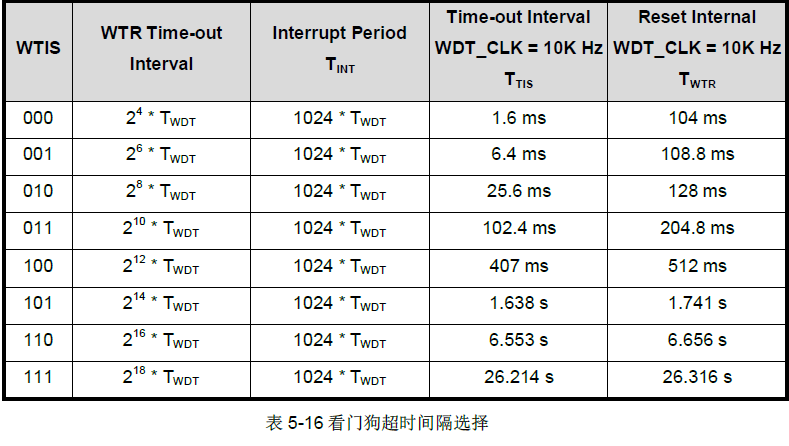

���x��ij��r�g�� (2^4 ~ 2^18)�����r�g����104 ms ~ 26.316 s (���WDT_CLK = 10 kHz)��

��(f��)��� = (1 / 10 kHz) * 63�����WDT_CLK = 10 kHz

����(y��ng)�ļĴ������@��

#define WDT_BASE (APB1PERIPH_BASE + 0x04000) ///< WDT register base address #define APB1PERIPH_BASE ((uint32_t)0x40000000) ///< APB1 base address #define CLK_APBCLK_WDT_EN_Pos (0) /*!< CLK_T::APBCLK: WDT_EN Position */ #define CLK_APBCLK_WDT_EN_Msk (0x1ul << CLK_APBCLK_WDT_EN_Pos) /*!< CLK_T::APBCLK: WDT_EN Mask

typedef struct { /** * PWRCTL * =================================================================================================== * Offset: 0x00 System Power Down Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[0] |HXT_EN |HXT Control * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |The bit default value is set by flash controller user configuration register config0 [26]. * | | |0 = Disabled. * | | |1 = Enabled. * | | |HXT is disabled by default. * |[1] |LXT_EN |LXT Control * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |0 = Disabled. * | | |1 = Enabled. * | | |LXT is disabled by default. * |[2] |HIRC_EN |HIRC Control * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |0 = Disabled. * | | |1 = Enabled. * | | |HIRC is enabled by default. * |[3] |LIRC_EN |LIRC Control * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |0 = Disabled. * | | |1 = Enabled. * | | |LIRC is enabled by default. * |[4] |WK_DLY |Wake-Up Delay Counter Enable * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |When chip wakes up from Power-down mode, the clock control will delay 4096 clock cycles to wait HXT stable or 16 clock cycles to wait HIRC stable. * | | |0 = Delay clock cycle Disabled. * | | |1 = Delay clock cycle Enabled. * |[5] |PD_WK_IE |Power-Down Mode Wake-Up Interrupt Enable * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |0 = Disabled. * | | |1 = Enabled. * | | |PD_WK_INT will be set if both PD_WK_IS and PD_WK_IE are high. * |[6] |PD_EN |Chip Power-Down Mode Enable Bit * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |When CPU sets this bit, the chip power down is enabled and chip will not enter Power-down mode until CPU sleep mode is also active * | | |When chip wakes up from Power-down mode, this bit will be auto cleared. * | | |When chip is in Power-down mode, the LDO, HXT and HIRC will be disabled, but LXT and LIRC are not controlled by Power-down mode. * | | |When power down, the PLL and system clock (CPU, HCLKx and PCLKx) are also disabled no matter the Clock Source selection. * | | |Peripheral clocks are not controlled by this bit, if peripheral Clock Source is from LXT or LIRC. * | | |In Power-down mode, flash macro power is ON. * | | |0 = Chip operated in Normal mode. * | | |1 = Chip power down Enabled. * |[8] |HXT_SELXT |HXT SELXT * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |0 = High frequency crystal loop back path Disabled. It is used for external oscillator. * | | |1 = High frequency crystal loop back path Enabled. It is used for external crystal. * |[9] |HXT_GAIN |HXT Gain Control Bit * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |Gain control is used to enlarge the gain of crystal to make sure crystal wok normally. * | | |If gain control is enabled, crystal will consume more power than gain control off. * | | |0 = Gain control Disabled. It means HXT gain is always high. * | | |For 16MHz to 24MHz crystal. * | | |1 = Gain control Enabled. HXT gain will be high lasting 2ms then low. This is for power saving. * | | |For 4MHz to 16MHz crystal. * |[10] |LXT_SCNT |LXT Stable Time Control * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |0 = Delay 4096 LXT before LXT output. * | | |1 = Delay 8192 LXT before LXT output. * |[12:11] |HXT_HF_ST |HXT Frequency Selection * | | |Set this bit to meet HXT frequency selection (Recommended) * | | |00 = HXT frequency is from 4 MHz to 12 MHz. * | | |01 = HXT frequency is from 12 MHz to 16 MHz. * | | |10 = HXT frequency is from 16 MHz to 24 MHz. * | | |11 = Reserved. */ __IO uint32_t PWRCTL; /** * AHBCLK * =================================================================================================== * Offset: 0x04 AHB Devices Clock Enable Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[0] |GPIO_EN |GPIO Controller Clock Enable * | | |0 = Disabled. * | | |1 = Enabled. * |[1] |DMA_EN |DMA Controller Clock Enable * | | |0 = Disabled. * | | |1 = Enabled. * |[2] |ISP_EN |Flash ISP Controller Clock Enable * | | |0 = Disabled. * | | |1 = Enabled. * |[3] |EBI_EN |EBI Controller Clock Enable * | | |0 = Disabled. * | | |1 = Enabled. * |[4] |SRAM_EN |SRAM Controller Clock Enable * | | |0 = Disabled. * | | |1 = Enabled. * |[5] |TICK_EN |System Tick Clock Enable * | | |0 = Disabled. * | | |1 = Enabled. */ __IO uint32_t AHBCLK; /** * APBCLK * =================================================================================================== * Offset: 0x08 APB Devices Clock Enable Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[0] |WDT_EN |Watchdog Timer Clock Enable Control * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |This bit is used to control the WDT APB clock only, The WDT engine Clock Source is from LIRC. * | | |0 = Disabled. * | | |1 = Enabled. * |[1] |RTC_EN |Real-Time-Clock Clock Enable Control * | | |This bit is used to control the RTC APB clock only, The RTC engine Clock Source is from LXT. * | | |0 = Disabled. * | | |1 = Enabled. * |[2] |TMR0_EN |Timer0 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[3] |TMR1_EN |Timer1 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[4] |TMR2_EN |Timer2 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[5] |TMR3_EN |Timer3 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[6] |FDIV_EN |Frequency Divider Output Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[7] |SC2_EN |SmartCard 2 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[8] |I2C0_EN |I2C0 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[9] |I2C1_EN |I2C1 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[12] |SPI0_EN |SPI0 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[13] |SPI1_EN |SPI1 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[14] |SPI2_EN |SPI2 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[16] |UART0_EN |UART0 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[17] |UART1_EN |UART1 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[20] |PWM0_CH01_EN|PWM0 Channel 0 And Channel 1Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[21] |PWM0_CH23_EN|PWM0 Channel 2 And Channel 3 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[22] |PWM1_CH01_EN|PWM1 Channel 0 And Channel 1 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[23] |PWM1_CH23_EN|PWM1 Channel 2 And Channel 3 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[25] |DAC_EN |12-Bit DAC Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[26] |LCD_EN |LCD Controller Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[27] |USBD_EN |USB FS Device Controller Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[28] |ADC_EN |Analog-Digital-Converter (ADC) Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[29] |I2S_EN |I2S Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[30] |SC0_EN |SmartCard 0 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. * |[31] |SC1_EN |SmartCard 1 Clock Enable Control * | | |0 = Disabled. * | | |1 = Enabled. */ __IO uint32_t APBCLK; /** * CLKSTATUS * =================================================================================================== * Offset: 0x0C Clock status monitor Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[0] |HXT_STB |HXT Clock Source Stable Flag * | | |0 = HXT clock is not stable or not enable. * | | |1 = HXT clock is stable. * |[1] |LXT_STB |LXT Clock Source Stable Flag * | | |0 = LXT clock is not stable or not enable. * | | |1 = LXT clock is stable. * |[2] |PLL_STB |PLL Clock Source Stable Flag * | | |0 = PLL clock is not stable or not enable. * | | |1 = PLL clock is stable. * |[3] |LIRC_STB |LIRC Clock Source Stable Flag * | | |0 = LIRC clock is not stable or not enable. * | | |1 = LIRC clock is stable. * |[4] |HIRC_STB |HIRC Clock Source Stable Flag * | | |0 = HIRC clock is not stable or not enable. * | | |1 = HIRC clock is stable. * |[7] |CLK_SW_FAIL|Clock Switch Fail Flag * | | |0 = Clock switch success. * | | |1 = Clock switch fail. * | | |This bit will be set when target switch Clock Source is not stable. This bit is write 1 clear */ __I uint32_t CLKSTATUS; /** * CLKSEL0 * =================================================================================================== * Offset: 0x10 Clock Source Select Control Register 0 * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[2:0] |HCLK_S |HCLK Clock Source Selection * | | |This is a protected register. Please refer to open lock sequence to program it. * | | |Note: * | | |Before Clock Source switches, the related clock sources (pre-select and new-select) must be turn on * | | |The 3-bit default value is reloaded with the value of CFOSC (Config0[26:24]) in user configuration register in Flash controller by any reset. * | | |Therefore the default value is either 000b or 111b. * | | |000 = HXT * | | |001 = LXT * | | |010 = PLL Clock * | | |011 = LIRC * | | |111 = HIRC * | | |Others = Reserved */ __IO uint32_t CLKSEL0; /** * CLKSEL1 * =================================================================================================== * Offset: 0x14 Clock Source Select Control Register 1 * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[1:0] |UART_S |UART 0/1 Clock Source Selection (UART0 And UART1 Use The Same Clock Source Selection) * | | |00 = HXT * | | |01 = LXT * | | |10 = PLL Clock * | | |11 = HIRC * |[3:2] |ADC_S |ADC Clock Source Selection * | | |00 = HXT * | | |01 = LXT * | | |10 = PLL Clock * | | |11 = HIRC * |[5:4] |PWM0_CH01_S|PWM0 Channel 0 And Channel 1 Clock Source Selection * | | |PWM0 channel 0 and channel 1 use the same Engine clock source, both of them with the same prescaler * | | |00 = HXT * | | |01 = LXT * | | |10 = HCLK * | | |11 = HIRC * |[7:6] |PWM0_CH23_S|PWM0 Channel 2 And Channel 3 Clock Source Selection * | | |PWM0 channel 2 and channel 3 use the same Engine clock source, both of them with the same prescaler * | | |00 = HXT * | | |01 = LXT * | | |10 = HCLK * | | |11 = HIRC * |[10:8] |TMR0_S |Timer0 Clock Source Selection * | | |000 = HXT * | | |001 = LXT * | | |010 = LIRC * | | |011 = External Pin * | | |111 = HIRC * | | |Others = Reserved * |[14:12] |TMR1_S |Timer1 Clock Source Selection * | | |000 = HXT * | | |001 = LXT * | | |010 = LIRC * | | |011 = External Pin * | | |111 = HIRC * | | |Others = Reserved * |[18] |LCD_S |LCD Clock Source Selection * | | |0 = Clock Source from LXT. * | | |1 = Reserved. */ __IO uint32_t CLKSEL1; /** * CLKSEL2 * =================================================================================================== * Offset: 0x18 Clock Source Select Control Register 2 * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[3:2] |FRQDIV_S |Clock Divider Clock Source Selection * | | |00 = HXT * | | |01 = LXT * | | |10 = HCLK * | | |11 = HIRC * |[5:4] |PWM1_CH01_S|PWM1 Channel 0 And Channel 1 Clock Source Selection * | | |PWM1 channel 0 and channel 1 use the same Engine clock source, both of them with the same pre-scale * | | |00 = HXT * | | |01 = LXT * | | |10 = HCLK * | | |11 = HIRC * |[7:6] |PWM1_CH23_S|PWM1 Channel 2 And Channel 2 Clock Source Selection * | | |PWM1 channel 2 and channel 3 use the same Engine clock source, both of them with the same pre-scale * | | |00 = HXT * | | |01 = LXT * | | |10 = HCLK * | | |11 = HIRC * |[10:8] |TMR2_S |Timer2 Clock Source Selection * | | |000 = HXT * | | |001 = LXT * | | |010 = LIRC * | | |011 = External Pin * | | |111 = HIRC * | | |Others = Reserved * |[14:12] |TMR3_S |Timer3 Clock Source Selection * | | |000 = HXT * | | |001 = LXT * | | |010 = LIRC * | | |011 = External Pin * | | |111 = HIRC * | | |Others = Reserved * |[17:16] |I2S_S |I2S Clock Source Selection * | | |00 = HXT * | | |01 = PLL Clock * | | |10 = HIRC * | | |11 = HIRC * |[19:18] |SC_S |SC Clock Source Selection * | | |00 = HXT * | | |01 = PLL Clock * | | |10 = HIRC * | | |11 = HIRC * | | |Note: SC0,SC1 and SC2 use the same Clock Source selection but they have different clock divider number. * |[20] |SPI0_S |SPI0 Clock Source Selection * | | |0 = PLL. * | | |1 = HCLK. * |[21] |SPI1_S |SPI1 Clock Source Selection * | | |0 = PLL. * | | |1 = HCLK. * |[22] |SPI2_S |SPI2 Clock Source Selection * | | |0 = PLL. * | | |1 = HCLK. */ __IO uint32_t CLKSEL2; /** * CLKDIV0 * =================================================================================================== * Offset: 0x1C Clock Divider Number Register 0 * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[3:0] |HCLK_N |HCLK Clock Divide Number From HCLK Clock Source * | | |The HCLK clock frequency = (HCLK Clock Source frequency) / (HCLK_N + 1). * |[7:4] |USB_N |USB Clock Divide Number From PLL Clock * | | |The USB clock frequency = (PLL frequency ) / (USB_N + 1). * |[11:8] |UART_N |UART Clock Divide Number From UART Clock Source * | | |The UART clock frequency = (UART Clock Source frequency ) / (UART_N + 1). * |[15:12] |I2S_N |I2S Clock Divide Number From I2S Clock Source * | | |The I2S clock frequency = (I2S Clock Source frequency ) / (I2S_N + 1). * |[23:16] |ADC_N |ADC Clock Divide Number From ADC Clock Source * | | |The ADC clock frequency = (ADC Clock Source frequency ) / (ADC_N + 1). * |[31:28] |SC0_N |SC 0 Clock Divide Number From SC 0 Clock Source * | | |The SC 0 clock frequency = (SC0 Clock Source frequency ) / (SC0_N + 1). */ __IO uint32_t CLKDIV0; /** * CLKDIV1 * =================================================================================================== * Offset: 0x20 Clock Divider Number Register 1 * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[3:0] |SC1_N |SC 1 Clock Divide Number From SC 1 Clock Source * | | |The SC 1 clock frequency = (SC 1 Clock Source frequency ) / (SC1_N + 1). * |[7:4] |SC2_N |SC 2 Clock Divide Number From SC2 Clock Source * | | |The SC 2 clock frequency = (SC 2 Clock Source frequency ) / (SC2_N + 1). */ __IO uint32_t CLKDIV1; /** * PLLCTL * =================================================================================================== * Offset: 0x24 PLL Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[4:0] |FB_DV |PLL Feedback Divider Control Pins * | | |Refer to the formulas below the table. * | | |The range of FB_DV is from 0 to 63. * |[9:8] |IN_DV |PLL Input Divider Control Pins * | | |Refer to the formulas below the table. * |[12] |OUT_DV |PLL Output Divider Control Pins * | | |Refer to the formulas below the table. This bit MUST be 0 for PLL output low deviation. * |[16] |PD |Power-Down Mode * | | |If set the PD_EN bit "1" in PWR_CTL register, the PLL will enter Power-down mode too * | | |0 = PLL is in normal mode. * | | |1 = PLL is in power-down mode (default). * |[17] |PLL_SRC |PLL Source Clock Select * | | |0 = PLL source clock from HXT. * | | |1 = PLL source clock from HIRC. */ __IO uint32_t PLLCTL; /** * FRQDIV * =================================================================================================== * Offset: 0x28 Frequency Divider Control Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[3:0] |FSEL |Divider Output Frequency Selection Bits * | | |The formula of output frequency is * | | |Fout = Fin/2^(N+1),. * | | |Where Fin is the input clock frequency, Fout is the frequency of divider output clock and N is the 4-bit value of FSEL[3:0]. * |[4] |FDIV_EN |Frequency Divider Enable Bit * | | |0 = Frequency Divider Disabled. * | | |1 = Frequency Divider Enabled. */ __IO uint32_t FRQDIV; /** * MCLKO * =================================================================================================== * Offset: 0x2C Module Clock Output Register * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[5:0] |MCLK_SEL |Module Clock Output Source Selection (PC.0) * | | |000000 = ISP_CLK * | | |000001 = HIRC * | | |000010 = HXT * | | |000011 = LXT * | | |000100 = LIRC * | | |000101 = PLL output * | | |000110 = PLL input * | | |000111 = System Tick * | | |001000 = HCLK clock * | | |001010 = PCLK clock * | | |100000 = TMR0_CLK * | | |100001 = TMR1_CLK * | | |100010 = UART0_CLK * | | |100011 = USB_CLK * | | |100100 = ADC_CLK * | | |100101 = WDT_CLK * | | |100110 = PWM0_CH01_CLK * | | |100111 = PWM0_CH32_CLK * | | |101001 = LCD_CLK * | | |111000 = TMR2_CLK * | | |111001 = TMR3_CLK * | | |111010 = UART1_CLK * | | |111011 = PWM1_CH01_CLK * | | |111100 = PWM1_CH23_CLK * | | |111101 = I²S_CLK * | | |111110 = SC0_CLK * | | |111111 = SC1_CLK * |[7] |MCLK_EN |Module Clock Output Enable * | | |User can get the module clock output from PC.0 pin via choosing the clock source in the MCLK_SEL bit field and then setting MCLK_EN bit to 1. * | | |0 = Module clock output Disabled. * | | |1 = Module clock output Enabled. * | | |Note: If this bit is enabled, PC.0 will be configured to module clock output and the setting of PC0_MFP will be ineffective */ __IO uint32_t MCLKO; /** * WK_INTSTS * =================================================================================================== * Offset: 0x30 Wake-up interrupt status * --------------------------------------------------------------------------------------------------- * |Bits |Field |Descriptions * | :----: | :----: | :---- | * |[0] |PD_WK_IS |Wake-Up Interrupt Status In Chip Power-Down Mode * | | |This bit indicates that some event resumes chip from Power-down mode * | | |The status is set if external interrupts, UART, GPIO, RTC, USB, SPI, Timer, WDT, and BOD wake-up occurred. * | | |Write 1 to clear this bit. */ __IO uint32_t WK_INTSTS; } CLK_T;

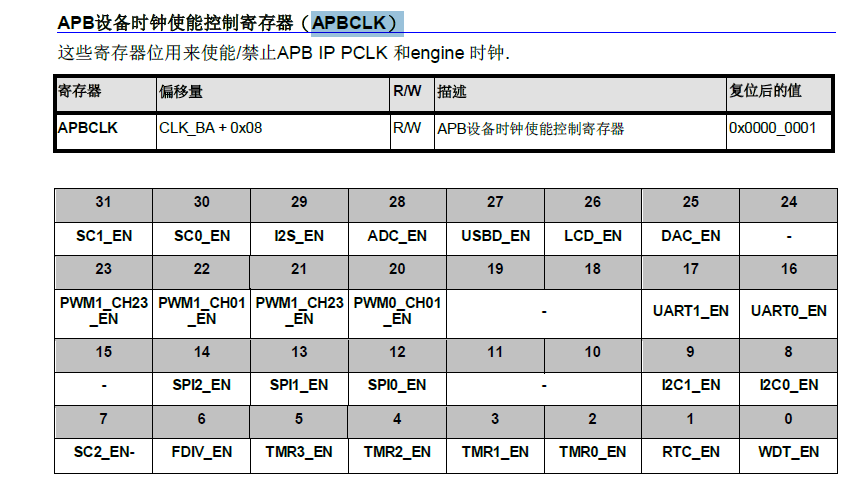

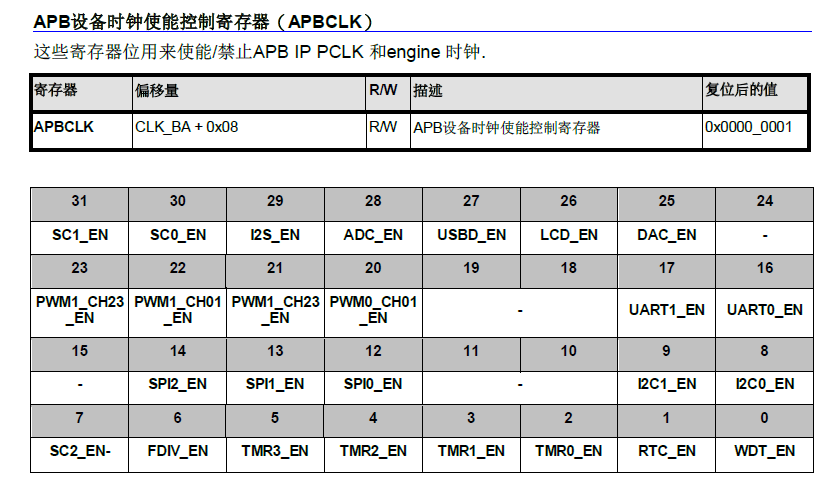

����datasheet��ֻ��Ҫ��APBCLK�IJ��־Ϳ����ˡ�

��������

���T�����r������;����ܛ�������}�r��(zh��)��ϵ�y(t��ng)��(f��)λ���ܣ��@���Է�ֹϵ�y(t��ng)�o���ڵؒ��𡣳���֮�⣬���T�����r��߀֧��CPU �ĵ��ģʽ���ѵĹ��ܣ�

���⮔(d��ng) CPU �M(j��n)����ģʽ�r��WDT Ӌ(j��)��(sh��)�����Ԅ����á�

���T�����r������һ��18 λ�������\(y��n)��Ӌ(j��)��(sh��)�������r����g���ɾ��̡�

�����ı���o���˿��T�����r�g���x��

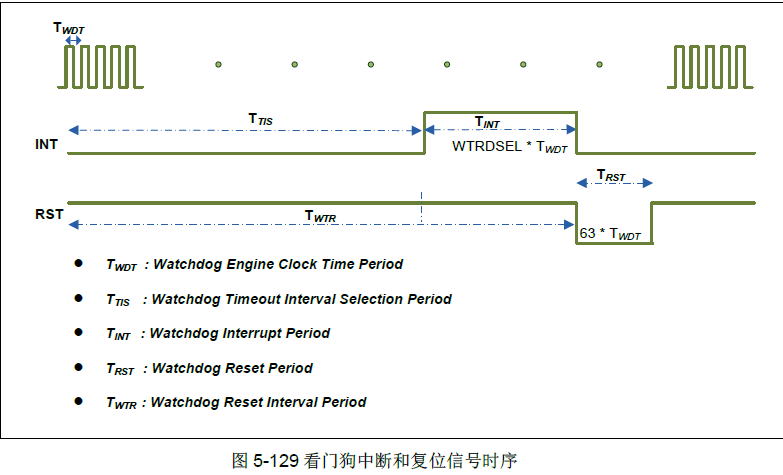

�������ĈDƬ�o���˿��T���Д���̖�͏�(f��)λ��̖�ĕr��

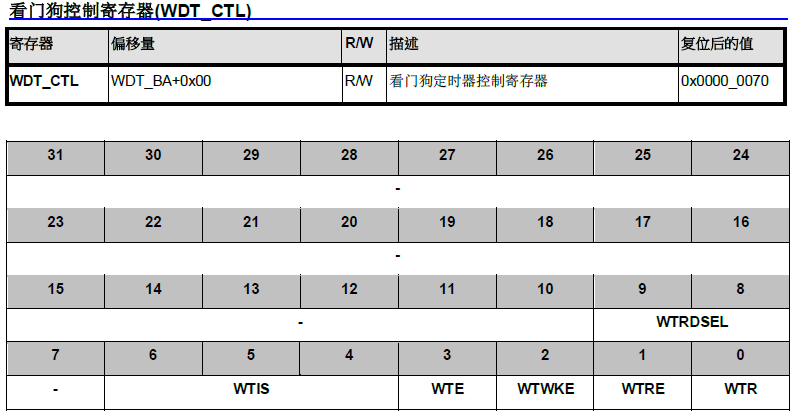

�O(sh��)�� WTE (WDT_CTL[3]) ʹ�ܿ��T�����r����WDT Ӌ(j��)��(sh��)���_ʼӋ(j��)��(sh��)��

��(d��ng)Ӌ(j��)��(sh��)���_(d��)���x��ij��r�g�������T�����r���Д���(bi��o)־W(w��ng)DT_IS ������������λ����Ո��WDT �Д� (������T�����r���Д�ʹ��λWDT_IE ��λ)��ͬ�r�o�������r�¼�����һ��ָ�����ӕr���^ WTRDSEL �O(sh��)�ã��Ñ������ԓָ���ӕr�^��ǰ�O(sh��)��WTR (WDT_CTL[0]) (���T�����r����(f��)λ) ��߁��(f��)λ18 λ WDT Ӌ(j��)��(sh��)�����Է�ֹоƬ��(f��)λ��

WTR λ��WDT Ӌ(j��)��(sh��)����(f��)λ����Ӳ���Ԅ����㡣

ͨ�^�O(sh��)��WTIS (WDT_CTL[6:4])����8 �N��ָ���ӕr�r�g�ij��r�g���ɹ��x������ı���

�����ָ�����t�r�g�^�ں�WDT Ӌ(j��)��(sh��)���]�б����㣬���T�����r������λ���T�����r����(f��)λ��(bi��o)־(WDT_RST_IS)������(f��)λCPU��

�@����(f��)λ�����m(x��)63 �� WDT �r� (TRST)��Ȼ��оƬ�؆������ď�(f��)λ����(0x0000_0000) ̎�����_ʼ��(zh��)�г���

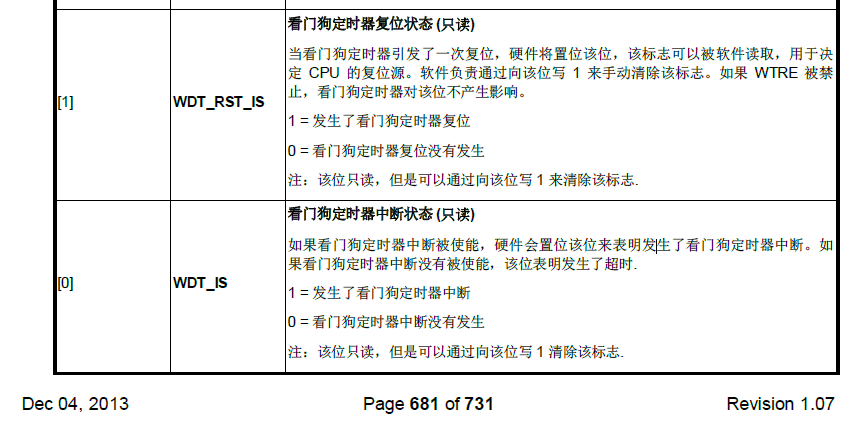

WDT_RST_IS ���������T����(f��)λ���㡣�Ñ�����ܛ��݆ԃWDT_RST_IS ���R�e��(f��)λԴ�Ƿ�WDT��

������ԭ�����ٿ�һ�������ļĴ�����Ȼ���ҵ�����(y��ng)�ļĴ������Ϳ����M(j��n)��������

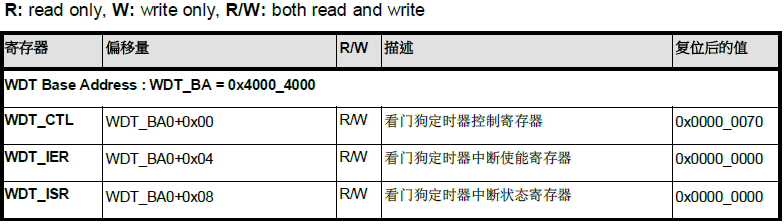

�Ĵ�����ʲô�����ҵ�������ǵ�ַ���@����ַ����(y��ng)��Ӳ����

�D�ǼĴ����Ļ���ַ��ƫ�Ƶ�ַ��

����(y��ng)�ĺ궨�x�飺

#define APB1PERIPH_BASE ((uint32_t)0x40000000) ///< APB1 base address #define WDT_BASE (APB1PERIPH_BASE + 0x04000) ///< WDT register base address #define WDT ((WDT_T *) WDT_BASE) ///< Pointer to WDT register structure

������WDT�Ļ���ַ��Ҳ����WDT_BA�IJ��֣������������ļĴ�������(y��ng)��ַ

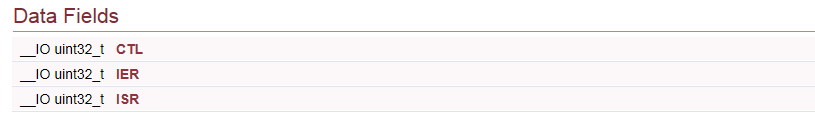

typedef struct {

/**

* CTL

* ===================================================================================================

* Offset: 0x00 Watchdog Timer Control Register

* ---------------------------------------------------------------------------------------------------

* |Bits |Field |Descriptions

* | :----: | :----: | :---- |

* |[0] |WTR |Clear Watchdog Timer

* | | |This is a protected register. Please refer to open lock sequence to program it.

* | | |Set this bit will clear the Watchdog timer.

* | | |0 = No effect.

* | | |1 = Reset the contents of the Watchdog timer.

* | | |Note: This bit will be auto cleared after few clock cycles.

* |[1] |WTRE |Watchdog Timer Reset Function Enable

* | | |This is a protected register. Please refer to open lock sequence to program it.

* | | |Setting this bit will enable the Watchdog timer reset function.

* | | |0 = Watchdog timer reset function Disabled.

* | | |1 = Watchdog timer reset function Enabled.

* |[2] |WTWKE |Watchdog Timer Wake-Up Function Enable

* | | |This is a protected register. Please refer to open lock sequence to program it.

* | | |0 = Watchdog timer Wake-up CPU function Disabled.

* | | |1 = Wake-up function Enabled so that Watchdog timer time-out can wake up CPU from power-down mode.

* |[3] |WTE |Watchdog Timer Enable

* | | |This is a protected register. Please refer to open lock sequence to program it.

* | | |0 = Watchdog timer Disabled (this action will reset the internal counter).

* | | |1 = Watchdog timer Enabled.

* |[6:4] |WTIS |Watchdog Timer Interval Selection

* | | |This is a protected register. Please refer to open lock sequence to program it.

* | | |These three bits select the time-out interval for the Watchdog timer.

* | | |This count is free running counter.

* | | |Please refer to the Table 5-16.

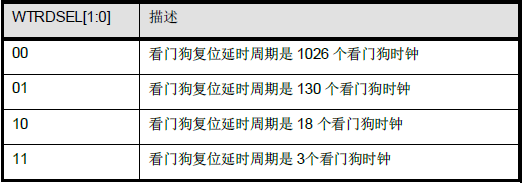

* |[9:8] |WTRDSEL |Watchdog Timer Reset Delay Select

* | | |When watchdog timeout happened, software has a time named watchdog reset delay period to clear watchdog timer to prevent watchdog reset happened.

* | | |Software can select a suitable value of watchdog reset delay period for different watchdog timeout period.

* | | |00 = Watchdog reset delay period is 1026 watchdog clock

* | | |01 = Watchdog reset delay period is 130 watchdog clock

* | | |10 = Watchdog reset delay period is 18 watchdog clock

* | | |11 = Watchdog reset delay period is 3 watchdog clock

* | | |This register will be reset if watchdog reset happened

*/

__IO uint32_t CTL;

/**

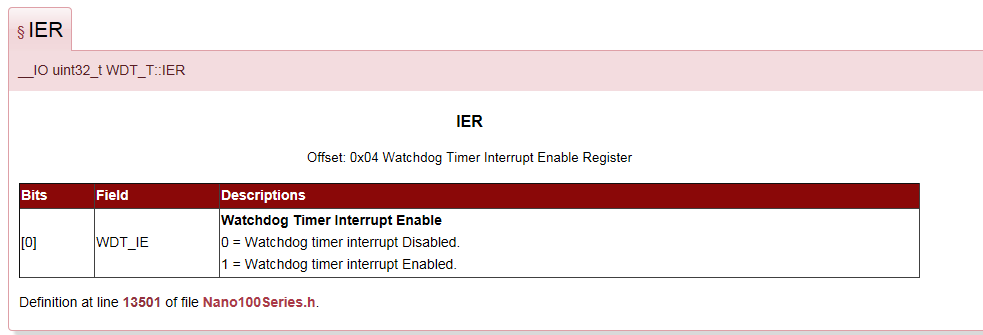

* IER

* ===================================================================================================

* Offset: 0x04 Watchdog Timer Interrupt Enable Register

* ---------------------------------------------------------------------------------------------------

* |Bits |Field |Descriptions

* | :----: | :----: | :---- |

* |[0] |WDT_IE |Watchdog Timer Interrupt Enable

* | | |0 = Watchdog timer interrupt Disabled.

* | | |1 = Watchdog timer interrupt Enabled.

*/

__IO uint32_t IER;

/**

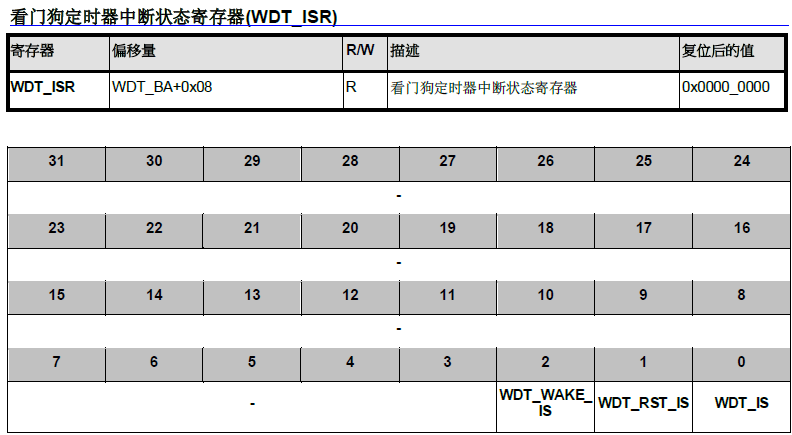

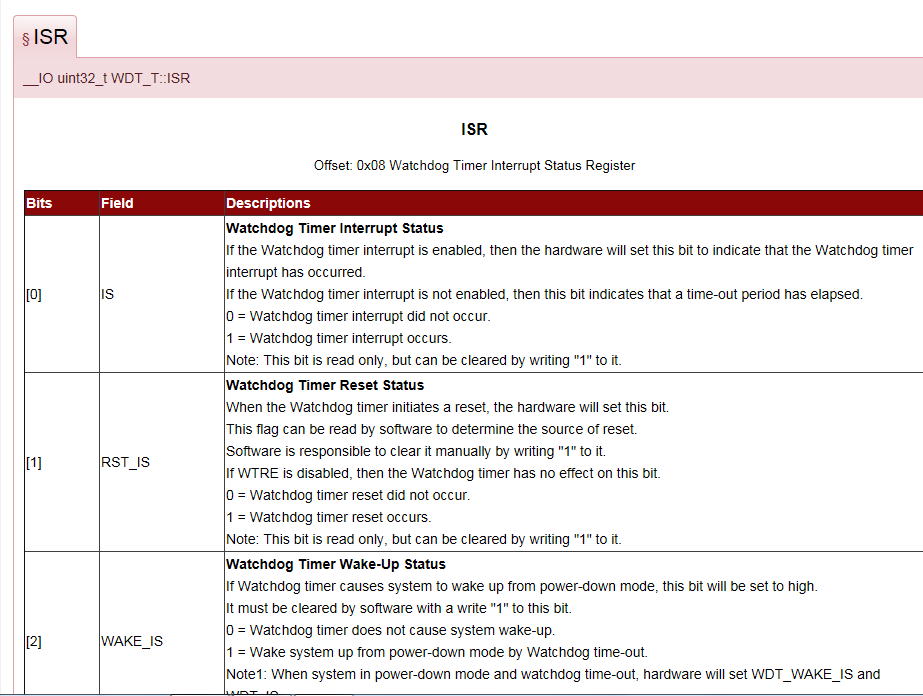

* ISR

* ===================================================================================================

* Offset: 0x08 Watchdog Timer Interrupt Status Register

* ---------------------------------------------------------------------------------------------------

* |Bits |Field |Descriptions

* | :----: | :----: | :---- |

* |[0] |IS |Watchdog Timer Interrupt Status

* | | |If the Watchdog timer interrupt is enabled, then the hardware will set this bit to indicate that the Watchdog timer interrupt has occurred.

* | | |If the Watchdog timer interrupt is not enabled, then this bit indicates that a time-out period has elapsed.

* | | |0 = Watchdog timer interrupt did not occur.

* | | |1 = Watchdog timer interrupt occurs.

* | | |Note: This bit is read only, but can be cleared by writing "1" to it.

* |[1] |RST_IS |Watchdog Timer Reset Status

* | | |When the Watchdog timer initiates a reset, the hardware will set this bit.

* | | |This flag can be read by software to determine the source of reset.

* | | |Software is responsible to clear it manually by writing "1" to it.

* | | |If WTRE is disabled, then the Watchdog timer has no effect on this bit.

* | | |0 = Watchdog timer reset did not occur.

* | | |1 = Watchdog timer reset occurs.

* | | |Note: This bit is read only, but can be cleared by writing "1" to it.

* |[2] |WAKE_IS |Watchdog Timer Wake-Up Status

* | | |If Watchdog timer causes system to wake up from power-down mode, this bit will be set to high.

* | | |It must be cleared by software with a write "1" to this bit.

* | | |0 = Watchdog timer does not cause system wake-up.

* | | |1 = Wake system up from power-down mode by Watchdog time-out.

* | | |Note1: When system in power-down mode and watchdog time-out, hardware will set WDT_WAKE_IS and WDT_IS.

* | | |Note2: After one engine clock, this bit can be cleared by writing "1" to it

*/

__IO uint32_t ISR;

} WDT_T;

#define WDT_CTL_WTR_Msk (0x1ul << WDT_CTL_WTR_Pos) /*!< WDT_T::CTL: WTR Mask */ #define WDT_CTL_WTRE_Pos (1) /*!< WDT_T::CTL: WTRE Position */ #define WDT_CTL_WTRE_Msk (0x1ul << WDT_CTL_WTRE_Pos) /*!< WDT_T::CTL: WTRE Mask */ #define WDT_CTL_WTWKE_Pos (2) /*!< WDT_T::CTL: WTWKE Position */ #define WDT_CTL_WTWKE_Msk (0x1ul << WDT_CTL_WTWKE_Pos) /*!< WDT_T::CTL: WTWKE Mask */ #define WDT_CTL_WTE_Pos (3) /*!< WDT_T::CTL: WTE Position */ #define WDT_CTL_WTE_Msk (0x1ul << WDT_CTL_WTE_Pos) /*!< WDT_T::CTL: WTE Mask */ #define WDT_CTL_WTIS_Pos (4) /*!< WDT_T::CTL: WTIS Position */ #define WDT_CTL_WTIS_Msk (0x7ul << WDT_CTL_WTIS_Pos) /*!< WDT_T::CTL: WTIS Mask */ #define WDT_CTL_WTRDSEL_Pos (8) /*!< WDT_T::CTL: WTRDSEL Position */ #define WDT_CTL_WTRDSEL_Msk (0x3ul << WDT_CTL_WTRDSEL_Pos) /*!< WDT_T::CTL: WTRDSEL Mask */ //���ϲ����Ƿ�е����죿��WDT_CTL�ĵ�ַ��һһ����(y��ng)�ģ�����Ҳ��һ�ӣ�Ҳ�����f0bit��WTR,1��WTRE.WTIS�ǵ���λ������������ռ��λ�� //������һ���Ĵ����͕�����λ���ֱ�����һλ���������Ƶڰ�λ�����涼��һ�ӵ�

#define WDT_IER_IE_Pos (0) /*!< WDT_T::IER: IE Position */ #define WDT_IER_IE_Msk (0x1ul << WDT_IER_IE_Pos) /*!< WDT_T::IER: IE Mask */ #define WDT_ISR_IS_Pos (0) /*!< WDT_T::ISR: IS Position */ #define WDT_ISR_IS_Msk (0x1ul << WDT_ISR_IS_Pos) /*!< WDT_T::ISR: IS Mask */ #define WDT_ISR_RST_IS_Pos (1) /*!< WDT_T::ISR: RST_IS Position */ #define WDT_ISR_RST_IS_Msk (0x1ul << WDT_ISR_RST_IS_Pos) /*!< WDT_T::ISR: RST_IS Mask */ #define WDT_ISR_WAKE_IS_Pos (2) /*!< WDT_T::ISR: WAKE_IS Position */ # define WDT_ISR_WAKE_IS_Msk (0x1ul << WDT_ISR_WAKE_IS_Pos) /*!< WDT_T::ISR: WAKE_IS Mask */ /**@}*/ /* WDT_CONST */ /**@}*/ /* end of WDT register group */ ������������Ӳ��֣���������ô���䌍(sh��)���Ǐ�(qi��ng)�Ƶ�ַ�D(zhu��n)�Q�������ַ��Ȼ�����(j��)��ַ�M(j��n)�С����üĴ������ǽo����һ��ݔ�룬����ݔ�������^�mȻ���|(zh��)�����@�ӣ��������������Σ� ��?y��n)������ļĴ����ܶ࣬���Ҵ��Ҫ�漰����·���ⲿ�������κ�һ���h(hu��n)��(ji��)���e�����������_(d��)��Ч�����mȻ�韩�����ֶ�����Ҏ(gu��)�ɵġ� �@�ﴩ��һ�t�Ĵ�����С֪�R �ڴ惦�� Block2 �@�K�^(q��)���O(sh��)Ӌ(j��)����Ƭ�����O(sh��)���������Ă��ֹ�(ji��)��һ����Ԫ����32bit��ÿһ����Ԫ����(y��ng)��ͬ�Ĺ��ܣ���(d��ng)�҂������@Щ��Ԫ�r�Ϳ����(q��)�����O(sh��)������ �҂������ҵ�ÿ����Ԫ����ʼ��ַ��Ȼ��ͨ�^ C�Z��ָᘵIJ�����ʽ���L���@Щ��Ԫ�����ÿ�ζ���ͨ�^�@�N��ַ�ķ�ʽ���L�������H����ӛ��߀���׳��e�� �@�r�҂����Ը���(j��)ÿ����Ԫ���ܵIJ�ͬ���Թ��ܞ����o�@����(n��i)���Ԫȡһ���e�����@���e�������҂���(j��ng)���f�ļĴ����� �@���o�ѽ�(j��ng)����õ�ַ�����ض����ܵă�(n��i)���Ԫȡ�e�����^�̾ͽмĴ���ӳ�䡣 ��(d��ng)Ȼ�Ĵ�����ܛ����Ҳ��Ӳ���ģ��·�������ҵ����˲����������������

�ٲ�һ�tС֪�R�����P(gu��n)�ڏ�(qi��ng)������D(zhu��n)�Q��

�P(gu��n)��һ��

int *ptr=(int *)(&a+1)

���}��̽ӑ

�W(w��ng)�j(lu��)�Ͽ����@��һ������˼���}Ŀ�����P(gu��n)�ڔ�(sh��)�M�cָᘵĆ��}���������£�

main()

{

int a[5]={1,2,3,4,5};

int *ptr=(int *)(&a+1);

printf("%d,%d",*(a+1),*(ptr-1));

}

ݔ���飺2,5

Ո������ϴ��a��ݔ���Y(ji��)���������£�

*(a+1)�䌍(sh��)�ܺ��ξ���ָa[1],ݔ����2. ���}�P(gu��n)�I�����ڵڶ����c(di��n)��

*(ptr-1)ݔ������٣�

������£�&a+1������ַ+1��ϵ�y(t��ng)���J(r��n)�����һ������a��(sh��)�M��ƫ����������(sh��)�Ma�Ĵ�С��Ҳ����5��int�Ĵ�С��������

int *ptr=(int *)(&a+1);�䌍(sh��)ptr��(sh��)�H��&(a[5]),Ҳ����a+5. ԭ��?y��n)���أ?/p>

&a�ǔ�(sh��)�Mָᘣ�����͞�int(*)[5]; ��ָᘼ�1Ҫ����(j��)ָ���ͼ���һ����ֵ����ͬ��͵�ָ�+1֮�����ӵĴ�С��ͬ��

a���L�Ȟ�5��int��(sh��)�Mָᘣ�����Ҫ��5*sizeof(int)������ptr��(sh��)�H��a[5],����ptr�c��&a+1������Dz�һ�ӵģ��@�c(di��n)�dz���Ҫ������ptr-1ֻ���pȥsizeof(int*),

a��&a�ĵ�ַ��һ�ӵģ�����˼�Ͳ�һ���ˣ�a�ǔ�(sh��)�M��ַ��Ҳ����a[0]�ĵ�ַ��&a�nj���(sh��)�M����ַ��a+1�ǔ�(sh��)�M��һԪ�صĵ�ַ����a[1],&a+1����һ������ĵ�ַ����a[5]��

С�ˣ��͵�ַ��ŵ�λ��(sh��)��(j��)��

��ˣ��͵�ַ��Ÿ�λ��(sh��)��(j��)��

���W(w��ng)�j(lu��)�Ђ�ݔ���ô�ˡ�

�ô��a��(sh��)�F(xi��n)��С�������˹����w��ԭ�팍(sh��)�F(xi��n)�Д��DZ��^���ε�һ��������

���ڹ����w�е�����Ԫ�ض������һ�K��(n��i)����g�У���b����ʼ��ַ�Ǐ�int�͵���ʼ��ַ���R�ġ����Ԍ�һ��int�͵Ĕ�(sh��)��(j��)�M(j��n)�Ќ�1������Ǵ�˵�Ԓ��char�͵�b�͕���1����tb�͞�0.

�������҂��ف������������������ļĴ������@��һ���ܴ������Ո���Ŀ��꣬���ŕ����ի@�ġ�

��Ȼ�҂���Ϥ�˵ӡ���ô�҂���(d��ng)Ȼ����ֹ���ڴˣ���(y��ng)�ÌӵĖ|������(d��ng)ȻҲҪ����

�ڹ���������һ�¹�(ji��)�r���҂��䌍(sh��)�ѽ�(j��ng)�����ˣ����ľ��w�����Ͳ��E�����Ǟ����҂�����������ͷ����{(di��o)�ã��҂��Q�����Î캯��(sh��)����ʽ�����v���@����(y��ng)�ã����������f�����@ֻ��һ��С�Ĺٷ����̣�������m(x��)���д��͵��(xi��ng)Ŀ�����漰���ܵ�Ԓ���ҕ�������������

��Ȼ�҂�Ҫ�ÿ��T������ȻҪʹ�������҂���(d��ng)ȻҪ���_�������M(j��n)�г�ʼ����

�����x��r�

void SYS_Init(void)

{

/*---------------------------------------------------------------------------------------------------------*/

/* Init System Clock */

/*---------------------------------------------------------------------------------------------------------*/

/* Unlock protected registers */

SYS_UnlockReg();

/* Enable External XTAL (4~24 MHz) */

CLK_EnableXtalRC(CLK_PWRCTL_HXT_EN_Msk);

/* Enable LIRC */

CLK_EnableXtalRC(CLK_PWRCTL_LIRC_EN_Msk);

/* Waiting for 12MHz clock ready */

CLK_WaitClockReady( CLK_CLKSTATUS_HXT_STB_Msk);

/* Waiting for LIRC clock ready */

CLK_WaitClockReady( CLK_CLKSTATUS_LIRC_STB_Msk);

/* Switch HCLK clock source to HXT */

CLK_SetHCLK(CLK_CLKSEL0_HCLK_S_HXT,CLK_HCLK_CLK_DIVIDER(1));

/* Enable IP clock */

CLK_EnableModuleClock(UART0_MODULE);

CLK_EnableModuleClock(WDT_MODULE);/*

#define WDT_MODULE ((1UL<<31)|(3<<29)|(MODULE_NoMsk<<25)|( 0<<20)|(0<<18)|(MODULE_NoMsk<<10)|( 0<<5)|CLK_APBCLK_WDT_EN_Pos )

/*!< Watchdog Timer Module */

#define MODULE_NoMsk 0x0 /*!< Not mask on MODULE index */

#define WDT_MODULE ((1UL<<31)|(3<<29)|(MODULE_NoMsk<<25)|( 0<<20)|(0<<18)|(MODULE_NoMsk<<10)|( 0<<5)|CLK_APBCLK_WDT_EN_Pos )

#define CLK_APBCLK_WDT_EN_Pos (0) /*!< CLK_T::APBCLK: WDT_EN Position */

#define CLK_APBCLK_WDT_EN_Msk (0x1ul << CLK_APBCLK_WDT_EN_Pos) /*!< CLK_T::APBCLK: WDT_EN Mask

*/

/* Select IP clock source */

CLK_SetModuleClock(UART0_MODULE, CLK_CLKSEL1_UART_S_HXT, CLK_UART_CLK_DIVIDER(1));

CLK_SetModuleClock(WDT_MODULE, 0, 0);

/* Update System Core Clock */

/* User can use SystemCoreClockUpdate() to calculate SystemCoreClock. */

SystemCoreClockUpdate();

/*---------------------------------------------------------------------------------------------------------*/

/* Init I/O Multi-function */

/*---------------------------------------------------------------------------------------------------------*/

/* Set GPB multi-function pins for UART0 RXD and TXD */

SYS->PB_L_MFP &= ~(SYS_PB_L_MFP_PB0_MFP_Msk | SYS_PB_L_MFP_PB1_MFP_Msk);

SYS->PB_L_MFP |= (SYS_PB_L_MFP_PB1_MFP_UART0_TX | SYS_PB_L_MFP_PB0_MFP_UART0_RX);

/* Lock protected registers */

SYS_LockReg();

}void CLK_SetModuleClock(uint32_t u32ModuleIdx, uint32_t u32ClkSrc, uint32_t u32ClkDiv)

{

uint32_t u32tmp=0,u32sel=0,u32div=0;

if(MODULE_CLKDIV_Msk(u32ModuleIdx)!=MODULE_NoMsk) {u32div =(uint32_t)&CLK->CLKDIV0+((MODULE_CLKDIV(u32ModuleIdx))*4);u32tmp = *(volatile uint32_t *)(u32div);u32tmp = ( u32tmp & ~(MODULE_CLKDIV_Msk(u32ModuleIdx)<<MODULE_CLKDIV_Pos(u32ModuleIdx)) ) | u32ClkDiv;*(volatile uint32_t *)(u32div) = u32tmp;}

#define MODULE_CLKDIV_Msk(x) ((x >>10) & 0xff) /*!< Calculate CLKDIV mask offset on MODULE index */

#define MODULE_CLKDIV_Msk(x) ((x >>10) & 0xff) /*!< Calculate CLKDIV mask offset on MODULE index */

#define MODULE_CLKDIV_Pos(x) ((x >>5 ) & 0x1f) /*!< Calculate CLKDIV position offset on MODULE index */

#define MODULE_CLKDIV_Pos(x) ((x >>5 ) & 0x1f) /*!< Calculate CLKDIV position offset on MODULE index */

( u32tmp & ~(MODULE_CLKDIV_Msk(u32ModuleIdx)<<MODULE_CLKDIV_Pos(u32ModuleIdx)) ) | u32ClkDiv;

~((1110 0000 0000 0000 0000 0000 0000>>10) <<(1110 0000 0000 0000 0000 0000 >>5))|u32Div mingbaile zhongyv

// 1110 0000 0000 0000 0000 0000 0000 0000 ����5�0000 1110 0000 0000 0000 0000 0000 0000 0000

// 1110 0000 0000 0000 0000 0000 0000 0000 ����10� 0000 0000 0111 0000 0000 0000 0000 0000 0000

//���^ģ�K���ǽo�r犵�WDT_ENλһ��ʹ��

if(MODULE_CLKSEL_Msk(u32ModuleIdx)!=MODULE_NoMsk) {u32sel = (uint32_t)&CLK->CLKSEL0+((MODULE_CLKSEL(u32ModuleIdx))*4);u32tmp = *(volatile uint32_t *)(u32sel);u32tmp = ( u32tmp & ~(MODULE_CLKSEL_Msk(u32ModuleIdx)<<MODULE_CLKSEL_Pos(u32ModuleIdx)) ) | u32ClkSrc;*(volatile uint32_t *)(u32sel) = u32tmp;}}

���҂����_ʼ���v���O(sh��)�� WTE (WDT_CTL[3]) ʹ�ܿ��T�����r����WDT Ӌ(j��)��(sh��)���_ʼӋ(j��)��(sh��)�����ڹ���������һ���ֵ�һ�䣩

/*** @brief This function make WDT module start counting with different time-out interval* @param[in] u32TimeoutInterval Time-out interval period of WDT module. Valid values are:* - \ref WDT_TIMEOUT_2POW4* - \ref WDT_TIMEOUT_2POW6* - \ref WDT_TIMEOUT_2POW8* - \ref WDT_TIMEOUT_2POW10* - \ref WDT_TIMEOUT_2POW12* - \ref WDT_TIMEOUT_2POW14* - \ref WDT_TIMEOUT_2POW16* - \ref WDT_TIMEOUT_2POW18* @param[in] u32ResetDelay Reset delay period while WDT time-out happened. Valid values are:* - \ref WDT_RESET_DELAY_3CLK* - \ref WDT_RESET_DELAY_18CLK* - \ref WDT_RESET_DELAY_130CLK* - \ref WDT_RESET_DELAY_1026CLK* @param[in] u32EnableReset Enable WDT reset system function. Valid values are TRUE and FALSE* @param[in] u32EnableWakeup Enable WDT wake-up system function. Valid values are TRUE and FALSE* @return None*/

void WDT_Open(uint32_t u32TimeoutInterval,

uint32_t u32ResetDelay,

uint32_t u32EnableReset,

uint32_t u32EnableWakeup)

{

WDT->CTL = u32TimeoutInterval | u32ResetDelay | WDT_CTL_WTE_Msk |

(u32EnableReset << WDT_CTL_WTRE_Pos) |

(u32EnableWakeup << WDT_CTL_WTWKE_Pos);

return;

}

�@����˼�����x�����ij��r�r�g���͏�(f��)λ���t�r�g�͆���ϵ�y(t��ng)���ܣ��͏�(f��)λϵ�y(t��ng)����

u32TimeoutInterval WDTģ�K�ij��r�g���r�g����Чֵ�ǣ�

* - \ ref WDT_TIMEOUT_2POW4

* - \ ref WDT_TIMEOUT_2POW6

* - \ ref WDT_TIMEOUT_2POW8

* - \ ref WDT_TIMEOUT_2POW10

* - \ ref WDT_TIMEOUT_2POW12

* - \ ref WDT_TIMEOUT_2POW14

* - \ ref WDT_TIMEOUT_2POW16

* - \ ref WDT_TIMEOUT_2POW18

* @param [in] u32ResetDelay�l(f��)��WDT���r�ď�(f��)λ���t�r�g����Чֵ�ǣ�

* - \ ref WDT_RESET_DELAY_3CLK

* - \ ref WDT_RESET_DELAY_18CLK

* - \ ref WDT_RESET_DELAY_130CLK

* - \ ref WDT_RESET_DELAY_1026CLK

* @param [in] u32EnableReset����WDT��(f��)λϵ�y(t��ng)���ܡ���Чֵ��TRUE��FALSE

* @param [in] u32EnableWakeup����WDT����ϵ�y(t��ng)���ܡ���Чֵ��TRUE��FALSE

* @����?z��)o

* /

����(y��ng)�Ď캯��(sh��)�c����քe�ǣ�

#define WDT_TIMEOUT_2POW4 (0UL << WDT_CTL_WTIS_Pos) /*!< WDT setting for timeout interval = 2^4 * WDT clocks */ #define WDT_TIMEOUT_2POW6 (1UL << WDT_CTL_WTIS_Pos) /*!< WDT setting for timeout interval = 2^6 * WDT clocks */ #define WDT_TIMEOUT_2POW8 (2UL << WDT_CTL_WTIS_Pos) /*!< WDT setting for timeout interval = 2^8 * WDT clocks */ #define WDT_TIMEOUT_2POW10 (3UL << WDT_CTL_WTIS_Pos) /*!< WDT setting for timeout interval = 2^10 * WDT clocks */ #define WDT_TIMEOUT_2POW12 (4UL << WDT_CTL_WTIS_Pos) /*!< WDT setting for timeout interval = 2^12 * WDT clocks */ #define WDT_TIMEOUT_2POW14 (5UL << WDT_CTL_WTIS_Pos) /*!< WDT setting for timeout interval = 2^14 * WDT clocks */ #define WDT_TIMEOUT_2POW16 (6UL << WDT_CTL_WTIS_Pos) /*!< WDT setting for timeout interval = 2^16 * WDT clocks */ #define WDT_TIMEOUT_2POW18 (7UL << WDT_CTL_WTIS_Pos) /*!< WDT setting for timeout interval = 2^18 * WDT clocks */ #define WDT_RESET_DELAY_3CLK (3UL << WDT_CTL_WTRDSEL_Pos) /*!< WDT setting reset delay to 3 WDT clocks */ #define WDT_RESET_DELAY_18CLK (2UL << WDT_CTL_WTRDSEL_Pos) /*!< WDT setting reset delay to 18 WDT clocks */ #define WDT_RESET_DELAY_130CLK (1UL << WDT_CTL_WTRDSEL_Pos) /*!< WDT setting reset delay to 130 WDT clocks */ #define WDT_RESET_DELAY_1026CLK (0UL << WDT_CTL_WTRDSEL_Pos) /*!< WDT setting reset delay to 1026 WDT clocks */

�҂���һ���ڶ��䣺

��(d��ng)Ӌ(j��)��(sh��)���_(d��)���x��ij��r�g�������T�����r���Д���(bi��o)־W(w��ng)DT_IS������������λ����Ո��WDT �Д� (������T�����r���Д�ʹ��λWDT_IE ��λ)��ͬ�r�o�������r�¼�����һ��ָ�����ӕr���^ WTRDSEL �O(sh��)�ã��Ñ������ԓָ���ӕr�^��ǰ�O(sh��)��WTR (WDT_CTL[0]) (���T�����r����(f��)λ) ��߁��(f��)λ18 λ WDT Ӌ(j��)��(sh��)�����Է�ֹоƬ��(f��)λ��

Ո���Д�͵������Д࣬ʹ���Дࣺ

/**

* @brief This function enables the WDT time-out interrupt

* @param None

* @return None

*/

__STATIC_INLINE void WDT_EnableInt(void)

{

WDT->IER = WDT_IER_IE_Msk;

return;

}/**

\brief Enable External Interrupt

\details Enables a device-specific interrupt in the NVIC interrupt controller.

\param [in] IRQn External interrupt number. Value cannot be negative.

*/

__STATIC_INLINE void NVIC_EnableIRQ(IRQn_Type IRQn)

{

NVIC->ISER[0U] = (uint32_t)(1UL << (((uint32_t)(int32_t)IRQn) & 0x1FUL));

}

�@�ɂ��Д࣬һ����WDTʹ���Д࣬һ�����ⲿ�Дࡣ�҂�߀Ҫ���ö��r���M(j��n)��ι�����������^ι����

void WDT_IRQHandler(void)

{

// Clear WDT interrupt flag

WDT_CLEAR_TIMEOUT_INT_FLAG();

// Check WDT wake up flag

if(WDT_GET_TIMEOUT_WAKEUP_FLAG()) {

printf("Wake up by WDT\n");

// Clear WDT wake up flag

WDT_CLEAR_TIMEOUT_WAKEUP_FLAG();

}

}

�@�����漰�Ď캯��(sh��)�������@Щ���������Ƿ������ˣ�

#define WDT_ISR_WAKE_IS_Msk (0x1ul << WDT_ISR_WAKE_IS_Pos) /*!< WDT_T::ISR: WAKE_IS Mask */

#define WDT_GET_TIMEOUT_WAKEUP_FLAG() (WDT->ISR & WDT_ISR_WAKE_IS_Msk ? 1 : 0)

#define WDT_CLEAR_TIMEOUT_WAKEUP_FLAG() (WDT->ISR = WDT_ISR_WAKE_IS_Msk)

��ô�������c��������@һ�䣬WDT_RST_IS ���������T����(f��)λ���㡣�Ñ�����ܛ��݆ԃWDT_RST_IS ���R�e��(f��)λԴ�Ƿ�WDT��

Ȼ���Ͻ�������ˣ��������ψ���

/******************************************************************************

* @file main.c

* @version V1.00

* $Revision: 3 $

* $Date: 14/09/11 7:39p $

* @brief Use WDT to wake up system from Power-down mode periodically.

*

* @note

* Copyright (C) 2013-2014 Nuvoton Technology Corp. All rights reserved.

*****************************************************************************/

#include <stdio.h>

#include "Nano100Series.h"

void WDT_IRQHandler(void)

{

// Clear WDT interrupt flag

WDT_CLEAR_TIMEOUT_INT_FLAG();

// Check WDT wake up flag

if(WDT_GET_TIMEOUT_WAKEUP_FLAG()) {

printf("Wake up by WDT\n");

// Clear WDT wake up flag

WDT_CLEAR_TIMEOUT_WAKEUP_FLAG();

}

}

void SYS_Init(void)

{

/*---------------------------------------------------------------------------------------------------------*/

/* Init System Clock */

/*---------------------------------------------------------------------------------------------------------*/

/* Unlock protected registers */

SYS_UnlockReg();

/* Enable External XTAL (4~24 MHz) */

CLK_EnableXtalRC(CLK_PWRCTL_HXT_EN_Msk);

/* Enable LIRC */

CLK_EnableXtalRC(CLK_PWRCTL_LIRC_EN_Msk);

/* Waiting for 12MHz clock ready */

CLK_WaitClockReady( CLK_CLKSTATUS_HXT_STB_Msk);

/* Waiting for LIRC clock ready */

CLK_WaitClockReady( CLK_CLKSTATUS_LIRC_STB_Msk);

/* Switch HCLK clock source to HXT */

CLK_SetHCLK(CLK_CLKSEL0_HCLK_S_HXT,CLK_HCLK_CLK_DIVIDER(1));

/* Enable IP clock */

CLK_EnableModuleClock(UART0_MODULE);

CLK_EnableModuleClock(WDT_MODULE);

/* Select IP clock source */

CLK_SetModuleClock(UART0_MODULE, CLK_CLKSEL1_UART_S_HXT, CLK_UART_CLK_DIVIDER(1));

CLK_SetModuleClock(WDT_MODULE, 0, 0);

/* Update System Core Clock */

/* User can use SystemCoreClockUpdate() to calculate SystemCoreClock. */

SystemCoreClockUpdate();

/*---------------------------------------------------------------------------------------------------------*/

/* Init I/O Multi-function */

/*---------------------------------------------------------------------------------------------------------*/

/* Set GPB multi-function pins for UART0 RXD and TXD */

SYS->PB_L_MFP &= ~(SYS_PB_L_MFP_PB0_MFP_Msk | SYS_PB_L_MFP_PB1_MFP_Msk);

SYS->PB_L_MFP |= (SYS_PB_L_MFP_PB1_MFP_UART0_TX | SYS_PB_L_MFP_PB0_MFP_UART0_RX);

/* Lock protected registers */

SYS_LockReg();

}

int32_t main (void)

{

/* Init System, IP clock and multi-function I/O

In the end of SYS_Init() will issue SYS_LockReg()

to lock protected register. If user want to write

protected register, please issue SYS_UnlockReg()

to unlock protected register if necessary */

SYS_Init();

/* Init UART to 115200-8n1 for print message */

UART_Open(UART0, 115200);

printf("\nThis sample code demonstrate using WDT to wake system up from power down mode\n");

// WDT register is locked, so it is necessary to unlock protect register before configure WDT

SYS_UnlockReg();

// WDT timeout every 2^14 WDT clock, disable system reset, enable wake up system

WDT_Open(WDT_TIMEOUT_2POW14, 0, FALSE, TRUE);

// Enable WDT timeout interrupt

WDT_EnableInt();

NVIC_EnableIRQ(WDT_IRQn);

while(1) {

// Wait 'til UART FIFO empty to get a cleaner console out

while(!UART_IS_TX_EMPTY(UART0));

CLK_PowerDown();

}

}

/*** (C) COPYRIGHT 2014 Nuvoton Technology Corp. ***/�@����߀��һЩ�қ]���v��̫��������ģ��ҕ���λ��������ģ��ҕ�����ȥ�������gӭ����ָ�c(di��n)

ʧ������������Ҳ���������dž�ʧ�����źͶ�־��ֻ�����S�����h(yu��n)Ҋ����̫ꖡ�����������һ�����������ӣ����lj��с��ĕr�s�l(f��)�F(xi��n)�Լ�һ�o���У�Ҫ��õ���߀���^�m(x��)���ܡ�

�ߴa�P(gu��n)ע�҂�

�]�䣺ivy@yingtexin.net

��ַ�����������A�^(q��)���νֵ����δ��973�f�����S��(chu��ng)�I(y��)�@A��2��A09