─·║├Ż¼ÜgėŁ▀M(j©¼n)╚ļ╔Ņ█┌╩ąĘf╠žą┬┐Ų╝╝ėąŽ▐╣½╦Š╣┘ĘĮŠW(w©Żng)šŠŻĪ

─·║├Ż¼ÜgėŁ▀M(j©¼n)╚ļ╔Ņ█┌╩ąĘf╠žą┬┐Ų╝╝ėąŽ▐╣½╦Š╣┘ĘĮŠW(w©Żng)šŠŻĪ

1.ā╚(n©©i)║╦ųT╚ń51/ARM/90/PIC/AVR.....ėą║├ČÓĘNĄ─,║╬ørā╚(n©©i)║╦Å─üĒ(l©ói)▓╗ĘųŅÉ,ę“?y©żn)ķ├┐ę╗╝ę│ŻČ╝┐╔ęįĖ─ā?n©©i)║╦,─Ńæ¬(y©®ng)įōå¢(w©©n)Ą─╩Ū╝▄śŗ(g©░u)!!ų╗ėąČ«╝▄śŗ(g©░u)▓┼─▄ė├╩▓├┤Ų¼ūėČ╝±{▌pŠ═╩ņ. ╬ęįö╝Ü(x©¼)Ą─šf(shu©Ł)ę╗Ž┬░╔. HARVARD(╣■Ę)╝▄śŗ(g©░u):ROM(│╠ą“┐šķg)┼cRAM(öĄ(sh©┤)ō■(j©┤)┐šķg)Ęųķ_(k©Īi),▒Ńė┌│╠ą“┼cöĄ(sh©┤)ō■(j©┤)Ą─═¼Ģr(sh©¬)įLå¢(w©©n),£p╔┘│╠ą“▀\(y©┤n)ąąĢr(sh©¬)įLå¢(w©©n)Ą─Ų┐Ņi,╠ßĖ▀öĄ(sh©┤)ō■(j©┤)═╠═┬. PRINCETON(Ųš┴ų╦╣ŅD)╝▄śŗ(g©░u):▓╔ė├═©ė├ėŗ(j©¼)╦ŃÖC(j©®)ÅVĘ║╩╣ė├Ą─ROMRAM║ŽČ■×ķę╗Ą─ĘĮ╩Į,Š═╩Ū▒Ŗ╦∙ų▄ų¬Ą─±TųZę└┬³ĮY(ji©”)śŗ(g©░u),│╠ą“ųĖ┴Ņ┤µā”(ch©│)ĄžųĘ║═öĄ(sh©┤)ō■(j©┤)ųĖ┴Ņ┤µā”(ch©│)ĄžųĘųĖŽ“═¼ę╗┤µā”(ch©│)Ų„▓╗═¼╬╗ų├,ę“┤╦│╠ą“ųĖ┴Ņ║═öĄ(sh©┤)ō■(j©┤)Ą─īÆČ╚ŽÓ═¼. ┼e└²šf(shu©Ł)├„:ęįėó╠žĀ¢×ķ└²:MCS-51ė├Ą─╩Ū╣■Ę╝▄śŗ(g©░u),Č°║¾╝░«a(ch©Żn)ŲĘ16╬╗Ą─MCS-96Š═╩ŪŲš┴ų╦╣ŅD╝▄śŗ(g©░u).ARM╣½╦Š┘uĄ─ā╚(n©©i)║╦Äū║§ČÓ╩Ū╣■Ę╝▄śŗ(g©░u)Ą─.

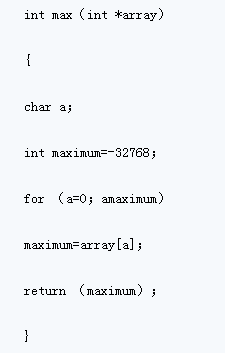

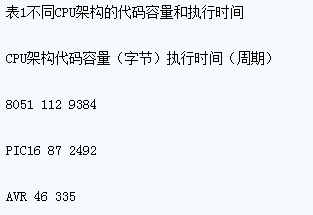

2.šł(q©½ng)å¢(w©©n)PICå╬Ų¼ÖC(j©®)║═AVRå╬Ų¼ÖC(j©®)╩Ū51ā╚(n©©i)║╦Ą─å߯┐

▓╗╩Ū,Č╝ėąūį╝║Ą─CŠÄūgŁh(hu©ón)Š│

3.STC51å╬Ų¼ÖC(j©®)║═AT89S51Ą─ģRŠÄšZ(y©│)čįę╗śėå߯┐

ā╚(n©©i)║╦║═ųĖ┴Ņ╝»Č╝╩Ūę╗śėĄ─Ż¼ ╦∙ęįĘ┼ą─Ż¼┴Ē═ŌĮ©ūh─ŃŠÄ▌ŗĄ─Ģr(sh©¬)║“╚ń╣¹ī”(du©¼)ł╠(zh©¬)ąąĢr(sh©¬)ķgę¬Ū¾▓╗╩Ū║▄┐┴┐╠Ą─įÆŻ¼▒M┴┐╩╣ė├CšZ(y©│)čįŻ¼«ģŠ╣═©ė├ąį║├Ūę▒╚▌^║å(ji©Żn)å╬

Ą½ģRŠÄ│╠ą“ę▓ę¬Ģ■(hu©¼)░ĪŻĪ▀@éĆ(g©©)┐╔ęįų▒Įė┼cąŠŲ¼Į╗┴„čĮŻĪ

4.AVRå╬Ų¼ÖC(j©®)╩Ū╩▓├┤ā╚(n©©i)║╦Ż┐

┤Ż║AVRå╬Ų¼ÖC(j©®)ā╚(n©©i)║╦Š═╩ŪAVRā╚(n©©i)║╦Ż¼║═51ā╚(n©©i)║╦╩Ū▓╗ę╗śėĄ─Ż¼╚ń╣¹ā╚(n©©i)║╦ę╗śėĄ─įÆŻ¼─Ū╦³Ą─ģRŠÄųĖ┴Ņæ¬(y©®ng)įō╩Ūę╗śėĄ─Ż¼īŹ(sh©¬)ļH╔Ž╦¹éāĄ─ģRŠÄųĖ┴Ņ╩Ū

═Ļ╚½▓╗ę╗śėĄ─ĪŻAVR╩Ū├└ć°(gu©«)ATMEL╣½╦Ščą░l(f©Ī)Ą─Ż¼ATMEL╣½╦Šėą╚²┤¾ŽĄ┴ąMCUŻ¼ę╗ĘN╩Ū└Ž╩ĮĄ─ęį8051ā╚(n©©i)║╦Ą─å╬Ų¼ÖC(j©®)Ż¼Ą┌Č■ĘN╩Ū─┐Ū░┤¾┴┐╩╣ė├

Ą─ęįAVRā╚(n©©i)║╦Ą─AVRå╬Ų¼ÖC(j©®)ĪŻĄ┌╚²ĘN╩Ū─┐Ū░Ė▀Č╦Ą─ęįARMā╚(n©©i)║╦Ą─╬ó╠Ä└ĒŲ„ĪŻARMęčĮø(j©®ng)▓╗╩Ūå╬Ų¼ÖC(j©®)─Ū├┤║å(ji©Żn)å╬Ą─Ė┼─Ņ┴╦Ż¼▓Ņ▓╗ČÓĖ·ļŖ─XCPUŅÉ╦Ų

┴╦ĪŻ¼F(xi©żn)į┌╩ųÖC(j©®)╔ŽĄ─CPUŠ═╩ŪAVRĄ─ĪŻ

5.51ŽĄ┴ąå╬Ų¼ÖC(j©®)Ą─ģ^(q©▒)äe┼c╠ž³c(di©Żn)ĮķĮB

8031/8051/8751╩ŪIntel╣½╦ŠįńŲ┌Ą─«a(ch©Żn)ŲĘĪŻ

1Īó8031Ą─╠ž³c(di©Żn)

8031Ų¼ā╚(n©©i)▓╗Ħ│╠ą“┤µā”(ch©│)Ų„ROMŻ¼╩╣ė├Ģr(sh©¬)ė├æ¶ąĶ═ŌĮė│╠ą“┤µā”(ch©│)Ų„║═ę╗Ų¼▀ē▌ŗļŖ┬Ę373Ż¼═ŌĮėĄ─│╠ą“┤µā”(ch©│)Ų„ČÓ×ķEPROMĄ─2764ŽĄ┴ąĪŻė├æ¶╚¶Žļī”(du©¼)īæ╚ļĄĮEPROMųąĄ─│╠ą“▀M(j©¼n)ąąą▐Ė─Ż¼▒žĒÜŽ╚ė├ę╗ĘN╠ž╩ŌĄ─ūŽ═ŌŠĆ¤¶īóŲõšš╔õ▓┴│²Ż¼ų«║¾į┘┐╔īæ╚ļĪŻīæ╚ļĄĮ═ŌĮė│╠ą“┤µā”(ch©│)Ų„Ą─│╠ą“┤·┤aø](m©”i)ėą╩▓├┤▒Ż├▄ąį┐╔čįĪŻ

2Īó8051Ą─╠ž³c(di©Żn)

8051Ų¼ā╚(n©©i)ėą4k ROMŻ¼¤o(w©▓)ĒÜ═ŌĮė═Ō┤µā”(ch©│)Ų„║═373Ż¼Ė³─▄¾w¼F(xi©żn)“å╬Ų¼”Ą─║å(ji©Żn)ŠÜĪŻĄ½╩Ū─ŃŠÄĄ─│╠ą“─Ѥo(w©▓)Ę©¤²īæĄĮŲõROMųąŻ¼ų╗ėąīó│╠ą“Į╗ąŠŲ¼ÅS┤·─Ѥ²īæŻ¼▓ó╩Ūę╗┤╬ąįĄ─Ż¼Į±║¾─Ń║═ąŠŲ¼ÅSČ╝▓╗─▄Ė─īæŲõā╚(n©©i)╚▌ĪŻ

3Īó8751Ą─╠ž³c(di©Żn)

8751┼c8051╗∙▒Šę╗śėŻ¼Ą½8751Ų¼ā╚(n©©i)ėą4kĄ─EPROMŻ¼ė├æ¶┐╔ęįīóūį╝║ŠÄīæĄ─│╠ą“?q©▒)æ╚ļå╬Ų¼ÖC(j©®)Ą─EPROMųą▀M(j©¼n)ąą¼F(xi©żn)ł÷(ch©Żng)īŹ(sh©¬)“×(y©żn)┼cæ¬(y©®ng)ė├Ż¼EPROMĄ─Ė─īæ═¼śėąĶę¬ė├ūŽ═ŌŠĆ¤¶šš╔õę╗Č©Ģr(sh©¬)ķg▓┴│²║¾į┘¤²īæĪŻ

ė╔ė┌╔Ž╩÷ŅÉą═Ą─å╬Ų¼ÖC(j©®)æ¬(y©®ng)ė├Ą─įńŻ¼ė░Ēæ║▄┤¾Ż¼ęč│╔×ķ╩┬īŹ(sh©¬)╔ŽĄ─╣żśI(y©©)ś╦(bi©Īo)£╩(zh©│n)ĪŻ║¾üĒ(l©ói)║▄ČÓąŠŲ¼ÅS╔╠ęįĖ„ĘNĘĮ╩Į┼cIntel╣½╦Š║Žū„Ż¼ę▓═Ų│÷┴╦═¼ŅÉą═Ą─å╬Ų¼ÖC(j©®)Ż¼╚ń═¼ę╗ĘNå╬Ų¼ÖC(j©®)Ą─ČÓéĆ(g©©)░µ▒Šę╗śėŻ¼ļmČ╝į┌▓╗öÓĄ─Ė─ūāųŲįņ╣ż╦ćŻ¼Ą½ā╚(n©©i)║╦ģsę╗śėŻ¼ę▓Š═╩Ūšf(shu©Ł)▀@ŅÉå╬Ų¼ÖC(j©®)ųĖ┴ŅŽĄĮy(t©»ng)═Ļ╚½╝µ╚▌Ż¼Į^┤¾ČÓöĄ(sh©┤)╣▄─_ę▓╝µ╚▌Ż╗į┌╩╣ė├╔Ž╗∙▒Š┐╔ęįų▒Įė╗źōQĪŻ╚╦éāĮy(t©»ng)ĘQ▀@ą®┼c8051ā╚(n©©i)║╦ŽÓ═¼Ą─å╬Ų¼ÖC(j©®)×ķ“51ŽĄ┴ąå╬Ų¼ÖC(j©®)”Ż¼īW(xu©”)┴╦Ųõųąę╗ĘNŻ¼▒ŃĢ■(hu©¼)╦∙ėąĄ─51ŽĄ┴ąĪŻ

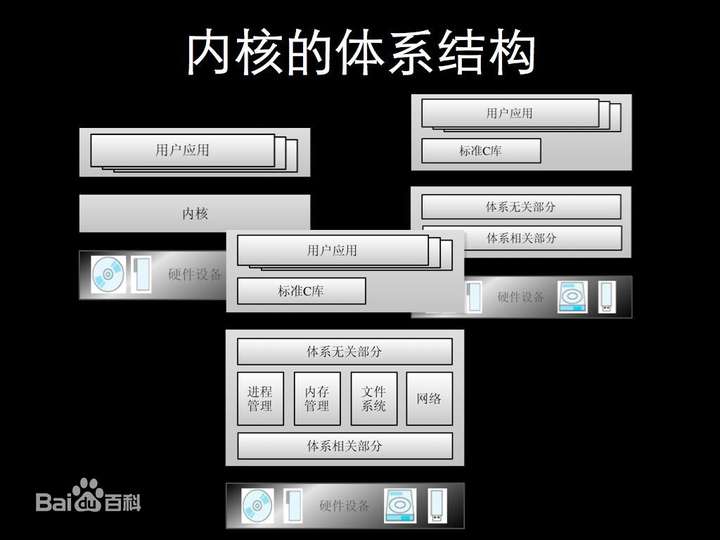

6.ā╚(n©©i)║╦░³║¼ųąčļ▀\(y©┤n)╦Ńå╬į¬+ā╚(n©©i)▓┐┐éŠĆ+ųĖ┴ŅĮŌ╬÷+..........,ā╚(n©©i)║╦ėą║▄ČÓųąŻ¼8051Ż¼ArmŻ¼MipsŻ¼power PCŻ¼▀@ą®Č╝╩Ū┤·▒Ē╚╦╬’Ż¼▀Ćėą║▄ČÓŻ¼║▄ČÓ

ā╚(n©©i)║╦╩Ū▄ø╝■╗“š▀ė▓╝■Ą─╗∙▒Š║╦ą─▓┐ĘųŻ¼┐╔ęį░³║¼▄ø╝■║═ė▓╝■ĪŻ╚ńLINUXĄ─ā╚(n©©i)║╦Š═╩Ū▄ø╝■Ą─Ż¼╩ŪLINUXūŅ╗∙▒ŠĄ─▓┐ĘųŻ¼Ųõ╦¹▄ø╝■╩Ūį┌ā╚(n©©i)║╦Ą─╗∙ĄA(ch©│)╔Ž░l(f©Ī)š╣ĪŻ51ā╚(n©©i)║╦╩Ū51ŽĄ┴ą╝µ╚▌ÖC(j©®)Ą─╗∙▒Š▓┐ĘųĪŻ░³║¼ųĖ┴ŅŽĄĮy(t©»ng)Īó║═╗∙▒ŠĄ─ė▓╝■Ż¼╚ńā╚(n©©i)┤µĮY(ji©”)śŗ(g©░u)Ą╚ĪŻŲõ╦¹į÷ÅŖ(qi©óng)ą═51å╬Ų¼ÖC(j©®)Ż¼Š═╩Ūį┌ā╚(n©©i)║╦Ą─╗∙ĄA(ch©│)╔ŽöU(ku©░)š╣╣”─▄ĪŻ

ŽĄĮy(t©»ng)ąį─▄▓ó▓╗Ą╚ār(ji©ż)ė┌ėŗ(j©¼)╦Ń─▄┴”ĪŻ▌^Ą═Ą─╣”║─ĪóžSĖ╗Ą─Ų¼ā╚(n©©i)═ŌįO(sh©©)ęį╝░īŹ(sh©¬)Ģr(sh©¬)Ą─ą┼╠¢(h©żo)╠Ä└Ē─▄┴”ī”(du©¼)ė┌┤¾▓┐ĘųŪČ╚ļ╩Įæ¬(y©®ng)ė├üĒ(l©ói)šf(shu©Ł)╩ŪūŅ×ķųžę¬Ą─ĪŻé„Įy(t©»ng)Ą─8╬╗Īó16╬╗å╬Ų¼ÖC(j©®)ęčĮø(j©®ng)║▄║├Ą─╠Ä└Ē┴╦▀@ŅÉå¢(w©©n)Ņ}Ż¼Ą½╩ŪļSų°«ö(d©Īng)Į±ŪČ╚ļ╩ĮįO(sh©©)ėŗ(j©¼)▓╗öÓį÷ķL(zh©Żng)Ą─╣”─▄ąĶŪ¾║═╠ž╩Ōę¬Ū¾Ż¼įSČÓ╬ó┐žųŲŲ„ÅS╔╠ķ_(k©Īi)╩╝ÆüŚē╦¹éāé„Įy(t©»ng)Ą─8╬╗Īó16╬╗å╬Ų¼ÖC(j©®)ĪŻĄ½╩Ū▀xō±32╬╗╠Ä└ĒŲ„ī”(du©¼)ė┌─│ą®╚╬äš(w©┤)üĒ(l©ói)┐╔─▄▓ó▓╗╩ŪūŅ▀mę╦Ą─ĪŻŽ┬├µ╬ęéāŠ═ėæšōę╗Ž┬å╬Ų¼ÖC(j©®)Ą─▀xą═å¢(w©©n)Ņ}ĪŻ

└ĒĮŌŽĄĮy(t©»ng)ąį─▄

MIPSŻ©million instructions per secondŻ®Ż¼╩Ū╬ó┐žųŲŲ„ėŗ(j©¼)╦Ń─▄┴”Ą─▒Ēš„ĪŻĄ½╩ŪŻ¼╦∙ėąĄ─ŪČ╚ļ╩Įæ¬(y©®ng)ė├▓╗āHāH╩ŪąĶę¬ėŗ(j©¼)╦Ń─▄┴”Ż¼╦∙ęįæ¬(y©®ng)ė├Ą─ČÓśė╗»øQČ©┴╦ŽĄĮy(t©»ng)ąį─▄║Ō┴┐ĘĮ╩ĮĄ─ČÓśė╗»Ż¼┤¾▓┐ĘųģóöĄ(sh©┤)Č╝═¼Ą╚ųžę¬▓óŪęļyė┌ė├ę╗éĆ(g©©)ģóöĄ(sh©┤)üĒ(l©ói)▒Ē╩ŠŻ¼╬ęéā▓ó▓╗æ¬(y©®ng)įōāHāHÅ─MIPSŠ═┼ąČ©ŽĄĮy(t©»ng)Ą─║├ē─ĪŻę▓įS─│ę╗æ¬(y©®ng)ė├ė╔ė┌│╔▒ŠĄ─Ž▐ųŲŻ¼ąĶę¬ę╗┐ŅĖ▀╝»│╔Č╚Ą─╬ó┐žųŲŲ„Ż¼įō┐žųŲŲ„ąĶę¬ČÓéĆ(g©©)Č©Ģr(sh©¬)Ų„║═ČÓĘNĮė┐┌ĪŻĄ½╩Ū┴Ēę╗éĆ(g©©)æ¬(y©®ng)ė├ąĶę¬Ė▀Ą─Š½Č╚║═┐ņ╦┘Ą──ŻöM▐D(zhu©Żn)ōQ─▄┴”ĪŻā╔š▀Ą─╣▓═¼³c(di©Żn)┐╔─▄āHāH╩Ū╣®ļŖ▓┐ĘųŻ¼▒╚╚ń▓╔ė├ļŖ│ž╣®ļŖĪŻī”(du©¼)ė┌ę╗éĆ(g©©)īŹ(sh©¬)Ģr(sh©¬)Ą─Ēśą“╠Ä└Ēæ¬(y©®ng)ė├üĒ(l©ói)šf(shu©Ł)Ż¼═©ą┼Ą─╩¦öĪ┐╔─▄Ģ■(hu©¼)ī¦(d©Żo)ų┬×─(z©Īi)ļyąį║¾╣¹ĪŻ▀@śėĄ─ł÷(ch©Żng)║ŽŽ┬Š═ąĶę¬ę╗éĆ(g©©)ņ`Ū╔Ą─┐žųŲŲ„ĪŻ▀@éĆ(g©©)┐žųŲŲ„æ¬(y©®ng)«ö(d©Īng)─▄ē“ęįš²┤_Ą─Ēśą“╠Ä└Ē╚╬äš(w©┤)Ż¼▓óŪęĒææ¬(y©®ng)Ģr(sh©¬)ķg▒žĒÜŠ∙║ŌĪŻ╦∙ėą╔Ž╩÷æ¬(y©®ng)ė├Ą─╣▓═¼å¢(w©©n)Ņ}┐╔─▄Š═╩ŪČ©Ų┌Ą─¼F(xi©żn)ł÷(ch©Żng)╔²╝ē(j©¬)─▄┴”ĪŻ

│²┴╦┼cŠ▀¾wĄ─«a(ch©Żn)ŲĘę¬Ū¾ėąĻP(gu©Īn)═ŌŻ¼ŽĄĮy(t©»ng)ąį─▄Ą─║Ō┴┐ę▓┐╔ęį┐╝æ]╩Ūʱėą╚▌ęū╔Ž╩ųĪó╚▌ęū╩╣ė├Ą─ķ_(k©Īi)░l(f©Ī)╣żŠ▀Īóæ¬(y©®ng)ė├╩Š└²Īó²R╚½Ą─╬─Ön║═Ė▀ą¦Ą─ų¦│ųŠW(w©Żng)Įj(lu©░)ĪŻ

ŽĄĮy(t©»ng)ąį─▄Ą─ŽÓĻP(gu©Īn)å¢(w©©n)Ņ}

1.é„Įy(t©»ng)8╬╗å╬Ų¼ÖC(j©®)Ą─ŠųŽ▐

┤¾ČÓöĄ(sh©┤)╣ż│╠Ĥ╩«ĘųĻP(gu©Īn)ūóŽĄĮy(t©»ng)ąį─▄Ż¼ę“?y©żn)ķįĮü?l©ói)įĮČÓĄ─8╬╗║═16╬╗å╬Ų¼ÖC(j©®)╝ęūÕęčĮø(j©®ng)¤o(w©▓)Ę©ØMūŃ«ö(d©Īng)Į±╚šęµį÷ķL(zh©Żng)Ą─ąĶŪ¾ĪŻĻÉ┼f║═Ą═ą¦Ą─╝▄śŗ(g©░u)Ž▐ųŲ┴╦╠Ä└Ē─▄┴”Īó┤µā”(ch©│)Ų„╚▌┴┐Īó═ŌįO(sh©©)╠Ä└Ē║═Ą═╣”║─ę¬Ū¾ĪŻ8╬╗Ą─╠Ä└ĒŲ„╝▄śŗ(g©░u)Ż¼▒╚╚ń8051ĪóPIC14ĪóPIC16ĪóPIC18Īó78K0║═HC08╩Ūį┌Ė▀╝ē(j©¬)šZ(y©│)čįŻ©▒╚╚ńCšZ(y©│)čįŻ®│÷¼F(xi©żn)ų«Ū░ķ_(k©Īi)░l(f©Ī)Ą─Ż¼ŲõųĖ┴Ņ╝»āHė├ė┌ģRŠÄķ_(k©Īi)░l(f©Ī)Łh(hu©ón)Š│ĪŻ▓óŪę▀@ŅÉ╝▄śŗ(g©░u)Ą─ųąčļ╠Ä└Ēå╬į¬Ż©CPUsŻ®╚▒Ę”ę╗ą®ĻP(gu©Īn)µI╣”─▄Ż¼▒╚╚ń16╬╗Ą─╦ŃöĄ(sh©┤)▀\(y©┤n)╦Ńų¦│ųĪóŚl╝■╠°▐D(zhu©Żn)║═┤µā”(ch©│)Ų„ųĖßśĪŻ

įSČÓCPU╝▄śŗ(g©░u)ł╠(zh©¬)ąąę╗ŚlųĖ┴ŅąĶę¬╚¶Ė╔Ģr(sh©¬)ńŖų▄Ų┌ĪŻMicrochipĄ─8╬╗PIC╝ęūÕł╠(zh©¬)ąąę╗ŚlūŅ║å(ji©Żn)å╬Ą─ųĖ┴ŅąĶę¬4éĆ(g©©)Ģr(sh©¬)ńŖų▄Ų┌Ż¼▀@ī¦(d©Żo)ų┬╩╣ė├20MĄ─Ģr(sh©¬)ńŖāH─▄▀_(d©ó)ĄĮ5MIPS.ī”(du©¼)ė┌Ųõ╦¹CPU╝▄śŗ(g©░u)Ż¼▒╚╚ń8051ā╚(n©©i)║╦ĪŻŲõł╠(zh©¬)ąąę╗ŚlųĖ┴Ņų┴╔┘ąĶę¬6éĆ(g©©)Ģr(sh©¬)ńŖų▄Ų┌Ż¼▀@Š═╩╣Ą├īŹ(sh©¬)ļHĄ─MIPSę¬▒╚ĮoČ©Ą─Ģr(sh©¬)ńŖŅl┬╩Ą═║▄ČÓĪŻ

╔Ž╩÷┤·┤a╩Ūę╗éĆ(g©©)║å(ji©Żn)å╬Ą─CšZ(y©│)čį║»öĄ(sh©┤)Ż¼▒Ē1┴ą│÷┴╦į┌╚²ĘN▓╗═¼CPU╝▄śŗ(g©░u)╔ŽŠÄūg▀@Č╬┤·┤aĄ─ŽÓæ¬(y©®ng)ĮY(ji©”)╣¹ĪŻ8051ā╚(n©©i)║╦Ą─ł╠(zh©¬)ąąĢr(sh©¬)ķgÄū║§╩ŪPIC16ā╚(n©©i)║╦Ą─4▒ČŻ¼ī”(du©¼)ė┌AVR╝▄śŗ(g©░u)Ė³╩Ū▀_(d©ó)ĄĮ┴╦28▒ČĪŻ

ę╗ą®░ļī¦(d©Żo)¾wÅS╔╠ĮŌøQ┴╦Ģr(sh©¬)ńŖĘų┼õå¢(w©©n)Ņ}Ż¼╩╣Ą├╬ó┐žųŲŲ„īŹ(sh©¬)¼F(xi©żn)┴╦å╬Ģr(sh©¬)ńŖų▄Ų┌ųĖ┴ŅĪŻ«ö(d©Īng)Ģr(sh©¬)ńŖŅl┬╩×ķ100MHzĢr(sh©¬)Ż¼Silicon Labs┬ĢĘQ╦¹éā╗∙ė┌8╬╗8051╝▄śŗ(g©░u)Ą─╬ó┐žųŲŲ„─▄ē“▀_(d©ó)ĄĮ100MIPSĄ─ĘÕųĄĪŻĄ½╩ŪŻ¼▀@└’ėąÄūéĆ(g©©)å¢(w©©n)Ņ}Ż║

Ą┌ę╗Ż¼ė╔ė┌┤¾▓┐ĘųųĖ┴ŅąĶę¬ā╔éĆ(g©©)Ģr(sh©¬)ńŖų▄Ų┌╔§ų┴Ė³ČÓŻ¼╦∙ęįŲõīŹ(sh©¬)ļH─▄┴”ĮėĮ³ė┌50MIPSŻ╗

Ą┌Č■Ż¼8051╩Ū╗∙ė┌└█╝ėŲ„Ą─CPUŻ¼╦∙ėąąĶę¬ėŗ(j©¼)╦ŃĄ─öĄ(sh©┤)ō■(j©┤)▒žĒÜ┐ĮžÉĄĮ└█╝ėŲ„ĪŻ▓ķ┐┤8051╠Ä└ĒŲ„Ą─ģRŠÄ┤·┤aŻ¼┐╔ęį░l(f©Ī)¼F(xi©żn)65%-70%Ą─ųĖ┴Ņė├üĒ(l©ói)ęŲäė(d©░ng)öĄ(sh©┤)ō■(j©┤)ĪŻė╔ė┌¼F(xi©żn)┤·8╬╗║═16╬╗å╬Ų¼ÖC(j©®)╝▄śŗ(g©░u)ųąėąę╗ŽĄ┴ą║═╦Ńąg(sh©┤)▀ē▌ŗå╬į¬Ż©ALUŻ®ŽÓ▀BĄ─╝─┤µŲ„ĪŻę“┤╦Ż¼8051ā╚(n©©i)║╦Ą─50MIPSāHŽÓ«ö(d©Īng)ė┌¼F(xi©żn)┤·8╬╗║═16╬╗å╬Ų¼ÖC(j©®)╝▄śŗ(g©░u)Ą─15MIPS.

Ą┌╚²Ż¼▌^└ŽĄ─CPU╝▄śŗ(g©░u)╚▒Ę”ī”(du©¼)┤¾╚▌┴┐┤µā”(ch©│)Ų„Ą─ų¦│ųĪŻįńį┌Ų▀╩«─Ļ┤·Ż¼║▄ļyŽļŽ¾ąĶę¬│¼▀^(gu©░)64KB┤µā”(ch©│)Ų„Ą─ŪČ╚ļ╩Įæ¬(y©®ng)ė├Ż¼▀@╩╣Ą├įSČÓCPUįO(sh©©)ėŗ(j©¼)Ĥ▀xō±16╬╗Ą─ĄžųĘ┐éŠĆĪŻę“┤╦Ż¼CPUĪó╝─┤µŲ„ĪóųĖ┴Ņ╝»ęį╝░│╠ą“┤µā”(ch©│)Ų„║═öĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)Ų„Ą─öĄ(sh©┤)ō■(j©┤)┐éŠĆ╩╝ĮK╩▄┤╦Ž▐ųŲĪŻ

Ą┌╦─Ż¼į┌2006─ĻŻ¼╝sėą9%Ą─8╬╗ŪČ╚ļ╩Įæ¬(y©®ng)ė├╩╣ė├┴╦64KB╔§ų┴Ė³ČÓĄ─│╠ą“┤µā”(ch©│)┐šķgŻ¼▀@┤·▒Ē┴╦8╬╗MCU╩ął÷(ch©Żng)26%Ą─╩šęµĪŻ═Ų£y(c©©)2009─ĻŻ¼14%Ą─8╬╗ŪČ╚ļ╩Įæ¬(y©®ng)ė├Ģ■(hu©¼)┤·▒Ē36%Ą─╩šęµĪŻČ°▀@14%Ą─æ¬(y©®ng)ė├Ģ■(hu©¼)╩╣ė├64KB╔§ų┴Ė³ČÓĄ─│╠ą“┤µā”(ch©│)┐šķgĪŻ

Å─ŽĄĮy(t©»ng)ąį─▄Ą─ĮŪČ╚üĒ(l©ói)┐┤Ż¼╦∙ėą▀@ą®╩╣Ą├▌^┼fĄ─8╬╗MCUųØu╩¦╚źĖé(j©¼ng)ĀÄ(zh©źng)┴”ĪŻ

2.▓╗▀mę╦32╬╗╠Ä└ĒŲ„Ą─ł÷(ch©Żng)║Ž

┼f╩ĮCPU╝▄śŗ(g©░u)¤o(w©▓)Ę©ØMūŃ«ö(d©Īng)Į±Ą─╩ął÷(ch©Żng)ąĶŪ¾Ż¼×ķ┴╦ĮŌøQ▀@éĆ(g©©)å¢(w©©n)Ņ}Ż¼įSČÓÅS╔╠╔²╝ē(j©¬)ų┴32╬╗Ą─╠Ä└ĒŲĮ┼_(t©ói)ĪŻī”(du©¼)ė┌ąĶę¬32╬╗╠Ä└Ē─▄┴”Ą─æ¬(y©®ng)ė├üĒ(l©ói)šf(shu©Ł)▀@¤o(w©▓)ę╔╩ŪūŅ░¶Ą─▀xō±Ż¼Ą½╩ŪįSČÓįO(sh©©)ėŗ(j©¼)Ĥ▐D(zhu©Żn)ōQĄĮ32╬╗ŲĮ┼_(t©ói)▓óĘŪūŅš²┤_Ą─▀xō±ĪŻ╩╣ė├32╬╗MCUüĒ(l©ói)ĮŌøQ8╬╗║═16╬╗å╬Ų¼ÖC(j©®)Ą─ūį╔ĒŽ▐ųŲīóĢ■(hu©¼)ī¦(d©Żo)ų┬▀^(gu©░)Ė▀Ą─│╔▒ŠĪŻ

┤¾▓┐Ęų32╬╗╬ó┐žųŲŲ„¤o(w©▓)Ę©╠ß╣®Ė▀╦┘ĪóĖ▀Ęų▒µ┬╩Ą──ŻöĄ(sh©┤)Ż©ADCŻ®▐D(zhu©Żn)ōQŻ¼EMCąį─▄═©│Ż▌^Ą═Ż¼ŪęESD▒Żūo(h©┤)▌^╚§ĪŻČ°8╬╗║═16╬╗å╬Ų¼ÖC(j©®)į┌▀@ą®ĘĮ├µā×(y©Łu)ä▌(sh©¼)├„’@ĪŻ┴Ē═ŌŻ¼ÅŖ(qi©óng)Ą─IO“ī(q©▒)äė(d©░ng)─▄┴”Ż¼┐╔╣®▀xō±Ą─ČÓĘNā╚(n©©i)▓┐Īó═Ō▓┐š±╩ÄŲ„Ż¼¤o(w©▓)ąĶ═Ō▓┐Ų„╝■Ą─Ų¼ā╚(n©©i)ļŖē║š{(di©żo)š¹Ų„Ą╚╩Ū8╬╗║═16╬╗å╬Ų¼ÖC(j©®)Ą─┴Ēę╗ą®ā×(y©Łu)³c(di©Żn)ĪŻ

’@╚╗Ż¼32╬╗CPU░³║¼▒╚╚╬║╬8╬╗║═16╬╗CPUČ╝ę¬ČÓĄ─öĄ(sh©┤)ūų▀ē▌ŗå╬į¬Ż¼▀@ī¦(d©Żo)ų┬┴╦Ė▀Ą─ųŲįņ│╔▒ŠĪŻļm╚╗╩╣ė├ę╗ą®╠ž╩ŌĄ─░ļī¦(d©Żo)¾w╣ż╦ć┐╔ęįĮĄĄ═│╔▒ŠŻ¼Ą½╩Ū▒ūČ╦╩ŪĢ■(hu©¼)ī¦(d©Żo)ų┬▌^Ė▀Ą─┬®ļŖ┴„║═ņoæB(t©żi)╣”║─ĪŻ─│ą®æ¬(y©®ng)ė├Ż¼Ž±╦«▒ĒĪó╚╝?x©¼)Ō▒ĒĪó╩š┘M(f©©i)╣½┬ĘļŖūėś╦(bi©Īo)║×Īó░▓╚½ŽĄĮy(t©»ng)Ą╚Ż¼į┌╦¹éā╔·├³Ų┌ųąĄ─┤¾▓┐ĘųĢr(sh©¬)ķgŻ¼CPU╠Äė┌╦»├▀─Ż╩ĮŻ¼╝┤×ķ═Żų╣?f©żn)ŅæB(t©żi)ĪŻ▀@ŅÉæ¬(y©®ng)ė├Ą─ļŖ│žē█├³▒žĒÜį┌5-10─ĻŻ¼╦∙ęį▀@ŪķørųąŻ¼▓╗┐╔─▄īóCPUÅ─8╬╗╗“š▀16╬╗╔²╝ē(j©¬)ų┴32╬╗╠Ä└ĒŲ„ĪŻ╚ń╣¹Žļę¬╠ß╔²ŽĄĮy(t©»ng)ąį─▄ų╗ėą▓╔ė├äeĄ─ĘĮĘ©ĪŻ

▀@└’ėąÄūéĆ(g©©)Č©┴xąĶ꬚f(shu©Ł)ę╗Ž┬Ż¼

═ŌįO(sh©©)Ż¼ŅÖ├¹╦╝┴xŻ¼Š═╩ŪICąŠŲ¼╦∙ĮėĄ──▄ē“┼cIC═©ą┼Ą─═Ō▓┐įO(sh©©)éõĪŻįńŲė╔ė┌IC╝»│╔╣ż╦ć▓╗░l(f©Ī)▀_(d©ó)Ż¼║▄ČÓ¢|╬„Č╝╩Ū═ŌįO(sh©©)Ą─Ż¼į┌┤╦ęįDSPąŠŲ¼×ķ└²Ż¼▒╚╚ńPWMĪóADCĪóCANĄ╚Ą╚Ż¼

įŁ▒ŠČ╝╩ŪąĶꬹŠŲ¼═ŌĮėĄ─Ż¼╝┤╩╣╩Ū¼F(xi©żn)į┌Ż¼╚į╚╗ėą¬Ü(d©▓)┴óĄ─ADCąŠŲ¼Ż¼▒╚╚ńADS8364Ą╚Ą╚Ż¼Ą½╩Ū¼F(xi©żn)į┌Ż¼PWMĪóADCĄ╚Ą╚¢|╬„Č╝ęčĮø(j©®ng)╝»│╔į┌DSPąŠŲ¼ā╚(n©©i)Ż¼«ö(d©Īng)╚╗Ż¼

¤o(w©▓)šō╚ń║╬Ż¼ąŠŲ¼┐é▀Ć╩ŪĢ■(hu©¼)ąĶę¬═ŌĮėę╗ą®įO(sh©©)éõīŹ(sh©¬)¼F(xi©żn)─│ĘNŽĄĮy(t©»ng)Ż¼×ķ┴╦┼c─Ūą®═ŌįO(sh©©)ŽÓģ^(q©▒)äeŻ¼Š═īó╝»│╔į┌ąŠŲ¼ā╚(n©©i)Ż¼Ą½╩Ūėų▓╗ī┘ė┌ąŠŲ¼▒Š╔ĒŻ©▒╚╚ńDSPŻ¼╩Ūę╗ĘN╬ó╠Ä└ĒŲ„Ż¼

ę“┤╦ąŠŲ¼ųą▓╗ī┘ė┌╬ó╠Ä└ĒŲ„Ą─▓┐ĘųČ╝╩Ū═ŌįO(sh©©)Ż®Ą─ĘQ×ķ“Ų¼╔Ž═ŌįO(sh©©)”ĪŻ

Ų¼ā╚(n©©i)Īó═ŌįO(sh©©)╩Ūā╔éĆ(g©©)Ė┼─ŅŻ¼Ų¼ā╚(n©©i)ųĖū÷│╔ąŠŲ¼Ą─╝»│╔ļŖ┬Ęā╚(n©©i)▓┐Ż¼║å(ji©Żn)ĘQŲ¼ā╚(n©©i)Ż╗═ŌįO(sh©©)╩Ū═Ō▓┐įO(sh©©)éõĄ─║å(ji©Żn)ĘQŻ¼╩ŪųĖ╝»│╔ļŖ┬ĘąŠŲ¼═Ō▓┐Ą─įO(sh©©)éõĪŻ╝»│╔ļŖ┬ĘąŠŲ¼┼c═Ō▓┐įO(sh©©)éõĄ─▀BĮėę╗░ŃąĶę¬īŻķTĄ─Įė┐┌ļŖ┬Ę║═┐éŠĆĄ─▀BĮėŻ©░³└©┐žųŲ┐éŠĆ┬ĘĪóĄžųĘ┐éŠĆ║═öĄ(sh©┤)ō■(j©┤)┐éŠĆĄ╚Ż®ĪŻ

ė╔ė┌┤¾ęÄ(gu©®)─Ż╝»│╔ļŖ┬ĘĄ─╝╝ąg(sh©┤)░l(f©Ī)š╣Ą├║▄┐ņŻ¼¼F(xi©żn)į┌įSČÓąŠŲ¼į┌ųŲįņĢr(sh©¬)ęčĮø(j©®ng)─▄ē“?q©▒)ó▓┐ĘųĮė┐┌ļŖ┬Ę║═┐éŠĆ╝»│╔ĄĮąŠŲ¼ā╚(n©©i)▓┐ĪŻī”(du©¼)ė┌▀@▓┐ĘųļŖ┬Ę┼cé„Įy(t©»ng)Ą─Įė┐┌ļŖ┬Ę║═┐éŠĆ╩Ūėąģ^(q©▒)äeĄ─Ż¼×ķ┴╦╝ėė┌ģ^(q©▒)äe┐╔ęįĘQų«×ķŲ¼ā╚(n©©i)═ŌįO(sh©©)Ż¼Ųõ║¼┴x╩Ūį┌╝»│╔ļŖ┬ĘąŠŲ¼ā╚(n©©i)▓┐╝»│╔Ą─ė├ė┌┼c═Ō▓┐įO(sh©©)éõ▀BĮėĄ─Įė┐┌ļŖ┬Ę║═┐éŠĆĪŻ

ę“┤╦Ż¼║å(ji©Żn)å╬Ą─šf(shu©Ł)Ż¼“Ų¼ā╚(n©©i)═ŌįO(sh©©)”╩ŪąŠŲ¼ā╚(n©©i)▓┐ė├ė┌┼c═Ō▓┐įO(sh©©)éõ▀BĮėĄ─Įė┐┌ļŖ┬Ę║═┐éŠĆĪŻ

Ž╚ĖĮ╔Žę╗Åłėŗ(j©¼)╦ŃÖC(j©®)ė▓╝■ĮM│╔łDŲ¼Ż║

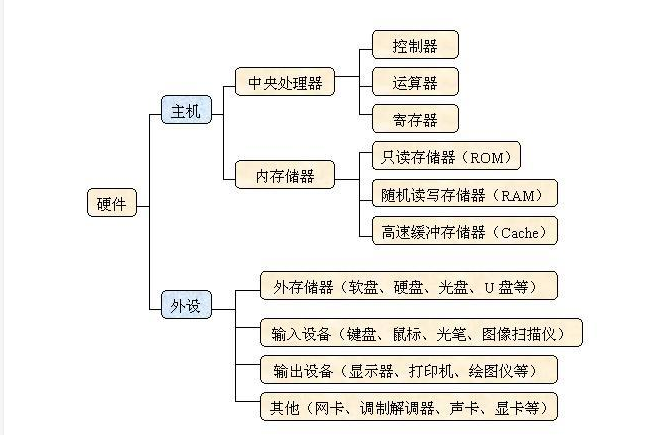

╝─┤µŲ„

╝─┤µŲ„╩Ūųąčļ╠Ä└ĒŲ„ā╚(n©©i)Ą─ĮM│╔▓┐Ę▌ĪŻ╦³Ė·CPUėąĻP(gu©Īn)ĪŻ╝─┤µŲ„╩ŪėąŽ▐┤µ┘A╚▌┴┐Ą─Ė▀╦┘┤µ┘A▓┐╝■Ż¼╦³éā┐╔ė├üĒ(l©ói)Ģ║┤µųĖ┴ŅĪóöĄ(sh©┤)ō■(j©┤)║═╬╗ųĘĪŻį┌ųąčļ╠Ä└ĒŲ„Ą─┐žųŲ▓┐╝■ųąŻ¼░³║¼Ą─╝─┤µŲ„ėąųĖ┴Ņ╝─┤µŲ„(IR)║═│╠ą“ėŗ(j©¼)öĄ(sh©┤)Ų„(PC)ĪŻį┌ųąčļ╠Ä└ĒŲ„Ą─╦Ńąg(sh©┤)╝░▀ē▌ŗ▓┐╝■ųąŻ¼░³║¼Ą─╝─┤µŲ„ėą└█╝ėŲ„(ACC)ĪŻ

┤µā”(ch©│)Ų„

┤µā”(ch©│)Ų„ĘČć·ūŅ┤¾Ż¼╦³Äū║§║Ł╔w┴╦╦∙ėąĻP(gu©Īn)ė┌┤µā”(ch©│)Ą─ĘČ«ĀĪŻ─Ń╦∙šf(shu©Ł)Ą─╝─┤µŲ„Ż¼ā╚(n©©i)┤µŻ¼Č╝╩Ū┤µā”(ch©│)Ų„└’├µĄ─ę╗ĘNĪŻĘ▓╩Ūėą┤µā”(ch©│)─▄┴”Ą─ė▓╝■Ż¼Č╝┐╔ęįĘQų«×ķ┤µā”(ch©│)Ų„Ż¼▀@╩Ūūį╚╗Ż¼ė▓▒PĖ³╝ė├„’@┴╦Ż¼╦³Üw╚ļ═Ō┤µā”(ch©│)Ų„ąą┴ąŻ¼ė╔┤╦┐╔ęŖ(ji©żn)——ĪŻ

ā╚(n©©i)┤µ

ā╚(n©©i)┤µ╝╚īŻśI(y©©)├¹╔ŽĄ─ā╚(n©©i)┤µā”(ch©│)Ų„Ż¼╦³▓╗╩ŪéĆ(g©©)╩▓├┤╔±├žĄ─¢|╬„Ż¼╦³ę▓ų╗╩Ū┤µā”(ch©│)Ų„ųąĄ─£µ║Żę╗╦┌Ż¼╦³░³║ŁĄ─ĘČć·ę▓║▄┤¾Ż¼ę╗░ŃĘų×ķų╗ūx┤µā”(ch©│)Ų„Ż©ROMŻ®║═ļSÖC(j©®)┤µā”(ch©│)Ų„Ż©RAMŻ®Ż¼ęį╝░ūŅÅŖ(qi©óng)║ĘĄ─Ė▀╦┘ŠÅø_┤µā”(ch©│)Ų„Ż©CACHEŻ®Ż¼ų╗ūx┤µā”(ch©│)Ų„æ¬(y©®ng)ė├ÅVĘ║Ż¼╦³═©│Ż╩Ūę╗ēKį┌ė▓╝■╔Ž╝»│╔Ą─┐╔ūxąŠŲ¼Ż¼ū„ė├╩ŪūR(sh©¬)äe┼c┐žųŲė▓╝■Ż¼╦³Ą─╠ž³c(di©Żn)╩Ūų╗┐╔ūx╚ĪŻ¼▓╗─▄īæ╚ļĪŻļSÖC(j©®)┤µā”(ch©│)Ų„Ą─╠ž³c(di©Żn)╩Ū┐╔ūx┐╔īæŻ¼öÓļŖ║¾ę╗ŪąöĄ(sh©┤)ō■(j©┤)Č╝Ž¹╩¦Ż¼╬ęéā╦∙šf(shu©Ł)Ą─ā╚(n©©i)┤µŚlŠ═╩ŪųĖ╦³┴╦ĪŻ

ŠÅ┤µCACHE

ŠÅ┤µŠ═╩ŪöĄ(sh©┤)ō■(j©┤)Į╗ōQĄ─ŠÅø_ģ^(q©▒)Ż©ĘQū„CacheŻ®Ż¼«ö(d©Īng)─│ę╗ė▓╝■ę¬ūx╚ĪöĄ(sh©┤)ō■(j©┤)Ģr(sh©¬)Ż¼Ģ■(hu©¼)╩ūŽ╚Å─ŠÅ┤µųą▓ķšęąĶꬥ─öĄ(sh©┤)ō■(j©┤)Ż¼╚ń╣¹šęĄĮ┴╦ätų▒Įėł╠(zh©¬)ąąŻ¼šę▓╗ĄĮĄ─įÆätÅ─ā╚(n©©i)┤µųąšęĪŻė╔ė┌ŠÅ┤µĄ─▀\(y©┤n)ąą╦┘Č╚▒╚ā╚(n©©i)┤µ┐ņĄ├ČÓŻ¼╣╩ŠÅ┤µĄ─ū„ė├Š═╩ŪÄ═ų·ė▓╝■Ė³┐ņĄž▀\(y©┤n)ąąĪŻ

ę“?y©żn)ķŠÅ┤µ═∙═∙╩╣ė├Ą─╩ŪRAMŻ©öÓļŖ╝┤Ą¶Ą─ĘŪė└Š├ā”(ch©│)┤µŻ®Ż¼╦∙ęįį┌ė├═Ļ║¾▀Ć╩ŪĢ■(hu©¼)░č╬─╝■╦═ĄĮė▓▒PĄ╚┤µā”(ch©│)Ų„└’ė└Š├┤µā”(ch©│)ĪŻļŖ─X└’ūŅ┤¾Ą─ŠÅ┤µŠ═╩Ūā╚(n©©i)┤µŚl┴╦Ż¼ūŅ┐ņĄ─╩ŪCPU╔ŽĶéĄ─L1║═L2ŠÅ┤µŻ¼’@┐©Ą─’@┤µ╩ŪĮo’@┐©▀\(y©┤n)╦ŃąŠŲ¼ė├Ą─ŠÅ┤µŻ¼ė▓▒P╔Žę▓ėą16M╗“š▀32MĄ─ŠÅ┤µĪŻ

CACHE╩Ūį┌CPUųą╦┘Č╚ĘŪ│ŻēKŻ¼Č°╚▌┴┐ģs║▄ąĪĄ─ę╗ĘN┤µā”(ch©│)Ų„Ż¼╦³╩Ūėŗ(j©¼)╦ŃÖC(j©®)┤µā”(ch©│)Ų„ųąūŅÅŖ(qi©óng)║ĘĄ─┤µā”(ch©│)Ų„ĪŻė╔ė┌╝╝ąg(sh©┤)Ž▐ųŲŻ¼╚▌┴┐║▄ļy╠ß╔²ĪŻ

ROMĪóRAMĄ─ģ^(q©▒)äeŻ║

ROMŻ©ų╗ūx┤µā”(ch©│)Ų„╗“š▀╣╠╗»┤µā”(ch©│)Ų„Ż®

RAMŻ©ļSÖC(j©®)┤µ╚Ī┤µā”(ch©│)Ų„Ż®

ROM║═RAMųĖĄ─Č╝╩Ū░ļī¦(d©Żo)¾w┤µā”(ch©│)Ų„Ż¼ROM╩ŪRead Only MemoryĄ─┐sīæŻ¼RAM╩ŪRandom Access MemoryĄ─┐sīæĪŻROMį┌ŽĄĮy(t©»ng)═Żų╣╣®ļŖĄ─Ģr(sh©¬)║“╚į╚╗┐╔ęį▒Ż│ų?j©½n)?sh©┤)ō■(j©┤)Ż¼Č°RAM═©│ŻČ╝╩Ūį┌Ą¶ļŖų«║¾Š═üG╩¦öĄ(sh©┤)ō■(j©┤)Ż¼Ąõą═Ą─RAMŠ═╩Ūėŗ(j©¼)╦ŃÖC(j©®)Ą─ā╚(n©©i)┤µĪŻ

RAMėąā╔┤¾ŅÉŻ¼ę╗ĘNĘQ×ķņoæB(t©żi)RAMŻ©Static RAM/SRAMŻ®Ż¼«ö(d©Īng)öĄ(sh©┤)ō■(j©┤)▒╗┤µ╚ļŲõųą║¾▓╗Ģ■(hu©¼)Ž¹╩¦ĪŻSRAM╦┘Č╚ĘŪ│Ż┐ņŻ¼╩Ū─┐Ū░ūxīæūŅ┐ņĄ─┤µā”(ch©│)įO(sh©©)éõ┴╦ĪŻ«ö(d©Īng)▀@éĆ(g©©)SRAM å╬į¬▒╗┘xėĶ0 ╗“š▀1 Ą─ĀŅæB(t©żi)ų«║¾Ż¼╦³Ģ■(hu©¼)▒Ż│ų▀@éĆ(g©©)ĀŅæB(t©żi)ų▒ĄĮŽ┬┤╬▒╗┘xėĶą┬Ą─ĀŅæB(t©żi)╗“š▀öÓļŖų«║¾▓┼Ģ■(hu©¼)Ė³Ė─╗“š▀Ž¹╩¦ĪŻĄ½╩Ū┤µā”(ch©│)1bit Ą─ą┼ŽóąĶę¬4-6 ų╗Š¦¾w╣▄ĪŻę“┤╦╦³ę▓ĘŪ│Ż░║┘FŻ¼╦∙ęįų╗į┌ę¬Ū¾║▄┐┴┐╠Ą─ĄžĘĮ╩╣ė├Ż¼Ų®╚ńCPUĄ─ę╗╝ē(j©¬)ŠÅø_Ż¼Č■╝ē(j©¬)ŠÅø_ĪŻ┴Ēę╗ĘNĘQ×ķäė(d©░ng)æB(t©żi)RAMŻ©Dynamic RAM/DRAMŻ®Ż¼DRAM ▒žĒÜį┌ę╗Č©Ą─Ģr(sh©¬)ķgā╚(n©©i)▓╗═ŻĄ─╦óą┬▓┼─▄▒Ż│ųŲõųą┤µā”(ch©│)Ą─öĄ(sh©┤)ō■(j©┤)ĪŻDRAM ų╗ę¬1 ų╗Š¦¾w╣▄Š═┐╔ęįīŹ(sh©¬)¼F(xi©żn)ĪŻDRAM▒Ż┴¶öĄ(sh©┤)ō■(j©┤)Ą─Ģr(sh©¬)ķg║▄Č╠Ż¼╦┘Č╚ę▓▒╚SRAM┬²Ż¼▓╗▀^(gu©░)╦³▀Ć╩Ū▒╚╚╬║╬Ą─ROMČ╝ę¬┐ņŻ¼Ą½Å─ār(ji©ż)Ė±╔ŽüĒ(l©ói)šf(shu©Ł)DRAMŽÓ▒╚SRAMę¬▒Ńę╦║▄ ČÓŻ¼ėŗ(j©¼)╦ŃÖC(j©®)ā╚(n©©i)┤µŠ═╩ŪDRAMĄ─ĪŻ

DRAMĘų×ķ║▄ČÓĘNŻ¼│ŻęŖ(ji©żn)Ą─ų„ę¬ėąFPRAM/FastPageĪóEDORAMĪóSDRAMĪóDDR RAMĪóRDRAMĪóSGRAMęį╝░WRAMĄ╚Ż¼▀@└’ĮķĮBŲõųąĄ─ę╗ĘNDDR RAMĪŻDDR RAMŻ©Date-Rate RAMŻ®ę▓ĘQū„DDR SDRAMŻ¼▀@ĘNĖ─▀M(j©¼n)ą═Ą─RAM║═SDRAM╩Ū╗∙▒Šę╗śėĄ─Ż¼▓╗═¼ų«╠Äį┌ė┌╦³┐╔ęįį┌ę╗éĆ(g©©)Ģr(sh©¬)ńŖūxīæā╔┤╬öĄ(sh©┤)ō■(j©┤)Ż¼▀@śėŠ═╩╣Ą├öĄ(sh©┤)ō■(j©┤)é„▌ö╦┘Č╚╝ė▒Č┴╦ĪŻ▀@╩Ū─┐Ū░ļŖ─Xųąė├ Ą├ūŅČÓĄ─ā╚(n©©i)┤µŻ¼Č°Ūę╦³ėąų°│╔▒Šā×(y©Łu)ä▌(sh©¼)Ż¼╩┬īŹ(sh©¬)╔Žō¶öĪ┴╦IntelĄ─┴Ē═Ōę╗ĘNā╚(n©©i)┤µś╦(bi©Īo)£╩(zh©│n)ŻŁRambus DRAMĪŻį┌║▄ČÓĖ▀Č╦Ą─’@┐©╔ŽŻ¼ę▓┼õéõ┴╦Ė▀╦┘DDR RAMüĒ(l©ói)╠ßĖ▀ĦīÆŻ¼▀@┐╔ęį┤¾Ę∙Č╚╠ßĖ▀3D╝ė╦┘┐©Ą─Ž±╦žõų╚Š─▄┴”ĪŻ

ROMę▓ėą║▄ČÓĘNŻ¼PROM╩Ū┐╔ŠÄ│╠Ą─ROMŻ¼PROM║═EPROMŻ©┐╔▓┴│²┐╔ŠÄ│╠ROMŻ®ā╔š▀ģ^(q©▒)äe╩ŪŻ¼PROM╩Ūę╗┤╬ąįĄ─Ż¼ę▓Š═╩Ū▄ø╝■╣Ó╚ļ║¾Ż¼Š═¤o(w©▓)Ę©ą▐ Ė─┴╦Ż¼▀@ĘN╩ŪįńŲ┌Ą─«a(ch©Żn)ŲĘŻ¼¼F(xi©żn)į┌ęčĮø(j©®ng)▓╗┐╔─▄╩╣ė├┴╦Ż¼Č°EPROM╩Ū═©▀^(gu©░)ūŽ═Ō╣ŌĄ─šš╔õ▓┴│÷įŁŽ╚Ą─│╠ą“Ż¼╩Ūę╗ĘN═©ė├Ą─┤µā”(ch©│)Ų„ĪŻ┴Ē═Ōę╗ĘNEEPROM╩Ū═©▀^(gu©░)ļŖūė▓┴│÷Ż¼ār(ji©ż)Ė±║▄Ė▀Ż¼īæ╚ļĢr(sh©¬)ķg║▄ķL(zh©Żng)Ż¼īæ╚ļ║▄┬²ĪŻ

ūŅ│§,░čų╗─▄ūxĄ─┤µā”(ch©│)Ų„Įąū÷ROM(Read Only Memory),▓óŪꥶļŖ║¾öĄ(sh©┤)ō■(j©┤)▓╗Ģ■(hu©¼)üG╩¦ĪŻė╔ė┌▓╗─▄Ė─īæŻ¼ę“Č°╩╣ė├ŲüĒ(l©ói)║▄▓╗ĘĮ▒ŃĪŻļSų°╝╝ąg(sh©┤)Ą─▀M(j©¼n)▓ĮŻ¼į┌ROMųą╩╣ė├ę╗ą®ą┬╝╝ąg(sh©┤)Ż¼Š═┐╔ęį╩╣╦³Š▀ėą┐╔ęįŠÄ│╠Ą─╣”─▄ĪŻ▒╚▌^įńĄ─╩Ū╚█Įzą═Ą─┐╔ŠÄ│╠ROMŻ¼ė╔ė┌╩Ū═©▀^(gu©░)╚█öÓ╚█ĮzüĒ(l©ói)ŠÄ│╠Ą─Ż¼╦∙ęį▀@ŅÉROMŠÄ│╠║¾Ż¼Š═▓╗─▄į┘īæ┴╦Ż¼╩Ūę╗┤╬ąįĄ─(OTP)ĪŻ║¾üĒ(l©ói)ėų│÷¼F(xi©żn)┴╦EPROMŻ¼╩Ū═©▀^(gu©░)ūŽ═ŌŠĆüĒ(l©ói)▓┴│²Ą─Ż¼▓óŪę═©▀^(gu©░)Ė▀ē║üĒ(l©ói)ŠÄ│╠Ż¼▀@ŅÉROM╔Ž├µę╗░Ńėąę╗éĆ(g©©)═Ė├„Ą─╩»ėó▓Ż┴¦┤░Ż¼┐┤╔Ž╚ź═”Ų»┴┴Ą─Ż¼╦³Š═╩Ūė├üĒ(l©ói)ĮoūŽ═ŌŠĆšš╔õĄ─ĪŻ║¾üĒ(l©ói)ėų│÷¼F(xi©żn)┴╦EEPROMŻ¼▓╗ė├ūŽ═ŌŠĆšš╔õŠ═┐╔ęį▓┴│²Ż¼ę“Č°┐╔ęįų▒Įėį┌ļŖ┬ĘųąŠÄ│╠ĪŻ┴Ē═Ō▀ĆėąFLASH ROMŻ¼ėų┐╔Ęų×ķNOR FLASH║═NAND FLASHĪŻFLASH ROMę╗░Ńėąę╗éĆ(g©©)╠ž³c(di©Żn)Ż¼Š═╩ŪīæöĄ(sh©┤)ō■(j©┤)Ģr(sh©¬)Ż¼┐╔ęįīó1Ė─×ķ0Ż¼Č°▓╗─▄īó0Ė─×ķ1Ż¼ę“Č°īæöĄ(sh©┤)ō■(j©┤)Ū░ąĶę¬▓┴│²Ż¼▓┴│²Ģr(sh©¬)īó╦∙ėąöĄ(sh©┤)ō■(j©┤)ų├1ĪŻ

ų«╦∙ęįę└╚╗Įąū÷ROMŻ¼Üw╝{ę╗Ž┬Ż¼┤¾Ė┼ėąÄūéĆ(g©©)įŁę“:

ó┘▓╗─▄Ž±RAM─Ūśė┐ņ╦┘Ą─īæŻ╗

ó┌┐╔─▄ąĶę¬╠ž╩ŌĄ─▓┴īæļŖē║Ż╗

ó█┐╔─▄ąĶę¬╠ž╩ŌĄ─▓┴īæĢr(sh©¬)ą“Ż╗

ó▄┐╔─▄ąĶę¬į┌īæų«Ū░▀M(j©¼n)ąą▓┴│²▓┘ū„Ż╗

ó▌▓┴īæ┤╬öĄ(sh©┤)ėąŽ▐,▓╗Ž±RAM─Ūśė┐╔ęįļSęŌīæČ°▓╗ōpē─Ż╗

ó▐Ą¶ļŖ║¾öĄ(sh©┤)ō■(j©┤)▓╗Ģ■(hu©¼)üG╩¦Ż╗

ó▀ėąą®┐╔īæĄ─┤µā”(ch©│)Ų„ų╗─▄īæę╗┤╬(OTP)ĪŻ

┼eéĆ(g©©)└²ūėŻ¼╩ųÖC(j©®)▄ø╝■ę╗░ŃĘ┼į┌EEPROMųąŻ¼╬ęéā┤“ļŖįÆŻ¼ėąą®ūŅ║¾ō▄┤“Ą─╠¢(h©żo)┤aŻ¼Ģ║Ģr(sh©¬)╩Ū┤µį┌SRAMųąĄ─Ż¼▓╗╩Ū±R╔Žīæ╚ļ═©▀^(gu©░)ėøõøŻ©═©įÆėøõø▒Ż┤µį┌EEPROMųąŻ®Ż¼ę“?y©żn)ķ«?d©Īng)Ģr(sh©¬)ėą║▄ųžę¬╣żū„Ż©═©įÆŻ®ę¬ū÷Ż¼╚ń╣¹īæ╚ļŻ¼┬■ķL(zh©Żng)Ą─Ą╚┤²╩Ūūīė├æ¶╚╠¤o(w©▓)┐╔╚╠Ą─ĪŻ

FLASH┤µā”(ch©│)Ų„ėųĘQķW┤µŻ¼╦³ĮY(ji©”)║Ž┴╦ROM║═RAMĄ─ķL(zh©Żng)╠ÄŻ¼▓╗āHŠ▀éõļŖūė┐╔▓┴│÷┐╔ŠÄ│╠Ż©EEPROMŻ®Ą─ąį─▄Ż¼▀Ć▓╗Ģ■(hu©¼)öÓļŖüG╩¦öĄ(sh©┤)ō■(j©┤)═¼Ģr(sh©¬)┐╔ęį┐ņ╦┘ūx╚ĪöĄ(sh©┤)ō■(j©┤) Ż©NVRAMĄ─ā×(y©Łu)ä▌(sh©¼)Ż®Ż¼U▒P║═MP3└’ė├Ą─Š═╩Ū▀@ĘN┤µā”(ch©│)Ų„ĪŻį┌▀^(gu©░)╚źĄ─20─Ļ└’Ż¼ŪČ╚ļ╩ĮŽĄĮy(t©»ng)ę╗ų▒╩╣ė├ROMŻ©EPROMŻ®ū„×ķ╦³éāĄ─┤µā”(ch©│)įO(sh©©)éõŻ¼╚╗Č°Į³─ĻüĒ(l©ói) Flash╚½├µ┤·╠µ┴╦ROMŻ©EPROMŻ®į┌ŪČ╚ļ╩ĮŽĄĮy(t©»ng)ųąĄ─Ąž╬╗Ż¼ė├ū„┤µā”(ch©│)Bootloaderęį╝░▓┘ū„ŽĄĮy(t©»ng)╗“š▀│╠ą“┤·┤a╗“š▀ų▒Įė«ö(d©Īng)ė▓▒P╩╣ė├Ż©U▒PŻ®ĪŻ

─┐Ū░Flashų„ę¬ėąā╔ĘNNOR Flash║═NADN FlashĪŻNOR FlashĄ─ūx╚Ī║═╬ęéā│ŻęŖ(ji©żn)Ą─SDRAMĄ─ūx╚Ī╩Ūę╗śėŻ¼ė├æ¶┐╔ęįų▒Įė▀\(y©┤n)ąąčb▌dį┌NOR FLASH└’├µĄ─┤·┤aŻ¼▀@śė┐╔ęį£p╔┘SRAMĄ─╚▌┴┐Å─Č°╣Ø(ji©”)╝s┴╦│╔▒ŠĪŻNAND Flashø](m©”i)ėą▓╔╚Īā╚(n©©i)┤µĄ─ļSÖC(j©®)ūx╚Ī╝╝ąg(sh©┤)Ż¼╦³Ą─ūx╚Ī╩Ūęįę╗┤╬ūx╚Īę╗┐ņĄ─ą╬╩ĮüĒ(l©ói)▀M(j©¼n)ąąĄ─Ż¼═©│Ż╩Ūę╗┤╬ūx╚Ī512éĆ(g©©)ūų╣Ø(ji©”)Ż¼▓╔ė├▀@ĘN╝╝ąg(sh©┤)Ą─Flash▒╚▌^┴«ār(ji©ż)ĪŻė├æ¶ ▓╗─▄ų▒Įė▀\(y©┤n)ąąNAND Flash╔ŽĄ─┤·┤aŻ¼ę“┤╦║├ČÓ╩╣ė├NAND FlashĄ─ķ_(k©Īi)░l(f©Ī)░Õ│²┴╦╩╣ė├NAND Flahęį═ŌŻ¼▀Ćū„╔Ž┴╦ę╗ēKąĪĄ─NOR FlashüĒ(l©ói)▀\(y©┤n)ąąåóäė(d©░ng)┤·┤aĪŻ

ę╗░ŃąĪ╚▌┴┐Ą─ė├NOR FlashŻ¼ę“?y©żn)ķŲõūx╚Ī╦┘Č╚┐ņŻ¼ČÓė├üĒ(l©ói)┤µā”(ch©│)▓┘ū„ŽĄĮy(t©»ng)Ą╚ųžę¬ą┼ŽóŻ¼Č°┤¾╚▌┴┐Ą─ė├NAND FLASHŻ¼ūŅ│ŻęŖ(ji©żn)Ą─NAND FLASHæ¬(y©®ng)ė├╩ŪŪČ╚ļ╩ĮŽĄĮy(t©»ng)▓╔ė├Ą─DOCŻ©Disk On ChipŻ®║═╬ęéā═©│Żė├Ą─“ķW▒P”Ż¼┐╔ęįį┌ŠĆ▓┴│²ĪŻ

Å─ā╔éĆ(g©©)ĘĮ├µüĒ(l©ói)╗ž┤:

ę╗ĘĮ├µ╩ŪcacheĄ─ąą×ķĪŻIcache┤¾ČÓČ╝╩ŪĒśą“╚ĪųĖ,┼÷ĄĮĘųų¦ųĖ┴Ņę▓Ģ■(hu©¼)╠°▐D(zhu©Żn),Č°DcacheįLå¢(w©©n)Ą──Ż╩Įūā╗»▒╚▌^┤¾.ę▓Š═╩ŪŪ░š▀╦∙šf(shu©Ł)Ą─patternĄ─å¢(w©©n)Ņ}.ųĖ┴Ņų╗ėąūx║═refillø](m©”i)ėąīæ,Č°öĄ(sh©┤)ō■(j©┤)ėąūxę▓ėąīæ.ūŅųžę¬Ą─╩Ū±T╩ŽĄ─ĮY(ji©”)śŗ(g©░u)╩ŪųĖ┴Ņ║═öĄ(sh©┤)ō■(j©┤)Ęųļx.I║═Dį┌ę╗Ųų╗ėąŽÓ╗źĖ╔ö_.

┴Ēę╗éĆ(g©©)ĘĮ├µŠ═╩Ū,╬’└ĒįO(sh©©)ėŗ(j©¼)╔Ž┐╝æ]Ż║

ę╗éĆ(g©©)unionĄ─cacheŻ¼═¼Ģr(sh©¬)ąĶę¬öĄ(sh©┤)ō■(j©┤)║═ųĖ┴ŅĄ─įLå¢(w©©n)Ż¼Č╦┐┌╔Ž╩Ū║▄ļyīŹ(sh©¬)¼F(xi©żn)Ą─ĪŻ

╦∙ęįę╗░Ńį┌┴„╦«ŠĆĄ─ų„Ė╔╔Ž,Č╝╩Ū▓╔ė├ĘųļxĄ─icache║═dcache.

ĘŪų„Ė╔Ą─L2 cache,Å─╚▌┴┐Ą─ĮŪČ╚┐╝æ]▓╔ė├unionĄ─ĘĮ╩Į.

«ö(d©Īng)╚╗įńŲ┌Ą─ę▓ėą▓╗Ęųļxicache║═dcache.ę“?y©żn)ķįńŲ┌Ą─ĮY(ji©”)śŗ(g©░u)ę▓║å(ji©Żn)å╬.

š¹éĆ(g©©)ŽĄĮy(t©»ng)Ą─īė┤╬ĮY(ji©”)śŗ(g©░u)╚ńłD1╦∙╩ŠŻ¼ė╔ICache║═DCacheśŗ(g©░u)│╔L1 CacheŻ¼ęį╝░║═L1 CacheĮė┐┌Ą─L2 CacheŻ¼║═L2 CacheĮė┐┌Ą─DRAMĪŻŲõųąL1 Cache║═L2 Cache╩Ūį┌╬ó╠Ä└ĒŲ„Ų¼ā╚(n©©i)Ż¼Č°DRAM╩Ūū„×ķų„┤µŻ¼┤µį┌ė┌Ų¼═ŌĪŻ▀@Ė·─┐Ū░ų„┴„Ą─éĆ(g©©)╚╦ļŖ─XĄ─īė┤╬ĮY(ji©”)śŗ(g©░u)║▄ŽÓ╦ŲĪŻ

cacheĖ▀╦┘ŠÅø_┤µā”(ch©│)Ų„ę╗ĘN╠ž╩ŌĄ─┤µā”(ch©│)Ų„ūėŽĄĮy(t©»ng)Ż¼ŲõųąÅ═(f©┤)ųŲ┴╦ŅlĘ▒╩╣ė├Ą─öĄ(sh©┤)ō■(j©┤)ęį└¹ė┌┐ņ╦┘įLå¢(w©©n)ĪŻ┤µā”(ch©│)Ų„Ą─Ė▀╦┘ŠÅø_┤µā”(ch©│)Ų„┤µā”(ch©│)┴╦ŅlĘ▒įLå¢(w©©n)Ą─RAM╬╗ų├Ą─ā╚(n©©i)╚▌╝░▀@ą®öĄ(sh©┤)ō■(j©┤)ĒŚ(xi©żng)Ą─┤µā”(ch©│)ĄžųĘĪŻ«ö(d©Īng)╠Ä└ĒŲ„ę²ė├┤µā”(ch©│)Ų„ųąĄ──│ĄžųĘĢr(sh©¬)Ż¼Ė▀╦┘ŠÅø_┤µā”(ch©│)Ų„▒ŃÖz▓ķ╩Ūʱ┤µėąįōĄžųĘĪŻ╚ń╣¹┤µėąįōĄžųĘŻ¼ätīóöĄ(sh©┤)ō■(j©┤)ĘĄ╗ž╠Ä└ĒŲ„;╚ń╣¹ø](m©”i)ėą▒Ż┤µįōĄžųĘŻ¼ät▀M(j©¼n)ąą│ŻęÄ(gu©®)Ą─┤µā”(ch©│)Ų„įLå¢(w©©n)ĪŻę“?y©żn)ķĖ▀╦┘ŠÅø_┤µā”(ch©│)Ų„┐é╩Ū▒╚ų„RAM┤µā”(ch©│)Ų„╦┘Č╚┐ņŻ¼╦∙ęį«ö(d©Īng)RAMĄ─įLå¢(w©©n)╦┘Č╚Ą═ė┌╬ó╠Ä└ĒŲ„Ą─╦┘Č╚Ģr(sh©¬)Ż¼│Ż╩╣ė├Ė▀╦┘ŠÅø_┤µā”(ch©│)Ų„ĪŻ

Cache(╝┤Ė▀╦┘ŠÅø_┤µā”(ch©│)Ų„(Cache Memory)Ż¼╩Ū╬ęéāūŅ│Ż┬Ā(t©®ng)ĄĮĄ─ę╗éĆ(g©©)į~┴╦ĪŻį┌└Ž°B(ni©Żo)éāč█ųąŻ¼▀@éĆ(g©©)į~╗“įSęčø](m©”i)ėąį┘šäĄ─▒žę¬Ż¼ę“?y©żn)ķ╦¹éāī?du©¼)CacheÅ─įO(sh©©)ėŗ(j©¼)Ą─▒žę¬ąįĄĮ╣żū„įŁ└ĒĪó╣żū„▀^(gu©░)│╠Ą╚Ą╚Č╝ęč┴╦╚ńųĖšŲ┴╦Ż╗Č°ī”(du©¼)▓╦°B(ni©Żo)┼¾ėčéāČ°čįŻ¼▀@ą®╬┤▒žŠ═║▄ŪÕ│■ĪŻ─Ū├┤Ż¼╦³éāĄĮĄū╩ŪųĖĄ─╩▓├┤─žŻ┐▓╗ė├╝▒Ż¼Ž┬├µŠ═šł(q©½ng)ļS╣Pš▀ę╗ŲüĒ(l©ói)╚½├µšJ(r©©n)ūR(sh©¬)CacheĪŻ

×ķ╩▓├┤ę¬įO(sh©©)ėŗ(j©¼)CacheŻ┐

╬ęéāų¬Ą└Ż¼ļŖ─XĄ─ā╚(n©©i)┤µ╩ŪęįŽĄĮy(t©»ng)┐éŠĆĄ─Ģr(sh©¬)ńŖŅl┬╩╣żū„Ą─Ż¼▀@éĆ(g©©)Ņl┬╩═©│Żę▓Š═╩ŪCPUĄ─═ŌŅl(ī”(du©¼)ė┌└ū°B(ni©Żo)ĪóČŠ²łŽĄ┴ąĄ─╠Ä└ĒŲ„Ż¼ė╔ė┌į┌įO(sh©©)ėŗ(j©¼)▓╔ė├┴╦DDR╝╝ąg(sh©┤)Ż¼CPU╣żū„Ą─═ŌŅl×ķŽĄĮy(t©»ng)┐éŠĆŅl┬╩Ą─ā╔▒Č)ĪŻĄ½╩ŪŻ¼CPUĄ─╣żū„Ņl┬╩(ų„Ņl)╩Ū═ŌŅl┼c▒ČŅlę“ūėĄ─│╦ĘeĪŻ▀@śėę╗üĒ(l©ói)Ż¼ā╚(n©©i)┤µĄ─╣żū„Ņl┬╩Š═▀h(yu©Żn)Ą═ė┌CPUĄ─╣żū„Ņl┬╩┴╦ĪŻ▀@śėįņ│╔Ą─ų▒ĮėĮY(ji©”)╣¹╩ŪŻ║CPUį┌ł╠(zh©¬)ąą═Ļę╗ŚlųĖ┴Ņ║¾Ż¼│Ż│ŻąĶꬓĄ╚┤²”ę╗ą®Ģr(sh©¬)ķg▓┼─▄į┘┤╬įLå¢(w©©n)ā╚(n©©i)┤µŻ¼śO┤¾ĮĄ┴╦CPU╣żū„ą¦┬╩ĪŻį┌▀@śėę╗ĘNŪķørŽ┬Ż¼CacheŠ═æ¬(y©®ng)▀\(y©┤n)Č°╔·┴╦ŻĪ

CACHEŻ║Cache╩Ūę╗ĘN╠ž╩ŌĄ─┤µā”(ch©│)Ų„Ż¼╦³ė╔Cache ┤µā”(ch©│)▓┐╝■║═Cache┐žųŲ▓┐╝■ĮM│╔ĪŻCache ┤µā”(ch©│)▓┐╝■ę╗░Ń▓╔ė├┼cCPU═¼ŅÉą═Ą─░ļī¦(d©Żo)¾w┤µā”(ch©│)Ų„╝■Ż¼┤µ╚Ī╦┘Č╚▒╚ā╚(n©©i)┤µ┐ņÄū▒Č╔§ų┴╩«Äū▒ČĪŻČ°Cache ┐žųŲŲ„▓┐╝■░³└©ų„┤µĄžųĘ╝─┤µŲ„ĪóCache ĄžųĘ╝─┤µŲ„Ż¼ų„┤µ—CacheĄžųĘūāōQ▓┐╝■╝░╠µōQ┐žųŲ▓┐╝■Ą╚ĪŻų┴ė┌╦³éāĖ„ūįėų╩Ūį§śė╣żū„Ą─Īóėą║╬ū„ė├Ą╚Ą╚Ż¼╬ęŽļ╬ęéāŠ═ø](m©”i)ėą▒žę¬ū÷▀M(j©¼n)ę╗▓ĮĄ─蹊┐Ż¼ų¬Ą└ę╗░ŃCacheĘų×ķL(zh©Żng)1 Cache(ŲõųąėųĘų×ķöĄ(sh©┤)ō■(j©┤)CacheĪó┤·┤aCache)ĪóL2 CacheŠ═ąą┴╦ĪŻ

╬ęéāų¬Ą└Ż¼CPU▀\(y©┤n)ąą│╠ą“╩Ūę╗ŚlųĖ┴Ņę╗ŚlųĖ┴ŅĄžł╠(zh©¬)ąąĄ─Ż¼Č°ŪęųĖ┴ŅĄžųĘ═∙═∙╩Ū▀B└m(x©┤)Ą─Ż¼ęŌ╦╝Š═╩Ūšf(shu©Ł)CPUį┌įLå¢(w©©n)ā╚(n©©i)┤µĢr(sh©¬)Ż¼į┌▌^Č╠Ą─ę╗Č╬Ģr(sh©¬)ķgā╚(n©©i)═∙═∙╝»ųąė┌─│éĆ(g©©)Šų▓┐Ż¼▀@Ģr(sh©¬)║“┐╔─▄Ģ■(hu©¼)┼÷ĄĮę╗ą®ąĶę¬Ę┤Å═(f©┤)š{(di©żo)ė├Ą─ūė│╠ą“ĪŻļŖ─Xį┌╣żū„Ģr(sh©¬)Ż¼░č▀@ą®╗Ņ▄SĄ─ūė│╠ą“┤µ╚ļ▒╚ā╚(n©©i)┤µ┐ņĄ├ČÓĄ─Cache ųąĪŻCPUį┌įLå¢(w©©n)ā╚(n©©i)┤µĢr(sh©¬)Ż¼╩ūŽ╚┼ąöÓ╦∙ę¬įLå¢(w©©n)Ą─ā╚(n©©i)╚▌╩Ūʱį┌CacheųąŻ¼╚ń╣¹į┌Ż¼Š═ĘQ×ķ“├³ųą”Ż¼┤╦Ģr(sh©¬)CPUų▒ĮėÅ─Cacheųąš{(di©żo)ė├įōā╚(n©©i)╚▌Ż╗ʱätŻ¼Š═ĘQ×ķ“▓╗├³ųą”Ż¼CPUų╗║├╚źā╚(n©©i)┤µųąš{(di©żo)ė├╦∙ąĶĄ─ūė│╠ą“╗“ųĖ┴Ņ┴╦ĪŻCPU▓╗Ą½┐╔ęįų▒ĮėÅ─Cacheųąūx│÷ā╚(n©©i)╚▌Ż¼ę▓┐╔ęįų▒Įė═∙Ųõųąīæ╚ļā╚(n©©i)╚▌ĪŻė╔ė┌CacheĄ─┤µ╚Ī╦┘┬╩ŽÓ«ö(d©Īng)┐ņŻ¼╩╣Ą├CPUĄ─└¹ė├┬╩┤¾┤¾╠ßĖ▀Ż¼▀M(j©¼n)Č°╩╣š¹éĆ(g©©)ŽĄĮy(t©»ng)Ą─ąį─▄Ą├ęį╠ß╔²

įńį┌486Ģr(sh©¬)┤·Ż¼ų„░Õ╔ŽŠ═įO(sh©©)ėŗ(j©¼)┴╦Cache▓Õ▓█Ż¼ė├æ¶┐╔ęįĖ∙ō■(j©┤)ąĶę¬ūį╝║┼õų├CacheŻ╗586╝ē(j©¬)Ą─CPUąŠŲ¼ųąęč╝»│╔┴╦▓┐ĘųCacheŻ¼═¼Ģr(sh©¬)▀Ć▒Ż┴¶┴╦Cache▓Õ▓█╣®ė├æ¶öU(ku©░)│õŻ¼Č°ĄĮ┴╦Pentium ó“Ģr(sh©¬)┤·║¾Ż¼Cacheęč╚½▓┐╝»│╔ĄĮ┴╦CPUąŠŲ¼ųąŻ¼ų„░Õ╔Žį┘ę▓ø](m©”i)ėąCache▓Õ▓█ĪŻ¼F(xi©żn)į┌▒╚▌^┴„ąąĄ─CPUąŠŲ¼ųąę╗░Ń╝»│╔┴╦ų┴╔┘16KBĄ─┤·┤aCache ║═16KBĄ─öĄ(sh©┤)ō■(j©┤)Cache(ū„×ķL(zh©Żng)1 Cache)Ż¼ęį╝░ų┴╔┘64KBĄ─L2 CacheĪŻ

ėąĄ─┼¾ėč┐╔─▄Ģ■(hu©¼)å¢(w©©n)Ż¼╝╚╚╗CacheĄ─ū„ė├╚ń┤╦ųžę¬Ż¼─Ū×ķ├┤▓╗░čļŖ─XĄ─╚½▓┐?j©®)?n©©i)┤µČ╝ūā?y©Łu)ķCacheŻ¼─Ūśė▓╗╩ŪĖ³║├å߯┐ŲõīŹ(sh©¬)ī”(du©¼)ė┌▀@éĆ(g©©)å¢(w©©n)Ņ}Ż¼Ų▓ķ_(k©Īi)ār(ji©ż)Ė±ę“╦žŻ¼å╬Š═ŲõīŹ(sh©¬)ė├ąįČ°čįę▓╩Ūø](m©”i)ėą▒žę¬Ą─Ż¼«ģŠ╣Ż¼ļŖ─Xį┌ł╠(zh©¬)╚╬äš(w©┤)Ģr(sh©¬)Ż¼─ŪĘN╩╣ė├Ņl┬╩ĘŪ│ŻĖ▀Ą─ūė│╠ą“╗“ųĖ┴Ņ▓╗╩Ū║▄ČÓĄ─Ż¼ę“┤╦─Ūą®╩╣ė├Ņl┬╩▓╗╠½Ė▀Ą─ā╚(n©©i)╚▌ų╗ĒÜ▒Ż┤µį┌╦┘Č╚ŽÓī”(du©¼)▌^Ą═Ą─ā╚(n©©i)┤µųąŠ═┐╔ęį┴╦ŻĪ

į┌īŹ(sh©¬)ļHæ¬(y©®ng)ė├ųąŻ¼CacheŻ¼ė╚Ųõ╩ŪL2Cacheī”(du©¼)ŽĄĮy(t©»ng)Ą─ąį─▄Ż¼╠žäe╩Ūī”(du©¼)ĖĪ³c(di©Żn)▀\(y©┤n)╦Ń─▄┴”ėą▌^┤¾Ą─ė░ĒæĪŻČ°╬ęéāų¬Ą└Ż¼┤¾▓┐Ęųė╬æ“Ą─┴„Ģ│▀\(y©┤n)ąąąĶę¬ŅlĘ▒Ą─ĖĪ³c(di©Żn)▀\(y©┤n)╦ŃĪŻę“┤╦Ż¼CPU▀\(y©┤n)ąąė╬æ“Ą─ąį─▄Ą─║├ē─┼cL2CacheĄ─╚▌┴┐┼c╦┘Č╚ėą║▄┤¾ĻP(gu©Īn)ŽĄĪŻ

ĄžųĘė│Ž±

·ĄžųĘė│Ž±

╦∙ų^ė│Ž¾å¢(w©©n)Ņ}╩ŪųĖ╚ń║╬┤_Č©CacheųąĄ─ā╚(n©©i)╚▌╩Ūų„┤µųąĄ───ę╗▓┐ĘųĄ─┐ĮžÉŻ¼╝┤▒žĒÜæ¬(y©®ng)ė├─│ĘN║»öĄ(sh©┤)░čų„┤µĄžųĘė│Ž¾ĄĮCacheųąČ©╬╗Ż¼ę▓ĘQĄžųĘė│Ž¾ĪŻ«ö(d©Īng)ą┼Žó░┤▀@ĘNĘĮ╩Įčb╚ļCacheųą║¾Ż¼ł╠(zh©¬)ąą│╠ą“Ģr(sh©¬)Ż¼æ¬(y©®ng)īóų„┤µĄžųĘūāōQ×ķCacheĄžųĘŻ¼▀@éĆ(g©©)ūāōQ▀^(gu©░)│╠Įąū„ĄžųĘūāōQĪŻĄžųĘė│Ž¾ĘĮ╩Į═©│Ż▓╔ė├ų▒Įėė│Ž¾Īó╚½ŽÓ┬ō(li©ón)ė│Ž¾ĪóĮMŽÓ┬ō(li©ón)ė│Ž¾╚²ĘN

1Īóų▒Įėė│Ž±

╩ŪųĖ├┐éĆ(g©©)ų„┤µĒō(y©©)ų╗─▄Å═(f©┤)ųŲĄĮ─│ę╗╣╠Č©Ą─CacheĒō(y©©)ųąĪŻų▒Įėė│Ž±Ą─ęÄ(gu©®)┬╔╩ŪŻ║īóų„┤µĄ─2048Ēō(y©©)Ęų×ķ128ĮMŻ¼├┐ĮMėą16Ēō(y©©)Ż¼Ęųäe┼cCacheĄ─16Ēō(y©©)ų▒Įėī”(du©¼)æ¬(y©®ng)Ż¼╝┤ų„┤µĄ─Ą┌0Ēō(y©©)ĪóĄ┌16Ēō(y©©)ĪóĄ┌32Ēō(y©©)……ų╗─▄ė│Ž±ĄĮCacheĄ─Ą┌0Ēō(y©©)ĪŻ

2Īó╚½ŽÓ┬ō(li©ón)ė│Ž±

╚½ŽÓ┬ō(li©ón)ė│Ž±╩ŪųĖų„┤µĄ─├┐ę╗Ēō(y©©)┐╔ęįė│Ž±┐╔ęįė│Ž±ĄĮCacheĄ─╚╬ęŌę╗Ēō(y©©)ĪŻ

3ĪóĮMŽÓ┬ō(li©ón)ė│Ž±

ĮMŽÓ┬ō(li©ón)ė│Ž±╩Ūų▒Įėė│Ž±┼c╚½ŽÓ┬ō(li©ón)ė│Ž±Ą─š█ųąĘĮ░ĖŻ¼╦³īóCacheĘų×ķ╚¶Ė╔ĮMŻ¼╚ń8ĮMŻ╗├┐ĮM╚¶Ė╔Ēō(y©©)Ż¼╚ń2Ēō(y©©)Ż╗═¼Ģr(sh©¬)īóų„┤µĘų×ķ╚¶Ė╔ĮMŻ¼╚ń255ĮMŻ╗├┐ĮMā╚(n©©i)Ą─Ēō(y©©)öĄ(sh©┤)┼cCacheĄ─ĮMöĄ(sh©┤)ŽÓ═¼Ż¼╚ń8Ēō(y©©)ĪŻĮMŽÓ┬ō(li©ón)ė│Ž±Ą─ęÄ(gu©®)┬╔╩Ūų„┤µųąĄ─Ė„Ēō(y©©)┼cCacheĄ─ĮM╠¢(h©żo)ėą╣╠Č©Ą─ė│Ž±ĻP(gu©Īn)ŽĄŻ¼Ą½┐╔ūįė╔ė│Ž±ĄĮī”(du©¼)æ¬(y©®ng)Ą─CacheĮMųąĄ─╚╬ęŌę╗Ēō(y©©)ĪŻ╝┤ĮMķg▓╔ė├ų▒Įėė│Ž±Ż¼Č°ĮMā╚(n©©i)Ą─Ēō(y©©)×ķ╚½ŽÓ┬ō(li©ón)ė│Ž±ĪŻ

«ö(d©Īng)CPUįLå¢(w©©n)Cache╬┤├³ųąĢr(sh©¬)Ż¼æ¬(y©®ng)Å─ų„┤µųąūx╚Īą┼ŽóŻ¼═¼Ģr(sh©¬)īæ╚ļCacheĪŻ╚¶Cache╬┤ØMŻ¼ätų▒Įėīæ╚ļŻ╗╚¶CacheęčØMŻ¼ätąĶę¬▀M(j©¼n)ąą╠µōQĪŻ╠µōQÖC(j©®)śŗ(g©░u)ė╔ė▓╝■ĮM│╔Ż¼▓ó░┤╠µōQ╦ŃĘ©▀M(j©¼n)ąąįO(sh©©)ėŗ(j©¼)Ż¼Ųõū„ė├╩ŪųĖ│÷╠µōQĄ─Ēō(y©©)╠¢(h©żo)ĪŻ│Żė├Ą─╠µōQ╦ŃĘ©ėąŽ╚▀M(j©¼n)Ž╚│÷╦ŃĘ©Ż©FIFOŻ®║═Į³Ų┌ūŅ╔┘╩╣ė├╦ŃĘ©Ż©LRUŻ®ĪŻ

1Īóūx▓┘ū„

įL┤µĢr(sh©¬)Ż¼īóų„┤µĄžųĘ═¼Ģr(sh©¬)╦═ų„┤µ║═CacheŻ¼ę╗ätåóäė(d©░ng)ī”(du©¼)ų„┤µĄ─ūx▓┘ū„Ż¼Č■ätį┌Cacheųą░┤ė│Ž±ĘĮ╩ĮÅ─ųą½@╚ĪCacheĄžųĘŻ¼▓óīóų„┤µś╦(bi©Īo)ėø┼cCacheś╦(bi©Īo)ėø▒╚▌^Ż║╚¶ŽÓ═¼Ż¼ätįLå¢(w©©n)├³ųąŻ¼Å─Cacheųąūx╚ĪöĄ(sh©┤)ō■(j©┤)ĪŻę“?y©żn)ķCache╦┘Č╚▒╚ų„┤µ╦┘Č╚┐ņŻ¼╦∙ęį▓╗Ą╚ų„┤µūx▓┘ū„ĮY(ji©”)╩°Ż¼╝┤┐╔└^└m(x©┤)Ž┬ę╗┤╬įL┤µ▓┘ū„Ż╗╚¶▓╗ŽÓ═¼Ż¼ätįLå¢(w©©n)╬┤├³ųąŻ¼ätÅ─ų„┤µųąūx╚ĪöĄ(sh©┤)ō■(j©┤)Ż¼▓ó┐╝æ]╩Ūʱ░┤─│ĘN╠µōQ╦ŃĘ©Ė³ą┬Cache─│Ēō(y©©)Ą─ā╚(n©©i)╚▌ĪŻ

2Īóīæ▓┘ū„

īóöĄ(sh©┤)ō■(j©┤)īæ╚ļų„┤µėąā╔ĘNĘĮĘ©Ż¼īæ╗žĘ©║═ą®ų▒▀_(d©ó)Ę©ĪŻ

īæ╗žĘ©Ż║ą┼ŽóĢ║Ģr(sh©¬)ų╗īæ╚ļCacheŻ¼▓óė├ś╦(bi©Īo)ųŠ╝ėęįūó├„Ż¼ų▒ĄĮįōĒō(y©©)ā╚(n©©i)╚▌ąĶÅ─Cacheųą╠µōQ│÷üĒ(l©ói)Ģr(sh©¬)Ż¼▓┼ę╗┤╬īæ╚ļų„┤µĪŻā×(y©Łu)³c(di©Żn)╩Ū▓┘ū„╦┘Č╚┐ņŻ¼╚▒³c(di©Żn)╩Ūīæ╗žų„┤µŪ░Ż¼ų„┤µųąø](m©”i)ėą▀@ą®ā╚(n©©i)╚▌Ż¼┼cCache▓╗ę╗ų┬Ż¼ęūįņ│╔Õe(cu©░)š`ĪŻ

īæų▒▀_(d©ó)Ę©Ż║ą┼Žóį┌īæ╚ļCahceĢr(sh©¬)ę▓═¼Ģr(sh©¬)īæ╚ļų„┤µĪŻā×(y©Łu)³c(di©Żn)╩Ūų„┤µ┼cCache╩╝ĮK▒Ż│ųę╗ų┬Ż¼Ą½╦┘Č╚┬²ĪŻ

ŠÅ┤µŻ©cachedŻ®╩Ū░čūx╚Ī▀^(gu©░)Ą─öĄ(sh©┤)ō■(j©┤)▒Ż┤µŲüĒ(l©ói)Ż¼ųžą┬ūx╚ĪĢr(sh©¬)╚¶├³ųąŻ©šęĄĮąĶꬥ─öĄ(sh©┤)ō■(j©┤)Ż®Š═▓╗ę¬╚źūxė▓▒P┴╦Ż¼╚¶ø](m©”i)ėą├³ųąŠ═ūxė▓▒PĪŻŲõųąĄ─öĄ(sh©┤)ō■(j©┤)Ģ■(hu©¼)Ė∙ō■(j©┤)ūx╚ĪŅl┬╩▀M(j©¼n)ąąĮM┐ŚŻ¼░čūŅŅlĘ▒ūx╚ĪĄ─ā╚(n©©i)╚▌Ę┼į┌ūŅ╚▌ęūšęĄĮĄ─╬╗ų├Ż¼░č▓╗į┘ūxĄ─ā╚(n©©i)╚▌▓╗öÓ═∙║¾┼┼Ż¼ų▒ų┴Å─ųąäh│²ĪŻĪĪĪĪ

ŠÅø_Ż©buffersŻ®╩ŪĖ∙ō■(j©┤)┤┼▒PĄ─ūxīæįO(sh©©)ėŗ(j©¼)Ą─Ż¼░čĘų╔óĄ─īæ▓┘ū„╝»ųą▀M(j©¼n)ąąŻ¼£p╔┘┤┼▒P╦ķŲ¼║═ė▓▒PĄ─Ę┤Å═(f©┤)īżĄ└Ż¼Å─Č°╠ßĖ▀ŽĄĮy(t©»ng)ąį─▄ĪŻlinuxėąę╗éĆ(g©©)╩žūo(h©┤)▀M(j©¼n)│╠Č©Ų┌ŪÕ┐šŠÅø_ā╚(n©©i)╚▌Ż©╝┤īæ╚ń┤┼▒PŻ®Ż¼ę▓┐╔ęį═©▀^(gu©░)sync├³┴Ņ╩ųäė(d©░ng)ŪÕ┐šŠÅø_ĪŻ┼eéĆ(g©©)└²ūė░╔Ż║╬ę▀@└’ėąę╗éĆ(g©©)ext2Ą─U▒PŻ¼╬ę═∙└’├µcpę╗éĆ(g©©)3MĄ─MP3Ż¼Ą½U▒PĄ─¤¶ø](m©”i)ėą╠°äė(d©░ng)Ż¼▀^(gu©░)┴╦ę╗Ģ■(hu©¼)ā║Ż©╗“š▀╩ųäė(d©░ng)▌ö╚ļsyncŻ®U▒PĄ─¤¶Š═╠°äė(d©░ng)ŲüĒ(l©ói)┴╦ĪŻąČ▌dįO(sh©©)éõĢr(sh©¬)Ģ■(hu©¼)ŪÕ┐šŠÅø_Ż¼╦∙ęįėąą®Ģr(sh©¬)║“ąČ▌dę╗éĆ(g©©)įO(sh©©)éõĢr(sh©¬)ꬥ╚╔ŽÄū├ļńŖĪŻĪĪĪĪ

ą▐Ė─/etc/sysctl.confųąĄ─vm.swappinessėę▀ģĄ─öĄ(sh©┤)ūų┐╔ęįį┌Ž┬┤╬ķ_(k©Īi)ÖC(j©®)Ģr(sh©¬)š{(di©żo)╣Ø(ji©”)swap╩╣ė├▓▀┬įĪŻįōöĄ(sh©┤)ūųĘČć·╩Ū0Ī½100Ż¼öĄ(sh©┤)ūųįĮ┤¾įĮāAŽ“ė┌╩╣ė├swapĪŻ─¼šJ(r©©n)×ķ60Ż¼┐╔ęįĖ─ę╗Ž┬įćįćĪŻā╔š▀Č╝╩ŪRAMųąĄ─öĄ(sh©┤)ō■(j©┤)ĪŻ║å(ji©Żn)å╬üĒ(l©ói)šf(shu©Ł)Ż¼buffer╩Ū╝┤īóę¬▒╗īæ╚ļ┤┼▒PĄ─Ż¼Č°cache╩Ū▒╗Å─┤┼▒Pųąūx│÷üĒ(l©ói)Ą─ĪŻĪĪĪĪ

buffer╩Ūė╔Ė„ĘN▀M(j©¼n)│╠Ęų┼õĄ─Ż¼▒╗ė├į┌╚ń▌ö╚ļĻĀ(du©¼)┴ąĄ╚ĘĮ├µŻ¼ę╗éĆ(g©©)║å(ji©Żn)å╬Ą─└²ūė╚ń─│éĆ(g©©)▀M(j©¼n)│╠ę¬Ū¾ėąČÓéĆ(g©©)ūųČ╬ūx╚ļŻ¼į┌╦∙ėąūųČ╬▒╗ūx╚ļ═Ļš¹ų«Ū░Ż¼▀M(j©¼n)│╠░čŽ╚Ū░ūx╚ļĄ─ūųČ╬Ę┼į┌bufferųą▒Ż┤µĪŻĪĪĪĪ

cacheĮø(j©®ng)│Ż▒╗ė├į┌┤┼▒PĄ─I/Ošł(q©½ng)Ū¾╔ŽŻ¼╚ń╣¹ėąČÓéĆ(g©©)▀M(j©¼n)│╠Č╝ę¬įLå¢(w©©n)─│éĆ(g©©)╬─╝■Ż¼ė┌╩Ūįō╬─╝■▒Ń▒╗ū÷│╔cacheęįĘĮ▒ŃŽ┬┤╬▒╗įLå¢(w©©n)Ż¼▀@śė┐╔╠ß╣®ŽĄĮy(t©»ng)ąį─▄ĪŻ

═©│Ż╚╦éā╦∙šf(shu©Ł)Ą─CacheŠ═╩ŪųĖŠÅ┤µSRAMĪŻ SRAMĮąņoæB(t©żi)ā╚(n©©i)┤µŻ¼“ņoæB(t©żi)”ųĖĄ─╩Ū«ö(d©Īng)╬ęéāīóę╗╣PöĄ(sh©┤)ō■(j©┤)īæ╚ļSRAM║¾Ż¼│²ĘŪųžą┬īæ╚ļą┬öĄ(sh©┤)ō■(j©┤)╗“ĻP(gu©Īn)ķ]ļŖį┤Ż¼Ę±ätīæ╚ļĄ─öĄ(sh©┤)ō■(j©┤)▒Ż│ų▓╗ūāĪŻ ĪĪĪĪ

ų„░ÕłDāį(c©©)

ų„░ÕłDāį(c©©)

ėą┴╦Ė▀╦┘ŠÅ┤µŻ¼┐╔ęįŽ╚░čöĄ(sh©┤)ō■(j©┤)ŅA(y©┤)īæĄĮŲõųąŻ¼ąĶę¬Ģr(sh©¬)ų▒ĮėÅ─╦³ūx│÷Ż¼▀@Š═┐sČ╠┴╦CPUĄ─Ą╚┤²Ģr(sh©¬)ķgĪŻĖ▀╦┘ŠÅ┤µų«╦∙ęį─▄╠ßĖ▀ŽĄĮy(t©»ng)Ą─╦┘Č╚╩Ū╗∙ė┌ę╗ĘNĮy(t©»ng)ėŗ(j©¼)ęÄ(gu©®)┬╔Ż¼ų„░Õ╔ŽĄ─┐žųŲŽĄĮy(t©»ng)Ģ■(hu©¼)ūįäė(d©░ng)Įy(t©»ng)ėŗ(j©¼)ā╚(n©©i)┤µųą──ą®öĄ(sh©┤)ō■(j©┤)Ģ■(hu©¼)▒╗ŅlĘ▒Ą─╩╣ė├Ż¼Š═░č▀@ą®öĄ(sh©┤)ō■(j©┤)┤µį┌Ė▀╦┘ŠÅ┤µųąŻ¼CPUę¬įLå¢(w©©n)▀@ą®öĄ(sh©┤)ō■(j©┤)Ģr(sh©¬)Ż¼Š═Ģ■(hu©¼)Ž╚ĄĮCacheųą╚źšęŻ¼Å─Č°╠ßĖ▀š¹¾wĄ─▀\(y©┤n)ąą╦┘Č╚ĪŻę╗░Ńšf(shu©Ł)üĒ(l©ói)Ż¼256KĄ─Ė▀╦┘ŠÅ┤µ─▄╩╣š¹ÖC(j©®)╦┘Č╚ŲĮŠ∙╠ßĖ▀10%ū¾ėęĪŻĪĪĪĪ

ų„░Õ╔Ž═©│ŻČ╝Ģ■(hu©¼)╠ß╣®256KĄĮ1MĄ─ŠÅ┤µĪŻį┌CPUā╚(n©©i)▓┐ę▓ėąĖ▀╦┘ŠÅ┤µŻ¼╚ń486CPUėą8KĄ─Ė▀╦┘ŠÅ┤µŻ¼Pentiumėą16KĄ─Ė▀╦┘ŠÅ┤µĪŻPentium IIėą32K ę╗╝ē(j©¬)ŠÅ┤µŻ¼AMD K6-2ųąėą64KĄ─ę╗╝ē(j©¬)CacheŻ¼AMD K6-3ųąėą64K Ą─ę╗╝ē(j©¬) CacheŻ¼║═256K Ą─Č■╝ē(j©¬)CacheŻ¼Cyrix MII ųąėą64KĄ─CacheĪŻĪĪĪĪ

×ķ┴╦ģ^(q©▒)Ęų╦³éāŻ¼CPUā╚(n©©i)▓┐Ą─ŠÅ┤µĮąā╚(n©©i)▓┐Ė▀╦┘ŠÅ┤µ(Internal Cache)╗“ę╗╝ē(j©¬)Ė▀╦┘ŠÅ┤µŻ¼ų„░Õ╔ŽĄ─ŠÅ┤µĮą═Ō▓┐Ė▀╦┘ŠÅ┤µ(External Cache)╗“Č■╝ē(j©¬)Ė▀╦┘ŠÅ┤µĪŻ▓╗▀^(gu©░)¼F(xi©żn)į┌Ą─Pentium II Ą─CPUęčĮø(j©®ng)īóų„░Õ╔ŽĄ─Č■╝ē(j©¬)ŠÅ┤µĘŌčbį┌CPUĄ─║ąūėųąŻ¼AMD K6-3Ą─CPUā╚(n©©i)▓┐ę▓╝»│╔┴╦256KĄ─Č■╝ē(j©¬)CacheŻ¼ī”(du©¼)ė┌▀@ŅÉCPUüĒ(l©ói)šf(shu©Ł)Ż¼ų„░Õ╔Ž╠ß╣®Ą─ęč╩Ū╚²╝ē(j©¬)ŠÅ┤µ┴╦ĪŻ

Æ▀┤aĻP(gu©Īn)ūó╬ęéā

Ó]ŽõŻ║ivy@yingtexin.net

ĄžųĘŻ║╔Ņ█┌╩ą²ł╚Aģ^(q©▒)├±ų╬ĮųĄ└├±ų╬┤¾Ą└973╚f(w©żn)▒ŖØÖ(r©┤n)žSäō(chu©żng)śI(y©©)ł@AŚØ2śŪA09