���ã��gӭ�M(j��n)�������зf���¿Ƽ�����˾�ٷ��W(w��ng)վ��

���ã��gӭ�M(j��n)�������зf���¿Ƽ�����˾�ٷ��W(w��ng)վ��

���˹����ܣ�AI�����C(j��)���W(xu��)��(x��)��ML���͔�(sh��)��(j��)�ھ�Ŀ��У��҂�����(sh��)��(j��)̎���Ŀ���ʬF(xi��n)��ǰ��δ�е�ָ��(sh��)�����L���挦�@�Nǰ������(n��i)�控�����˔�(sh��)�֕r(sh��)�����P(gu��n)�I����(d��ng)�}�������У����p����(sh��)��(j��)��ݔ���ʺ��ߵĎ��������� DDR��Double Data Rate�����g(sh��)�����(d��ng)�B(t��i)�S�C(j��)��ȡ�惦����DRAM������Ҫ���M(j��n)���O����Ƅ�(d��ng)��Ӌ(j��)��C(j��)���ܵ��������� 2000 ���һ�� DDR ���g(sh��)�Q������ 2020 �� DDR5��ÿһ�� DDR ���g(sh��)�ڎ��������ܺ��ĵȸ���(g��)���涼��(sh��)�F(xi��n)���@�����M(j��n)����

��oՓ�� PC���P�߀���˹����ܣ����ИI(y��)���ڼ����� DDR5 �¼o(j��)Ԫ�~�M(j��n)�����꣬����ʽ AI �Ј���l(f��)չ�����ڴ���ģ�͑�(y��ng)�õ� AI ����(w��)�������Ƅ�(d��ng)�ˌ� DDR5 �������S����(n��i)���Ј�����Ļ�ů����(n��i)��оƬ����(y��ng)�̂��������ڽ���� 4 ����ȫ������ DDR5 �a(ch��n)�ܣ���ȡ���F(xi��n)��� DDR4��

DDR5 ���r(sh��)���ѽ�(j��ng)���R��Ȼ����һЩ����(zh��n)Ҳ��K�ˮa(ch��n)�I(y��)���M(j��n)һ���l(f��)չ��

DDR5 �r(sh��)�������������ܱ�����O(sh��)Ӌ(j��)����(zh��n)

2020 �� 7 �£�DDR5 ��(n��i)�漼�g(sh��)��(bi��o)��(zh��n)��ʽ�l(f��)������(bi��o)־����(n��i)�漼�g(sh��)�_�����µ�ƪ�¡�DDR5 �Ը��ߵĎ��������������ˏV�����P(gu��n)ע���c֮ǰ�� DDR4 ��ȣ�DDR5 �����(y��u)���������@�������˹��ģ�ͬ�r(sh��)������������һ�������w������DDR5 ��(d��ng)ǰ�l(f��)���f(xi��)�h������������_(d��) 6.4Gbps����r(sh��)��l��Ҳ�� 1.6GHz ���ӵ��� 3.2GHz��

��(d��ng)�҂�����̽�� DDR5 �ĸ��༚(x��)��(ji��)�r(sh��)���҂�Ҳ�l(f��)�F(xi��n)�@һ�¼��g(sh��)������һЩ�~��ļ��g(sh��)����(zh��n)�����磬DDR5 ���Դ늉����^�� DDR4 �� 1.2V ������ 0.1V���_(d��)���� 1.1V���mȻ�^�͵��Դ늉������˹��IJ����L��늳؉�������ͬ�r(sh��)Ҳ������һЩ���g(sh��)����(zh��n)������������ܵ����ĸɔ_���@ʹ����̖������׃�ø�������(zh��n)�ԣ���?y��n)���̖�_�P(gu��n)�r(sh��)늉�֮�g�����������٣������ܕ����Ӱ푵��O(sh��)Ӌ(j��)��

DDR5 ����һ��(g��)�ش�׃���ǣ��c DDR4 ���Դ����оƬ��PMIC�������������ϵķ�ʽ��ͬ��DDR5 ���Դ���� IC��PMIC�����������D(zhu��n)�Ƶ����p��ֱ��ʽ��(n��i)��ģ�K��DIMM���ϡ��@ʹ���Դ������늉��{(di��o)��(ji��)���������������ϸ��ӽ�ģ�K�ϵĴ惦�������@Ҳ�����ڴ_���Դ�����ԣ�PI����������(qi��ng)�� PMIC �\(y��n)�з�ʽ�Ŀ��ơ�

���⣬�ڔ�(sh��)��(j��)λ����(sh��)���ֲ�׃����r�£�DIMM ��ͨ����(sh��)�� 1 ��(g��)ͨ�����ӵ� 2 ��(g��)ͨ��Ҳ��һ��(g��)��Ҫ���M(j��n)����ͨ�^����(sh��)��(j��)�ֳɃɂ�(g��)�^խ��ͨ����ݔ�����Ը���Ч�����ɺͷ���r(sh��)���̖���Ķ���������̖�����ԡ�

�@Ȼ��DDR5 ��(bi��o)��(zh��n)���_�l(f��)Ҳ���]������̖�����Ԇ��}���� PMIC �D(zhu��n)�Ƶ�ģ�K��Ҳ���l(f��)�]����(y��ng)�ă�(y��u)�ݡ�Ȼ�����O(sh��)Ӌ(j��)�ˆT��Ȼ��Ҫ���]����ԴӰ푵���̖�����Ե����wЧ��(y��ng)��������������DDR5 ���и��_(d��) 6.4Gbps �Ĕ�(sh��)��(j��)���ʺ� 3.2GHz ϵ�y(t��ng)�r(sh��)��l�ʣ��Դ�����@�N���ٲ����п��ܕ����l(f��)�����@�Ć��}����ϵ�y(t��ng)���ܺͷ�(w��n)�������Ӱ푡�����քe�M(j��n)���Դ�����Ժ���̖�����Է������Ϳ��ܕ��z©�Դ������Ć��}��

��ˣ�Ҫ���ְl(f��)�] DDR5 �����ܣ������ϵ�y(t��ng)�������P(gu��n)�I�c(di��n)����оƬ�����b�� PCB �M(j��n)�м���ԴӰ푵���̖�����Է��������ǣ��M(j��n)���@�N����ķ�����һ�(xi��ng)��(f��)�s���΄�(w��)��������Ӌ(j��)��ƽ�_�����ڷ��������Ӳ����ܛ�����߶��кܸߵ�Ҫ��Ҳ��ʹ�ÿ��w���O(sh��)Ӌ(j��)�r(sh��)�g׃�ø��L���������O(sh��)Ӌ(j��)���y�Ⱥ͏�(f��)�s�ԡ�

���ጷ� DDR5 �ĝ�����Cadence ����Ӌ(j��)

���� 2005 �꣬������ԴӰ푡��@һ�����״����࣬����һ�N�܉�ͬ�r(sh��)������̖�c�Դ�������M(j��n)��̖�����Է��淽�����D 1��������ԴӰ푵���̖�����Խ�Q������횿��]���䡢��?d��ng)_���r(sh��)�������Ч��(y��ng)�����������(y��ng)�ķ����Ҏ(gu��)�t�z�鼼�g(sh��)��ֵ��ע����ǣ�Ҫ����Ч�،�(sh��)ʩ����ԴӰ푵���̖�����Է��棬��Ҫ��Ҏ(gu��)�t�z��Ͳ�����ķ����A���M(j��n)�У���?y��n)�ƽ�����̖������?��ϰl(f��)���ڲ������֮��

��ˣ�һ��(g��)�����ļ���ԴӰ푵Ľ�Q����������Ҫ�ṩ��

l һ��ᘌ���̖˥�p���Դ����̖��Ӱ푵Ŀ��ٙz�鷽��

l �܉�ģ�M�����·�ĕr(sh��)�������������(g��)��̖�W(w��ng)�j(lu��)���Դ�W(w��ng)�j(lu��)�ĽY(ji��)����

l �Դ�W(w��ng)�j(lu��)����̖�W(w��ng)�j(lu��)�Ľ�ģ

l ��ݔ��/ݔ����I/O�����_����ģ

�D 1������ԴӰ푵���̖�����Է���Y(ji��)��

�M���Ј��ϵ��S��߶�֧�ֻ����ļ���ԴӰ푵� I/O ��ģ��(bi��o)��(zh��n)�����^���S����(n��i)��ӿڼ��g(sh��)�IJ���l(f��)չ���Ј�����̖�����Թ��ߵ�Ҫ��Ҳ�����(y��n)���܌�(sh��)�F(xi��n)��оƬ�����b�� PCB �ϵ������̖���Դ�ͽӵ���̖�Ĝ�(zh��n)�_��ȡ�Ĺ��߅s���Pë��ǡ�

���@���棬��������O(sh��)Ӌ(j��)�Ԅ�(d��ng)����EDA�������I(l��ng)����I(l��ng)܊��I(y��)��Cadence �Ƴ��� Sigrity X ���g(sh��)�t��ᘌ� DDR4 �� DDR5 �ṩ�������ļ���ԴӰ푵���̖�����Է�����

Sigrity X ���g(sh��)���H��(sh��)�F(xi��n)��оƬ�����b�� PCB �ϵ������̖���Դ�ͽӵ���̖�ľ��_��ȡ��߀��ͬ�r(sh��)ᘌ����䡢�p�ġ���?d��ng)_��ͬ���_�P(gu��n)ݔ����SSO��Ч��(y��ng)�M(j��n)�и�Ч���档���� Sigrity ���g(sh��)���O(sh��)Ӌ(j��)�ˆT��Ѹ�ٌ����w�ܼ�ģ���D(zhu��n)�Q�鿼�]�ԴӰ푵��О鼉 IBIS ģ�ͣ��Ķ��ڎׂ�(g��)С�r(sh��)֮��(n��i)�����ṩ����(zh��n)����Ч��ȫ�濼�]�ԴӰ푵ķ��棬���s����ԭ����Ҫ��(sh��)����O(sh��)Ӌ(j��)���ڡ����D 2��

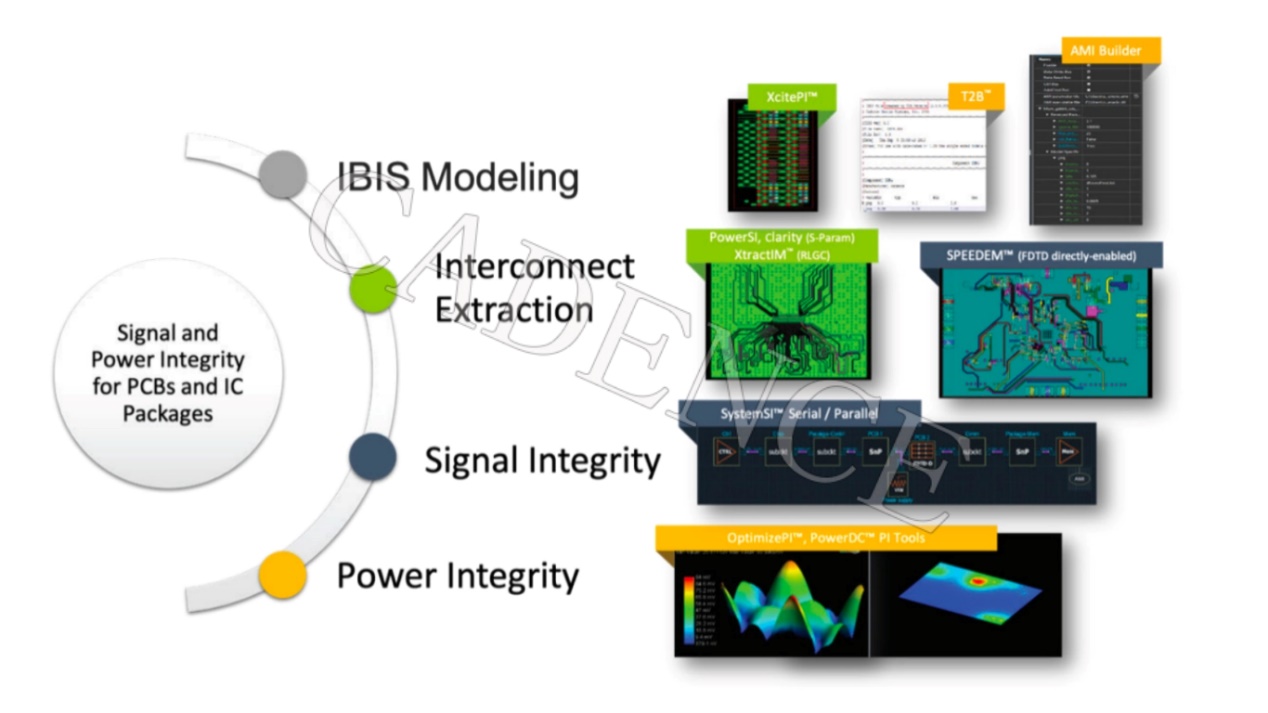

�D 2������ PCB �� IC ���b�� Cadence ��̖�����Ժ��Դ�����Թ���

Sigrity X ���g(sh��)�����˹������̣��ṩ�O(sh��)Ӌ(j��)ͬ�����ٷ����������K�(y��n)�C�ĺ��˼���(zh��n)�_�ȡ���̖�����ʺ͟ᆖ�}������ÿ��(g��)�O(sh��)Ӌ(j��)�A�����Խ�Q���Ķ��������O(sh��)Ӌ(j��)�ͷ����F(tu��n)�(du��)�g�ĵ����Δ�(sh��)���O(sh��)Ӌ(j��)�ˆT�������O(sh��)Ӌ(j��)������(n��i)�\(y��n)�к��˼�������M(j��n)�и߾��ȵķ��棬�Ķ��ṩ���|(zh��)�����O(sh��)Ӌ(j��)���������F(tu��n)�(du��)�M(j��n)���(y��n)�C��֮�����F(tu��n)�(du��)���� Sigrity ��Ҏ(gu��)ģ���з��������M(j��n)��ȫϵ�y(t��ng)���棬�_������(g��)��оƬ-���b-PCB-�⚤�������O(sh��)Ӌ(j��)Ҏ(gu��)�������麞�����Ü�(zh��n)�䡣

�@Щ��(y��u)��ʹ�� Sigrity X �ɞ� DDR5 ��(n��i)��� 112G �ӿڵ���ѽ�Q���������S���(bi��o)��(zh��n)�Ļ��B��ģ���Y(ji��)���˴�����/�����SerDes��������֧�� IBIS �㷨��ģ�ӿڣ�AMI���ĕr(sh��)����棨�·��ͨ�����棩���x�� Cadence ��(d��)һ�o���ă�(y��u)�ݣ��Ķ�����ȡ�ͽӿں�Ҏ(gu��)�Ժ����ṩ�����Ľ�Q������

�M(j��n)һ���ģ�Sigrity XtractIM �� Clarity 3D Solver ���g(sh��)�������ʹ�ã��@���̎����܉�ᘌ����N��͵ķ��b��(chu��ng)�������������̖���Դ�ͽӵػ��Bģ�͵��������bģ�ͣ���Ч���a(b��)�˷��b�O(sh��)Ӌ(j��)�ͷ��b����֮�g�IJ�ࡣ

���⣬Sigrity SystemSI ���g(sh��)֧�ֿ����B�Ӽ���ԴӰ푵� IBIS ģ�ͺͼ���ԴӰ푵Ļ��Bģ�ͣ��O(sh��)Ӌ(j��)�ˆTͨ�^�@һ���g(sh��)������Ѹ�ٴ_������ĵ���r���c JEDEC ��(bi��o)��(zh��n)�M(j��n)�бȌ����_�� DDR4/DDR5 �ӿڣ����������`�a��Ҫ�����������P(gu��n)Ҏ(gu��)����

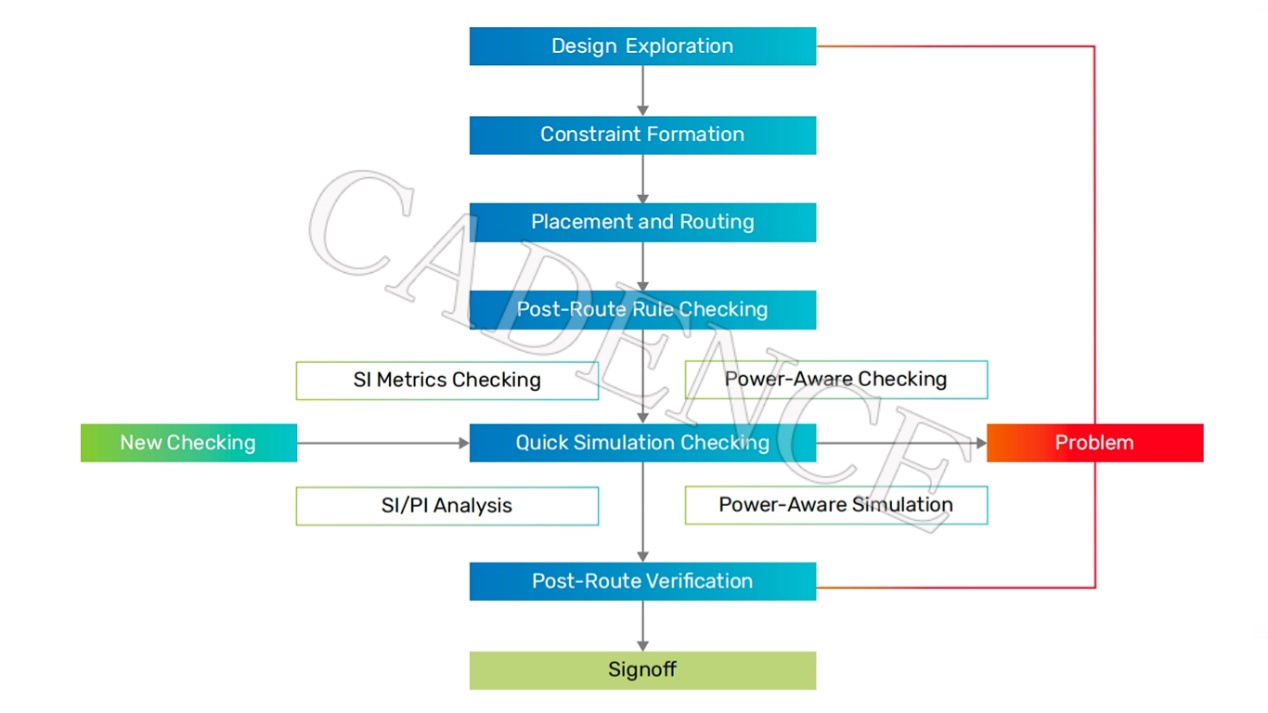

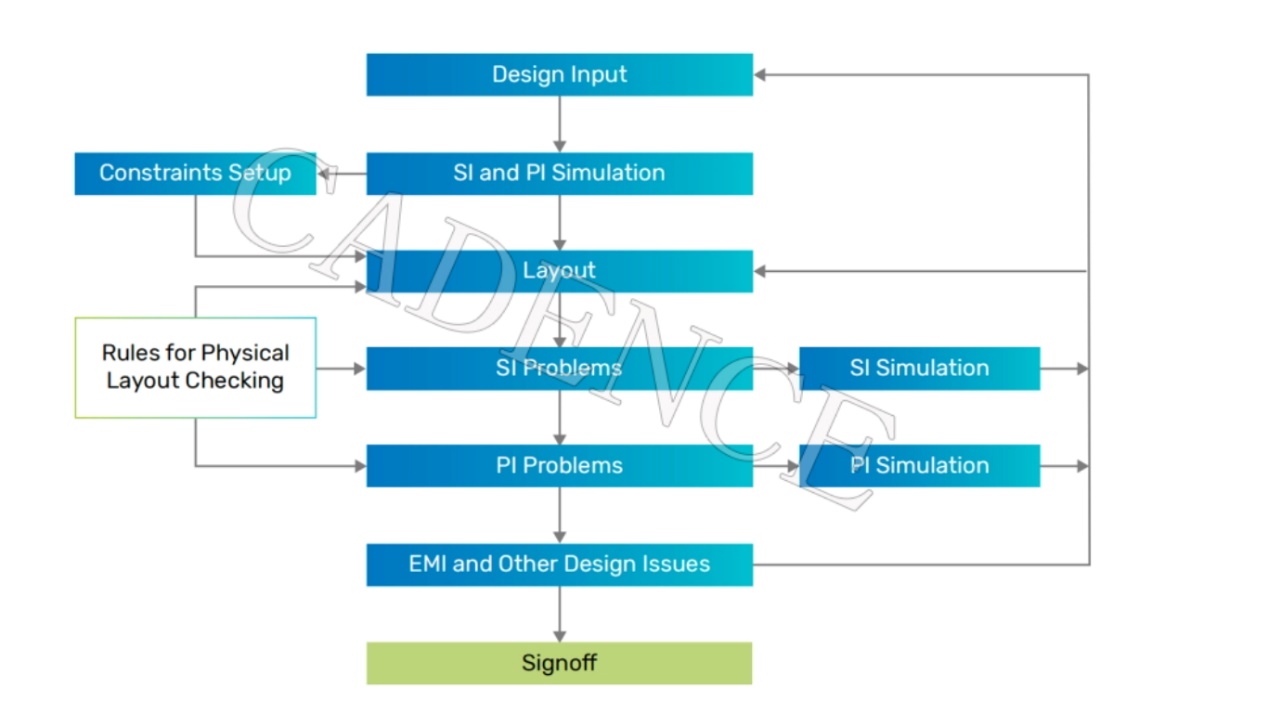

�D 3 �� Cadence ����ԴӰ푵ęz��ͷ������̣��@�c���y(t��ng)�ļs���(q��)��(d��ng)���O(sh��)Ӌ(j��)���̣��D 4���γ����r�����ȡ����y(t��ng)�ļs���(q��)��(d��ng)���O(sh��)Ӌ(j��)������Ҫ�����Ă�(g��)���֣��A(y��)���ֲ������s���γɡ�Ҏ(gu��)�t�z��Ͳ������(y��n)�C��

�D 3��Cadence ����ԴӰ푵ļs���(q��)��(d��ng)������

VS

�D 4�����y(t��ng)�ļs���(q��)��(d��ng)���O(sh��)Ӌ(j��)����ʾ��

��(d��ng)ǰ�ı���F(xi��n)�з��漼�g(sh��)�У���̖�������Դ�ֲ��W(w��ng)�j(lu��)��PDN��֮�g��������Ó��(ji��)��Ҳ������һЩ����ȱ�c(di��n)��ͨ����r�£�����(j��) SPICE ģ�͵ď�(f��)�s�Բ�ͬ���Еr(sh��)��ʹ�Õr(sh��)���������ɜ�(zh��n)�_�����/늸�/��ݣ�RLC��ģ�ͣ����Еr(sh��)�t�����O(sh��)һ��(g��)����Ľӵ�ƽ�档�ɴ˵ó��ĕr(sh��)��ģ���ǻ��ڷ�����ȡ�ĺ����l��푑�(y��ng)���mȻ�^���ݣ������ڜ�(zh��n)�_�Է������в��㣬�����ڸ��ߵ��l�ʣ����̎���ʹ��ͨ�^����������(chu��ng)���� S ����(sh��)��

�䌍(sh��)߀��һ�N��Ч�ķ�������������֕r(sh��)��FDTD�������c����������Y(ji��)�ϣ��Ķ������w�����U(ku��)����̖���Դ�ͽӵؾ���

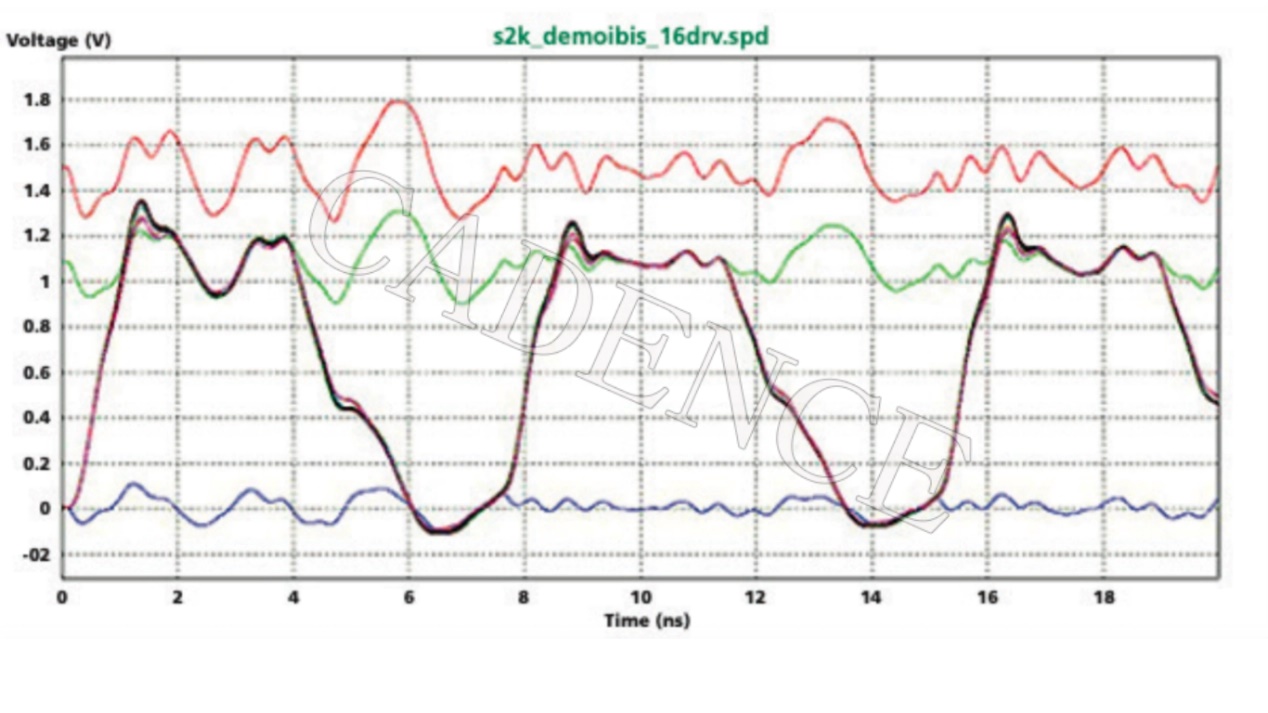

�@һ�����ijɹ���(sh��)�`������ Cadence �� Sigrity SPEED2000 ���湤�ߣ������ɺ����������ɂ�(g��)�������ݔ�����Դ˽�Q�·�����Լ���ݔ����늴ň����}���ܸ��õ�չʾ��(sh��)��(j��)���Դ/�ӵ�ƽ��֮�g�ڲ�ͬ�r(sh��)�g������á���ʹ�� FDTD ���������� IC ���b�� PCB �IJ��֡����·�O(sh��)Ӌ(j��)���M(j��n)һ����(y��u)���ṩ����Ҫ�ą�������(j��)��

��(d��ng)�M(j��n)�뵽��K�ĺ����A�Σ����̎�ͨ���A����ʹ�� 3D ȫ����ģ�����ԫ@�ø��ߵĜ�(zh��n)�_�ȡ����@�����ĸ����Ӌ(j��)���YԴ�������ӷ���ĕr(sh��)�g�����˾����@��(g��)���}�����Բ��÷ָ�Ͳ��л����g(sh��)�����@���棬ͨ�^ʹ�� Clarity 3D Solver �M(j��n)�л�������Ԫ������FEM��������Ȼ���ٽY(ji��)�� Sigrity XtractIM ���g(sh��)����K������(g��)�����Y(ji��)�������½M�ϣ��γ�һ��(g��)�����l��푑�(y��ng)�� S ����(sh��)ģ�ͣ��Ķ���(sh��)�F(xi��n)������(g��)ϵ�y(t��ng)���O(sh��)Ӌ(j��)������;��_������

���Y(ji��)

�Ƽ���ÿһ���w�S���ڎ������g(sh��)������ͬ�r(sh��)��Ҳ���ɱ���؞��O(sh��)Ӌ(j��)���������µ�����(zh��n)�����~�� DDR5 ��(n��i)����r(sh��)����������(zh��n)��·�ϣ����� Cadence Sigrity X �@���J���ġ����С����֣����̎�������̹Ȼ��(y��ng)����̖�����Եĸ��N��(f��)�s���}���_���a(ch��n)Ʒ���H�cҎ(gu��)����������������ϴ�Ů��ʣ���δ�턓(chu��ng)��֮·����һ�u��

�ߴa�P(gu��n)ע�҂�

�]�䣺ivy@yingtexin.net

��ַ�����������A�^(q��)���νֵ����δ��973�f�����S��(chu��ng)�I(y��)�@A��2��A09